Gerd Wöstenkühler

# Grundlagen der Digitaltechnik

Elementare Komponenten,

Funktionen und Steuerungen

Wöstenkühler

Grundlagen der Digitaltechnik

Bleiben Sie einfach auf dem Laufenden:

[www.hanser.de/newsletter](http://www.hanser.de/newsletter)

Sofort anmelden und Monat für Monat

die neuesten Infos und Updates erhalten

Gerd Wöstenkühler

# Grundlagen der Digitaltechnik

Elementare Komponenten, Funktionen

und Steuerungen

Mit 317 Bildern, 117 Tabellen und 54 Aufgaben mit Lösungen

**Fachbuchverlag Leipzig**

im Carl Hanser Verlag

Prof. Dr.-Ing. Gerd Wöstenkühler lehrt Mess-, Analog- und Digitaltechnik am Fachbereich Automatisierung und Informatik der Hochschule Harz.

Alle in diesem Buch enthaltenen Programme, Verfahren und elektronischen Schaltungen wurden nach bestem Wissen erstellt und mit Sorgfalt getestet. Dennoch sind Fehler nicht ganz auszuschließen. Aus diesem Grund ist das im vorliegenden Buch enthaltene Programm-Material mit keiner Verpflichtung oder Garantie irgendeiner Art verbunden. Autor und Verlag übernehmen infolgedessen keine Verantwortung und werden keine daraus folgende oder sonstige Haftung übernehmen, die auf irgendeine Art aus der Benutzung dieses Programm-Materials oder Teilen davon entsteht.

Die Wiedergabe von Gebrauchsnamen, Handelsnamen, Warenbezeichnungen usw. in diesem Werk berechtigt auch ohne besondere Kennzeichnung nicht zu der Annahme, dass solche Namen im Sinne der Warenzeichen- und Markenschutz-Gesetzgebung als frei zu betrachten wären und daher von jedermann benutzt werden dürften.

Bibliografische Information der Deutschen Nationalbibliothek

Die Deutsche Nationalbibliothek verzeichnet diese Publikation in der Deutschen Nationalbibliografie; detaillierte bibliografische Daten sind im Internet über <http://dnb.d-nb.de> abrufbar.

ISBN: 978-3-446-42737-2

E-Book-ISBN: 978-3-446-42952-9

Dieses Werk ist urheberrechtlich geschützt.

Alle Rechte, auch die der Übersetzung, des Nachdruckes und der Vervielfältigung des Buches, oder Teilen daraus, vorbehalten. Kein Teil des Werkes darf ohne schriftliche Genehmigung des Verlages in irgendeiner Form (Fotokopie, Mikrofilm oder ein anderes Verfahren), auch nicht für Zwecke der Unterrichtsgestaltung – mit Ausnahme der in den §§ 53, 54 URG genannten Sonderfälle –, reproduziert oder unter Verwendung elektronischer Systeme verarbeitet, vervielfältigt oder verbreitet werden.

© 2012 Carl Hanser Verlag München

Internet: <http://www.hanser.de>

Lektorat: Dr. Martin Feuchte

Herstellung: Dipl.-Ing. Franziska Kaufmann

Satz: le-tex publishing services GmbH, Leipzig

Coverconcept: Marc Müller-Bremer, [www.rebranding.de](http://www.rebranding.de), München

Coverrealisierung: Stephan Rönigk

Druck und Bindung: Friedrich Pustet KG, Regensburg

Printed in Germany

# Vorwort

Unsere Welt wird in zunehmendem Maße digitalisiert. Moderne Verfahren ermöglichen den Einsatz immer komplexerer Bausteine. Hiermit können vorhandene Realisierungen preiswerter erstellt, mit zusätzlichen Funktionen ausgestattet und/oder durch digitale Steuerungen ersetzt werden. Die Werkzeuge zur Erstellung dieser digitalen Funktionen und Steuerungen verwenden immer häufiger Abstraktionen. Die Kenntnisse der elementaren Grundschaltungen ermöglichen eine effektivere Nutzung der eingesetzten Tools.

Dieses Buch vermittelt die Grundlagen digitaler Funktionen und Steuerungen. Es ist nicht das Ziel, komplexe Entwurfswerkzeuge durch manuelle Synthese zu ersetzen, sondern die Kenntnisse über elementare Komponenten und Strukturen zu vermitteln, mit denen moderne Entwurfswerkzeuge effizienter eingesetzt werden können.

Die Inhalte des Buches basieren auf dem Lehrplan der Grundlagen-Vorlesungen „Digitaltechnik“ und „Digitale Systeme“, die ich seit vielen Jahren an der Hochschule Harz in Wernigerode halte. Zielgruppe sind Studierende elektrotechnischer Bachelor-Studiengänge, aber auch interessierte Studierende anderer technischer Ausbildungsrichtungen. Das Verständnis digitaler Grundlagen wird durch eine schrittweise Vertiefung und umfangreiche Übungsmöglichkeiten vermittelt. Das Buch eignet sich neben der Vorlesungsbegleitung auch zur Prüfungsvorbereitung und zum Selbststudium.

Mein Dank geht an die Mitarbeiter des Hanser Verlages, Frau Mirja Werner, die dieses Werk initiiert hat, Herrn Dr. Martin Feuchte für die Betreuung während der Abschlussphase und Frau Franziska Kaufmann für die technische Realisierung. Auch bedanke ich mich bei meiner Frau für die Unterstützung bei der Korrektur des Manuskripts und ihr Verständnis, dass ich viel Zeit in dieses Buch investiert habe.

Paderborn, Januar 2012

Gerd Wöstenkühler

# Inhalt

|          |                                               |           |

|----------|-----------------------------------------------|-----------|

| <b>1</b> | <b>Einleitung</b>                             | <b>11</b> |

| 1.1      | Analoge und digitale Darstellungsformen       | 11        |

| 1.1.1    | Analoge Größendarstellung                     | 11        |

| 1.1.2    | Digitale Größendarstellung                    | 12        |

| 1.2      | Binäre und logische Zustände                  | 13        |

| 1.3      | Zahlensysteme                                 | 14        |

| 1.3.1    | Zahlendarstellungen                           | 14        |

| 1.4      | Codierungen                                   | 17        |

| 1.4.1    | Binär Codierte Dezimalziffer                  | 17        |

| 1.4.2    | Gray-Code                                     | 18        |

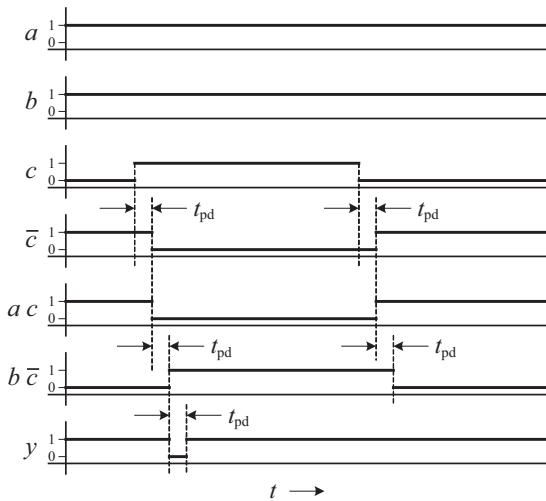

| 1.5      | Verarbeitungsgeschwindigkeit                  | 20        |

| <b>2</b> | <b>Logische Verknüpfungen</b>                 | <b>21</b> |

| 2.1      | Grundfunktionen und Grundglieder              | 21        |

| 2.1.1    | UND-Verknüpfung                               | 21        |

| 2.1.2    | ODER-Verknüpfung                              | 23        |

| 2.1.3    | NEGATION                                      | 24        |

| 2.1.4    | Verstärker                                    | 25        |

| 2.2      | Zusammengesetzte Elemente                     | 26        |

| 2.2.1    | NAND-Verknüpfung                              | 26        |

| 2.2.2    | NOR-Verknüpfung                               | 26        |

| 2.2.3    | ANTIVALENZ-Verknüpfung                        | 27        |

| 2.2.4    | ÄQUIVALENZ-Verknüpfung                        | 29        |

| 2.2.5    | Implikation                                   | 29        |

| 2.2.6    | Inhibition                                    | 30        |

| 2.2.7    | Verknüpfungen bei Gliedern mit zwei Eingängen | 30        |

| 2.2.8    | Wichtige Glieder mit mehr als zwei Eingängen  | 32        |

| 2.3      | Schaltungsanalyse                             | 33        |

| 2.4      | Aufgaben                                      | 34        |

|          |                                           |           |

|----------|-------------------------------------------|-----------|

| <b>3</b> | <b>Schaltalgebra</b>                      | <b>36</b> |

| 3.1      | Variable und Konstante                    | 36        |

| 3.2      | Rechenregeln                              | 37        |

| 3.2.1    | Postulate                                 | 37        |

| 3.2.2    | Theoreme der Schaltalgebra                | 38        |

| 3.2.3    | Kommutativgesetz                          | 39        |

| 3.2.4    | Assoziativgesetz                          | 39        |

| 3.2.5    | Distributivgesetz                         | 40        |

| 3.2.6    | De-Morgansche-Gesetze                     | 40        |

| 3.2.7    | Bindungsregel                             | 41        |

| 3.3      | Aufgaben                                  | 42        |

| <b>4</b> | <b>Schaltungssynthese</b>                 | <b>45</b> |

| 4.1      | Normalformen                              | 45        |

| 4.1.1    | Disjunktive Normalform                    | 45        |

| 4.1.2    | Konjunktive Normalform                    | 47        |

| 4.2      | Schaltungsvereinfachung                   | 48        |

| 4.2.1    | Algebraische Vereinfachung                | 48        |

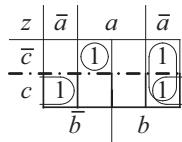

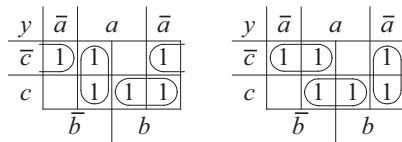

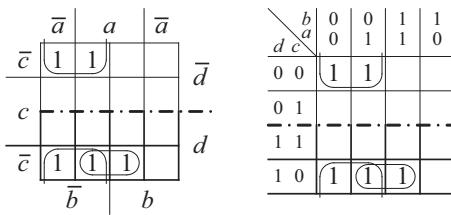

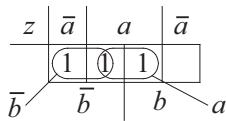

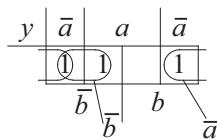

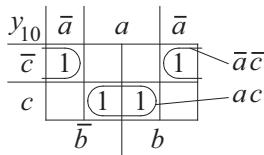

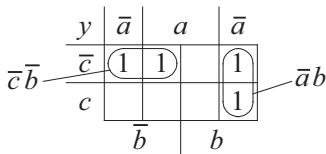

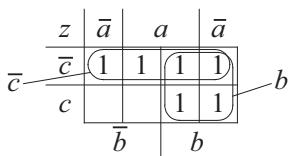

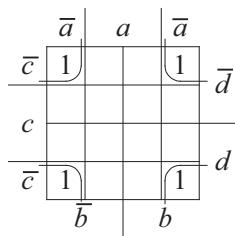

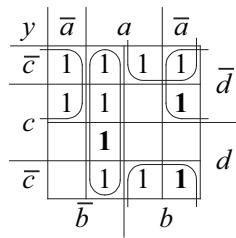

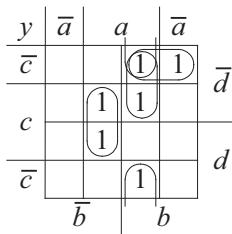

| 4.2.2    | Grafische Vereinfachung                   | 50        |

| 4.2.2.1  | KV-Diagramm mit zwei Variablen            | 50        |

| 4.2.2.2  | KV-Diagramm mit drei Variablen            | 51        |

| 4.2.2.3  | KV-Diagramm mit vier Variablen            | 52        |

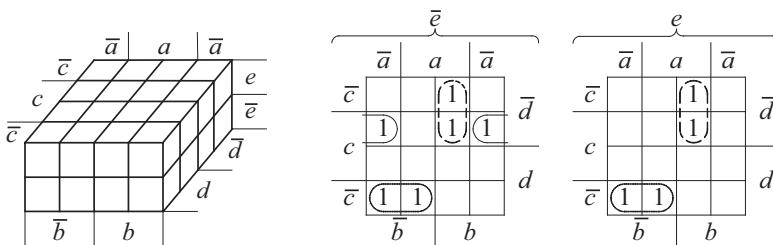

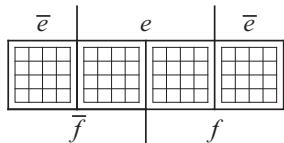

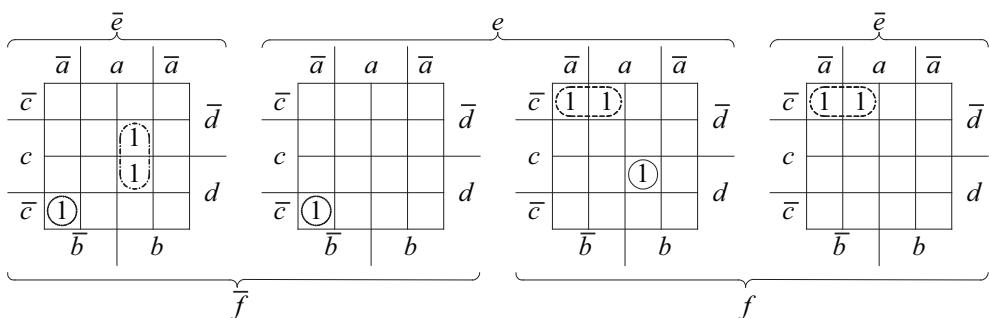

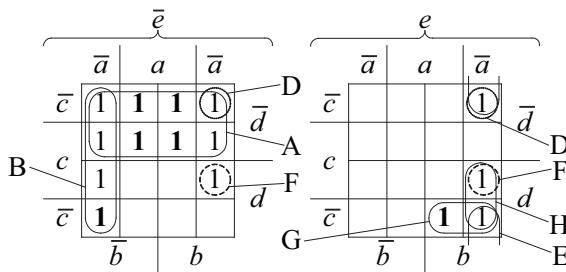

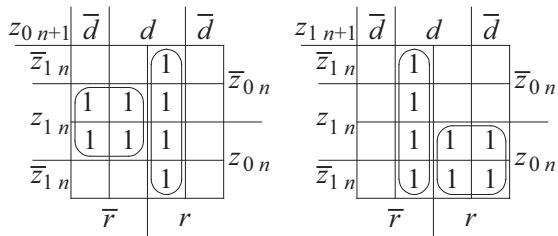

| 4.2.2.4  | KV-Diagramm mit fünf Variablen            | 53        |

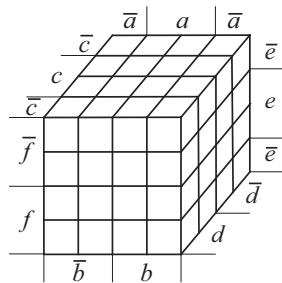

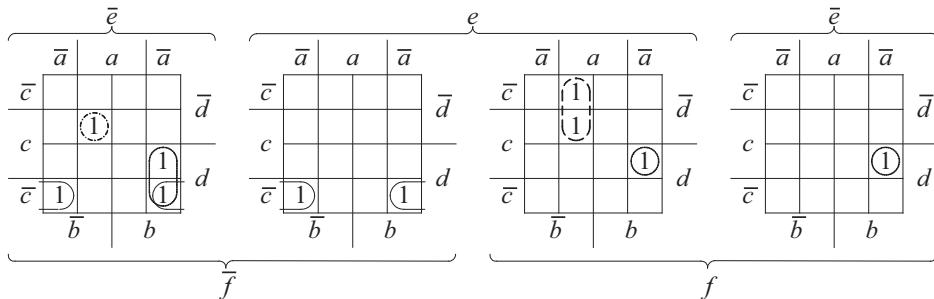

| 4.2.2.5  | KV-Diagramm mit sechs und mehr Variablen  | 54        |

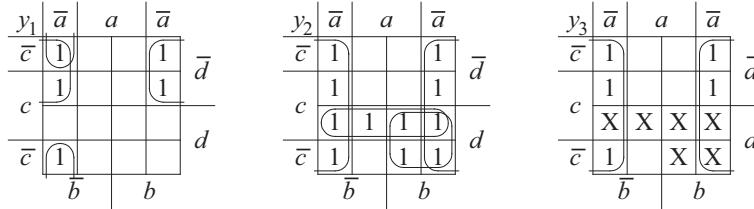

| 4.2.2.6  | Don't-Care-Felder                         | 55        |

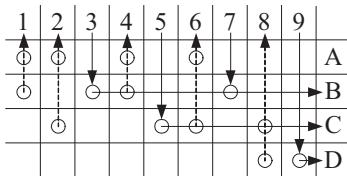

| 4.2.3    | Algorithmische Umformung (Quine-McClusky) | 56        |

| 4.3      | Aufgaben                                  | 59        |

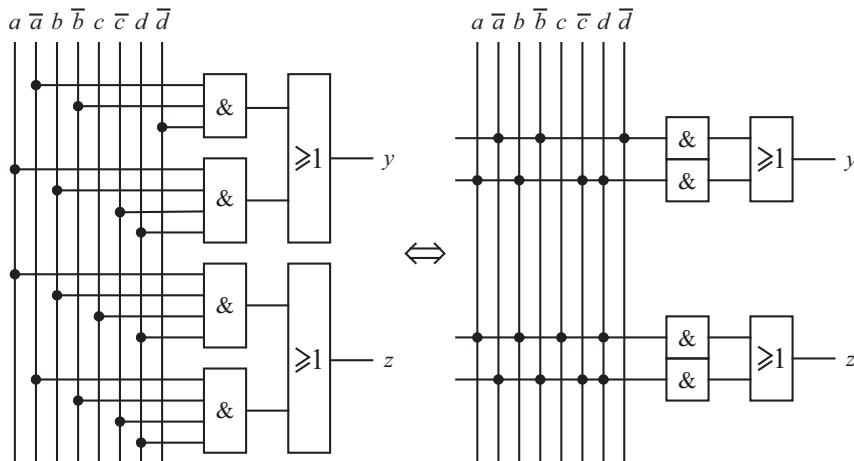

| <b>5</b> | <b>Schaltnetze</b>                        | <b>61</b> |

| 5.1      | Darstellung                               | 62        |

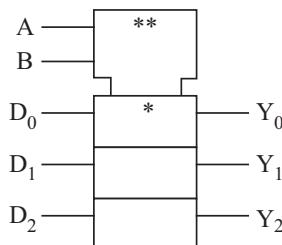

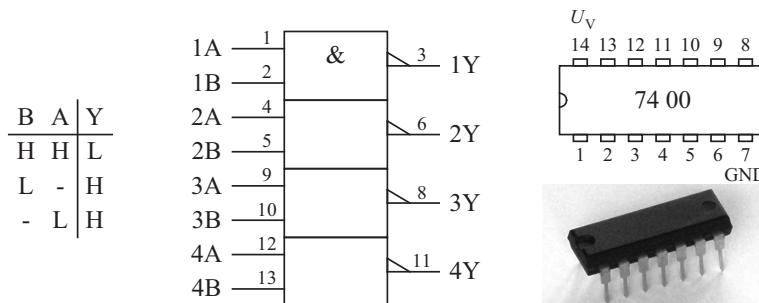

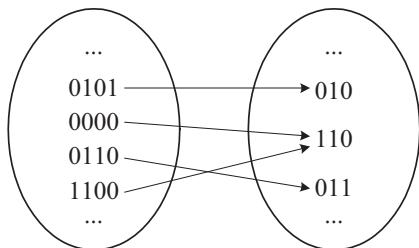

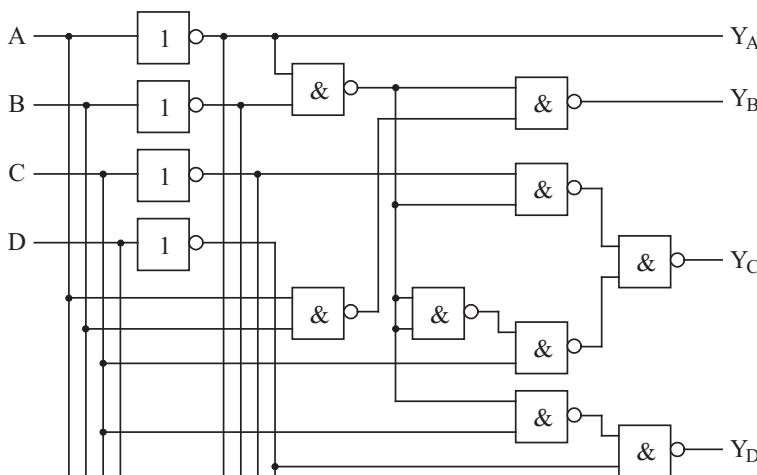

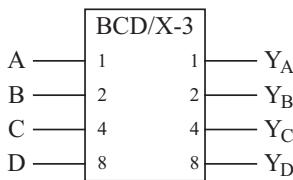

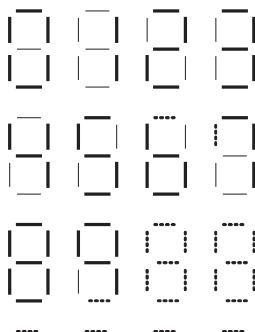

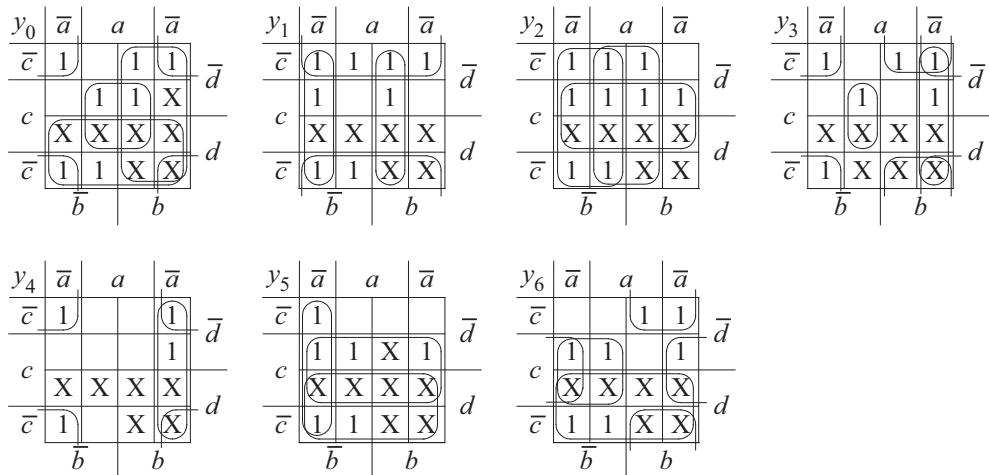

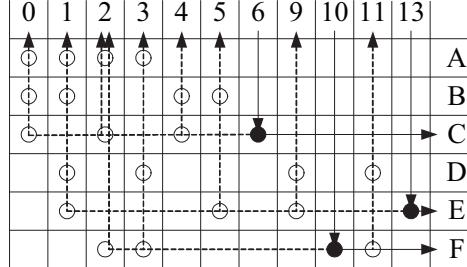

| 5.2      | Codeumsetzer                              | 63        |

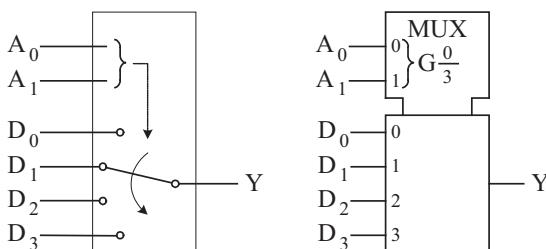

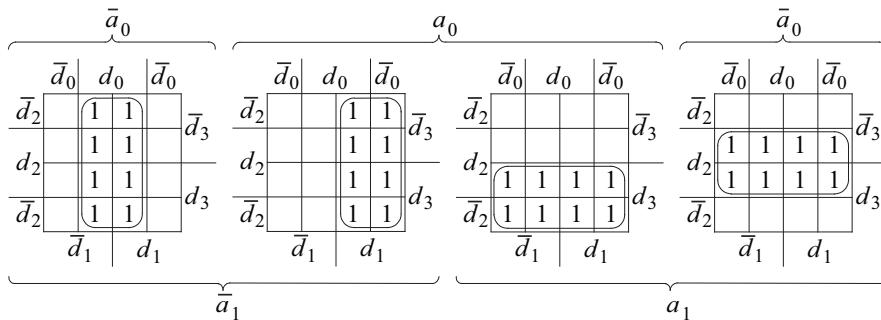

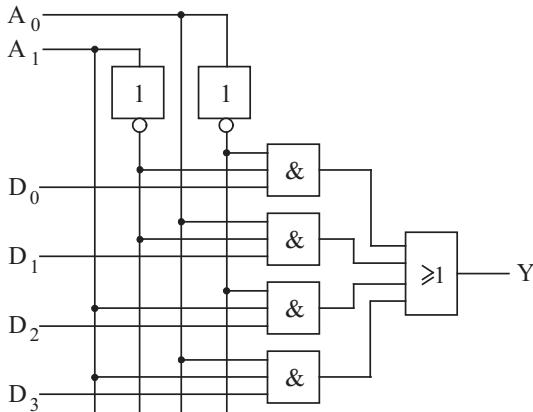

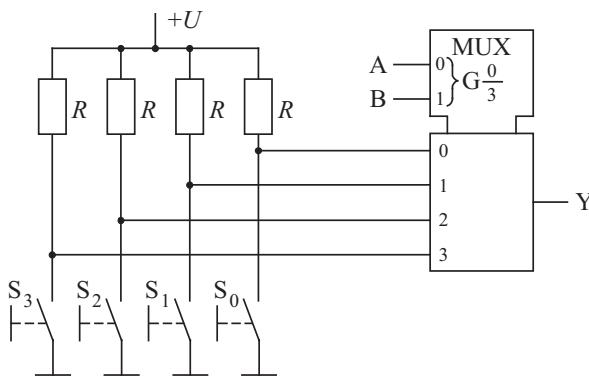

| 5.3      | Datenselektor                             | 65        |

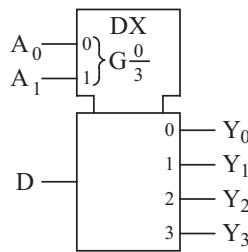

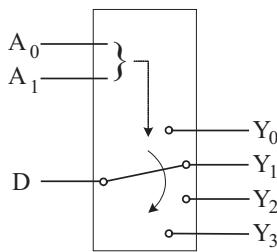

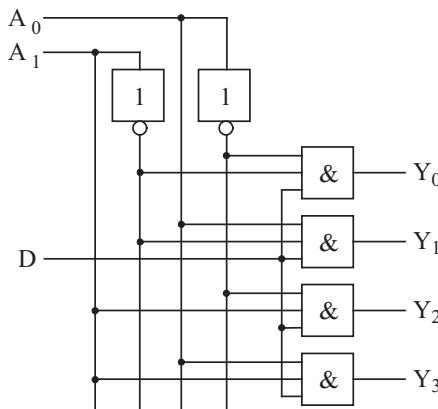

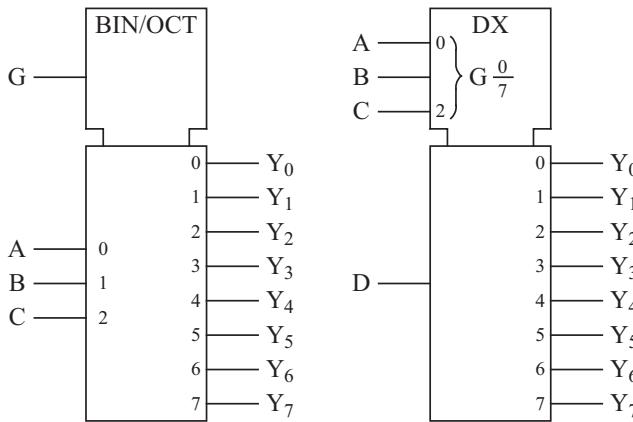

| 5.4      | Demultiplexer                             | 67        |

| 5.5      | Adressdecoder                             | 69        |

| 5.6      | Addierer                                  | 72        |

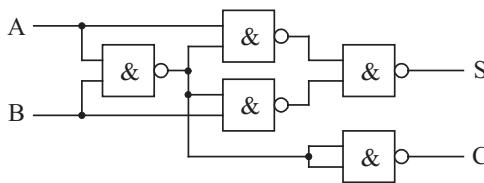

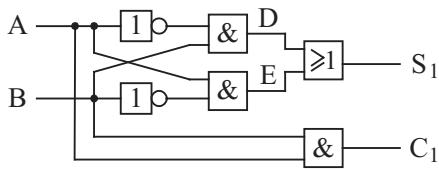

| 5.6.1    | Halbaddierer                              | 72        |

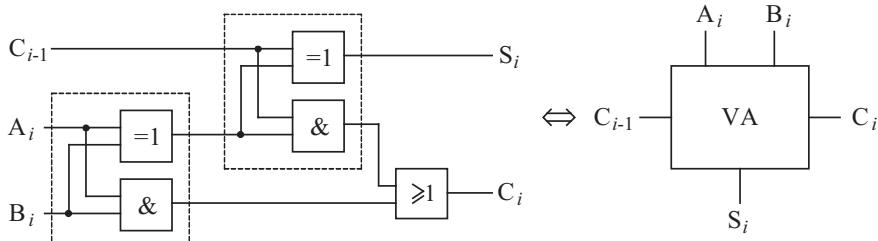

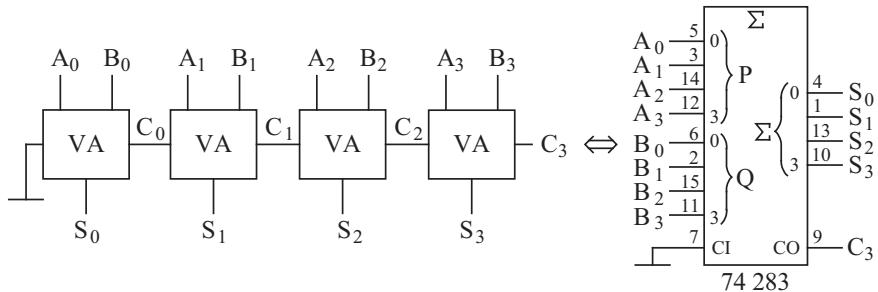

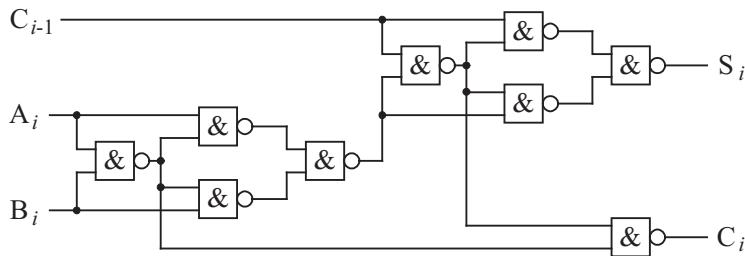

| 5.6.2    | Volladdierer                              | 73        |

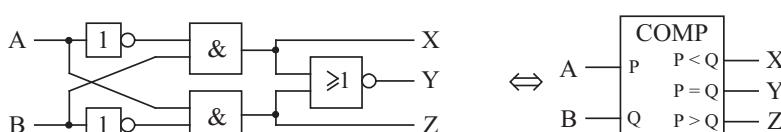

| 5.7      | Komparator                                | 75        |

| 5.8      | Aufgaben                                  | 79        |

---

|          |                                          |            |

|----------|------------------------------------------|------------|

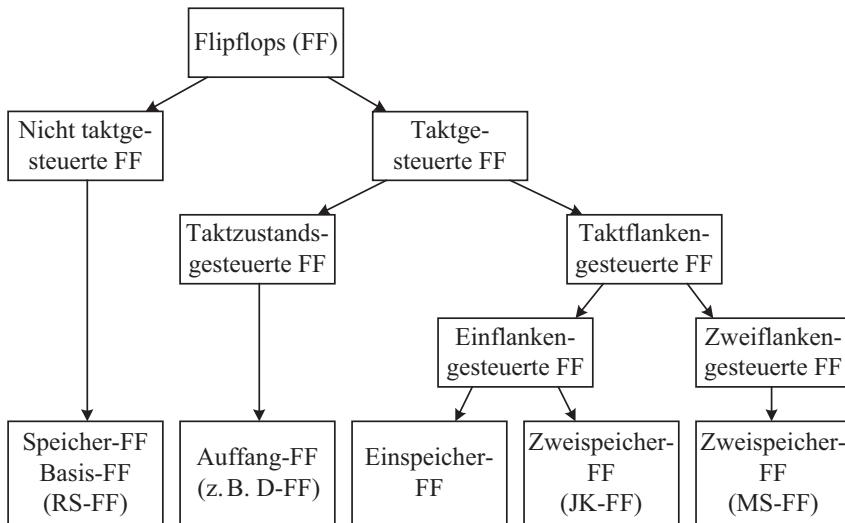

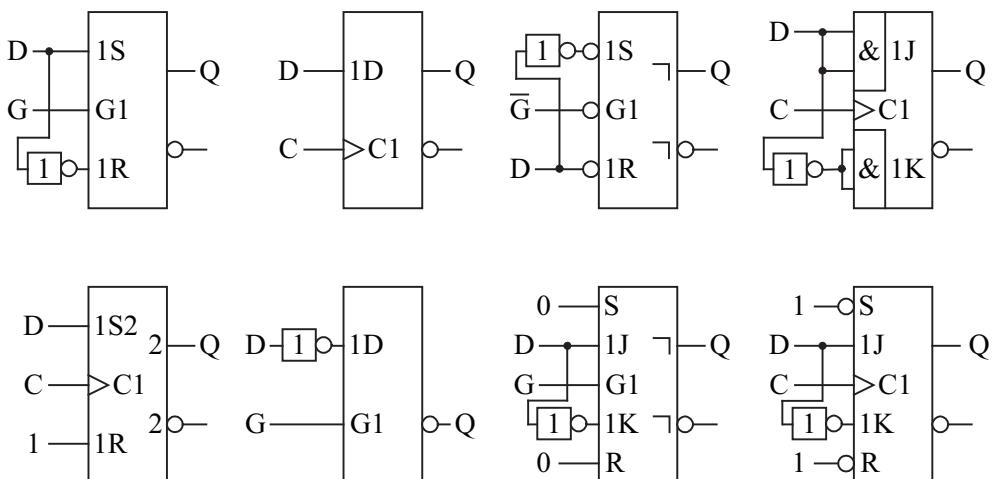

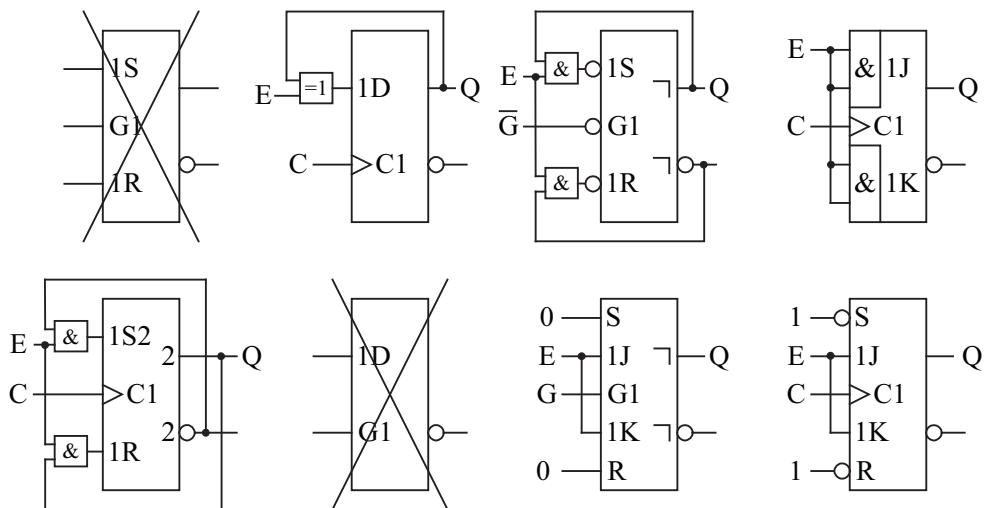

| <b>6</b> | <b>Zeitabhängige binäre Schaltungen</b>  | <b>82</b>  |

| 6.1      | Übersicht                                | 82         |

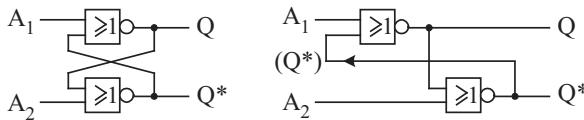

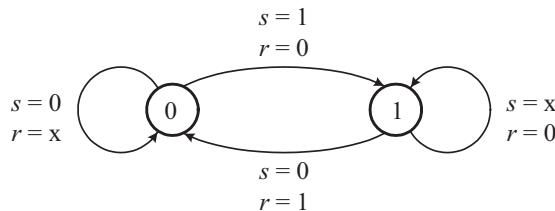

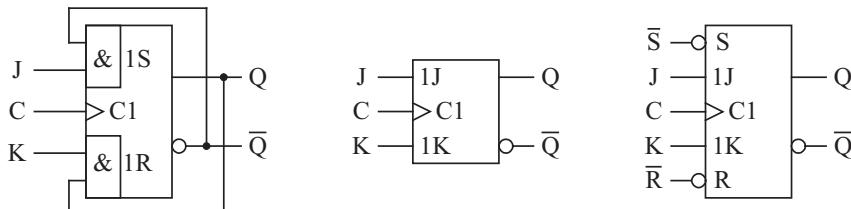

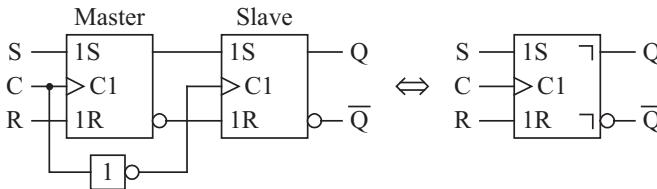

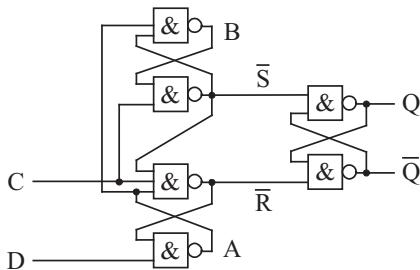

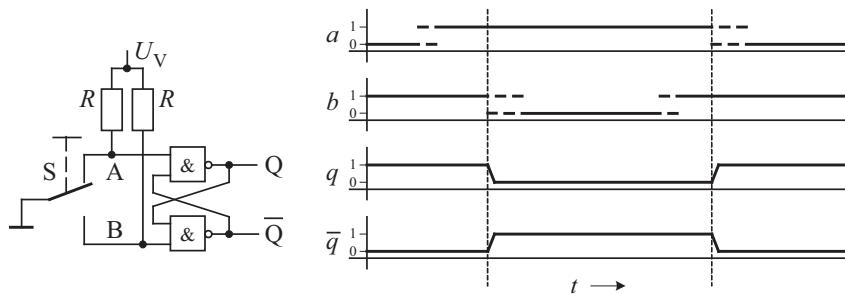

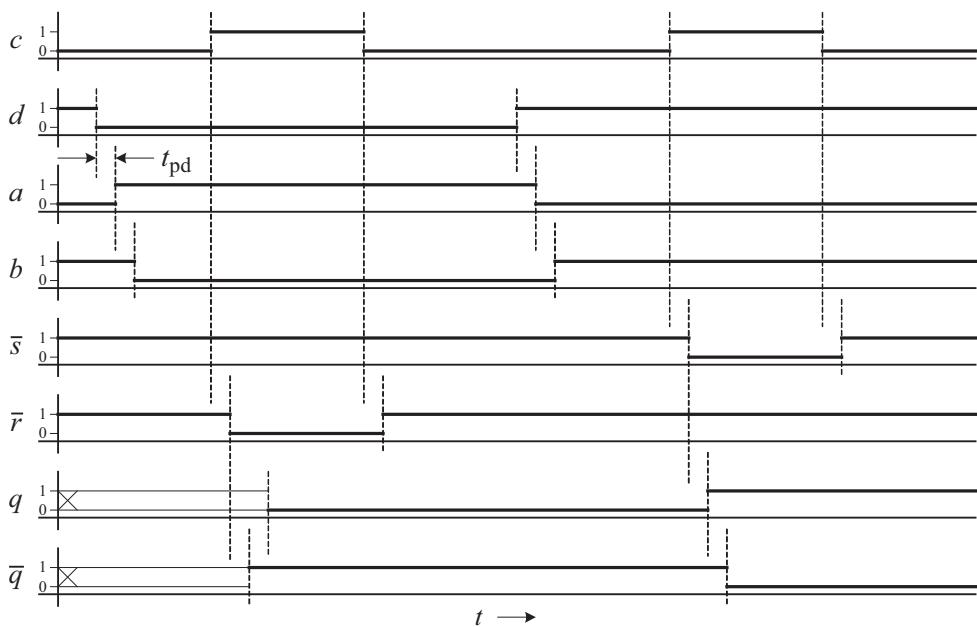

| 6.2      | RS-Flipflop (RS-FF)                      | 86         |

| 6.2.1    | Realisierung mit NOR-Gatter              | 86         |

| 6.2.2    | Realisierung mit NAND-Gatter             | 90         |

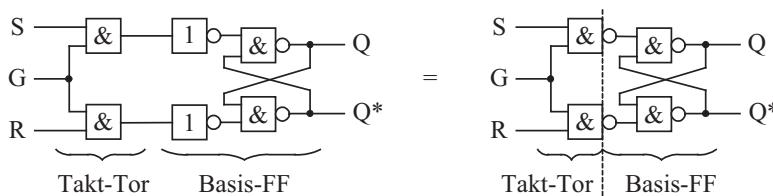

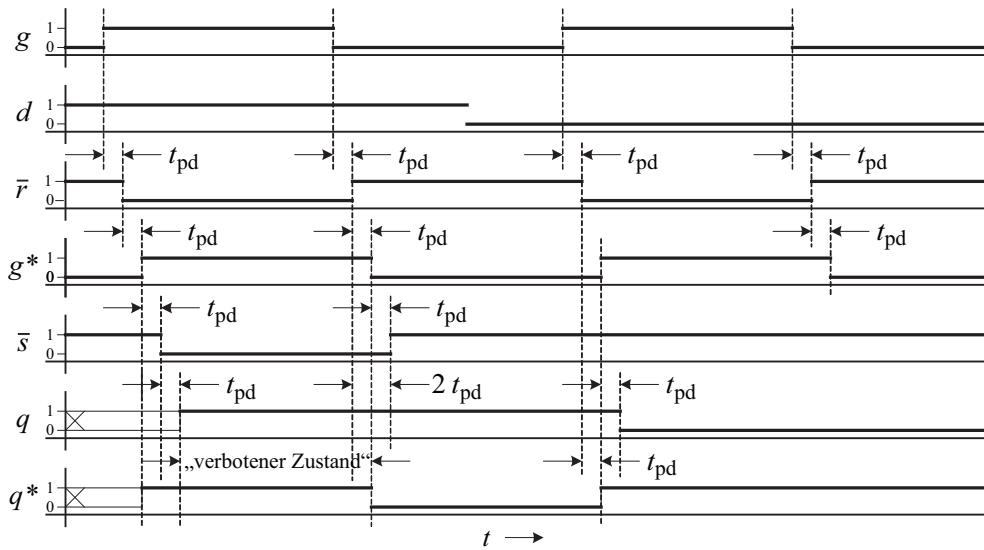

| 6.3      | Taktzustandsgesteuerte Flipflops         | 91         |

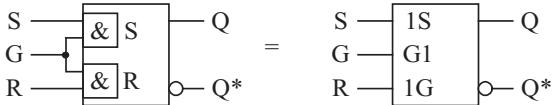

| 6.3.1    | RS-FF (taktzustandsgesteuert)            | 91         |

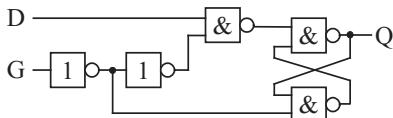

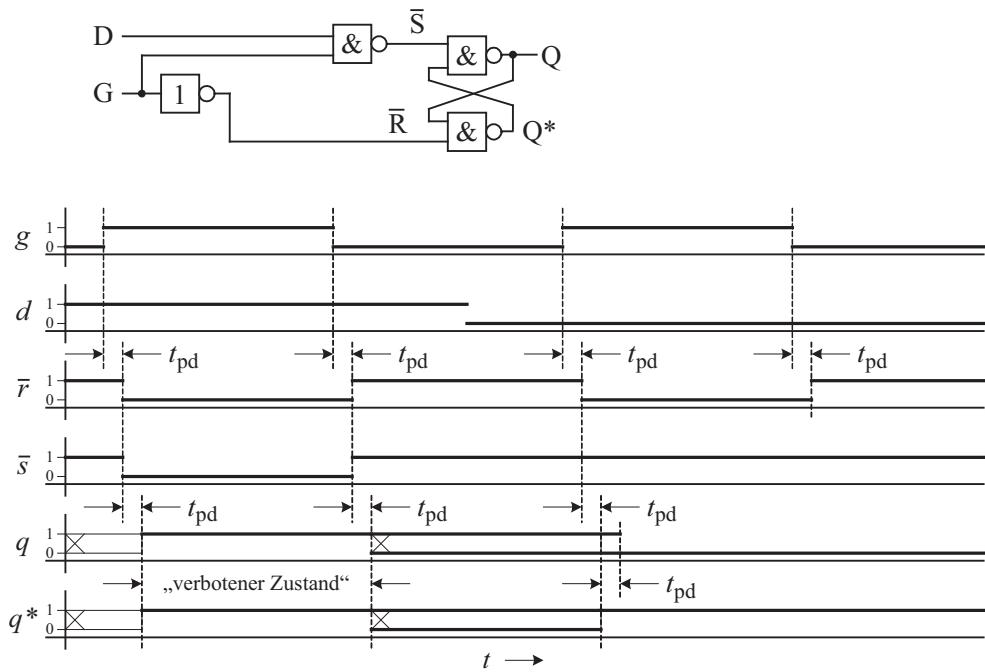

| 6.3.2    | D-FF (taktzustandsgesteuert)             | 94         |

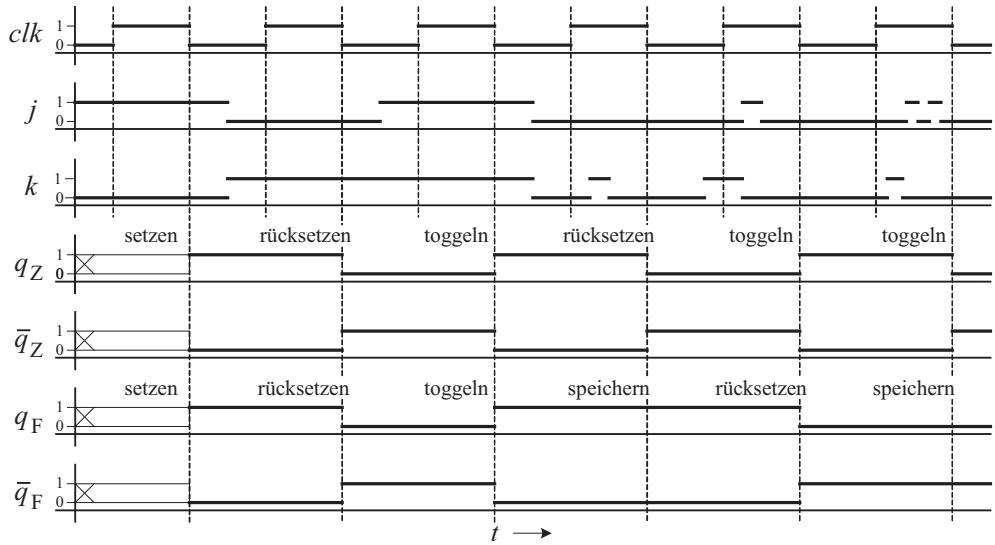

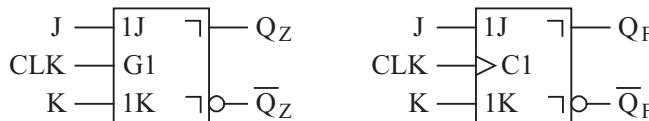

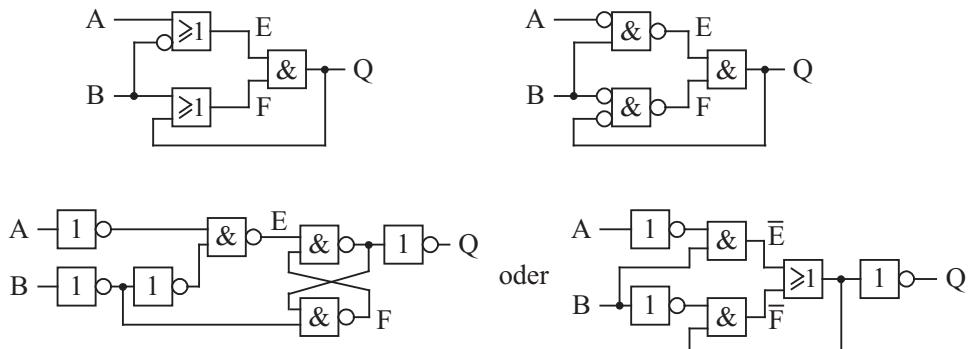

| 6.3.3    | JK-FF (taktzustandsgesteuert)            | 96         |

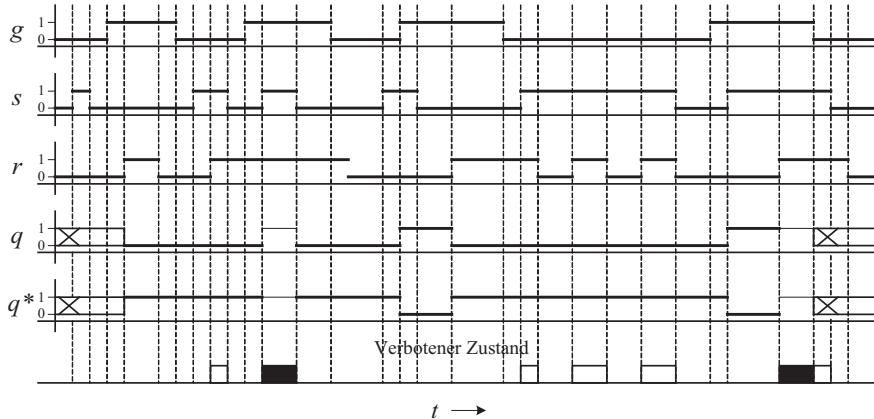

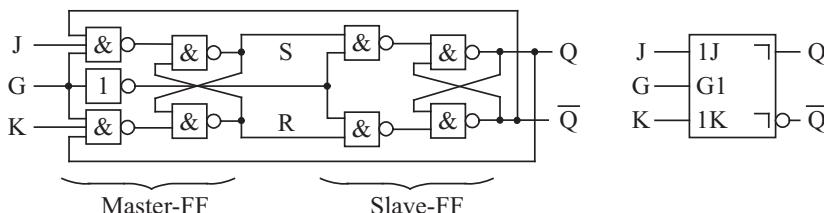

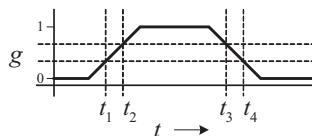

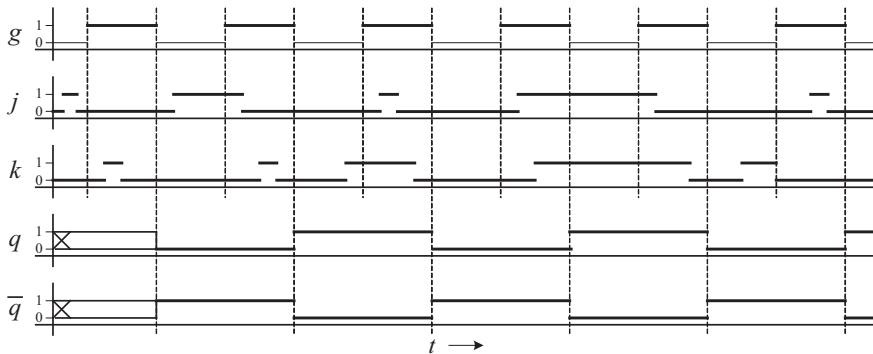

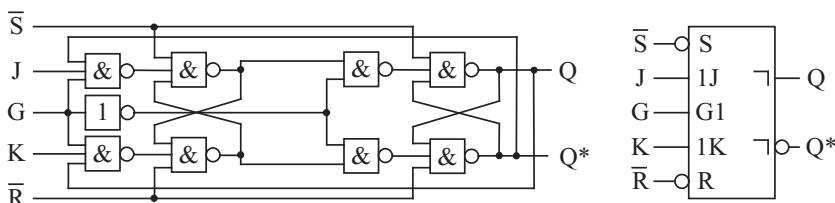

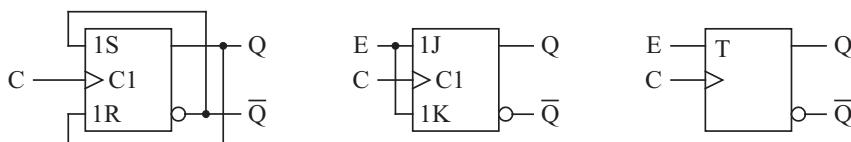

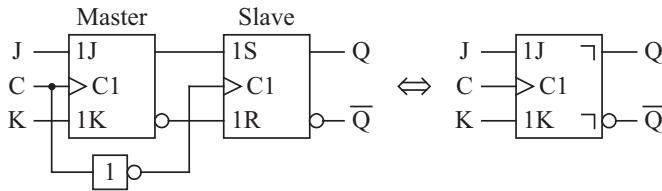

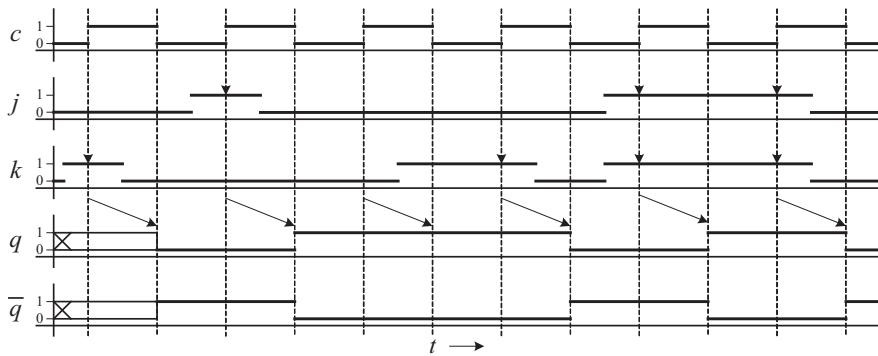

| 6.3.4    | JK-MS-FF (taktzustandsgesteuert)         | 98         |

| 6.4      | Taktflankengesteuerte Flipflops          | 100        |

| 6.4.1    | RS-FF (einflankengesteuert)              | 101        |

| 6.4.2    | D-FF (einflankengesteuert)               | 102        |

| 6.4.3    | JK-FF (einflankengesteuert)              | 105        |

| 6.4.4    | T-FF (einflankengesteuert)               | 106        |

| 6.4.5    | RS-MS-FF (zweiflankengesteuert)          | 106        |

| 6.4.6    | JK-MS-FF (zweiflankengesteuert)          | 107        |

| 6.5      | Charakteristische Gleichung              | 108        |

| 6.6      | Synthese-Tabellen                        | 110        |

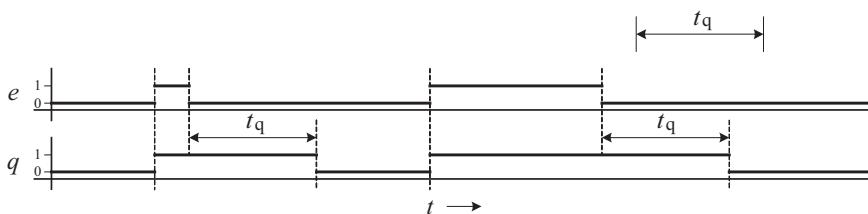

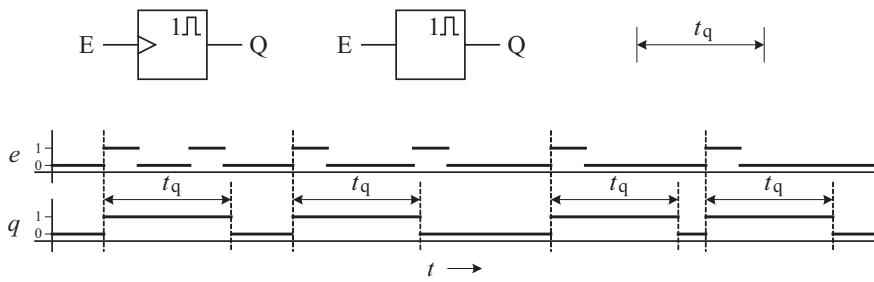

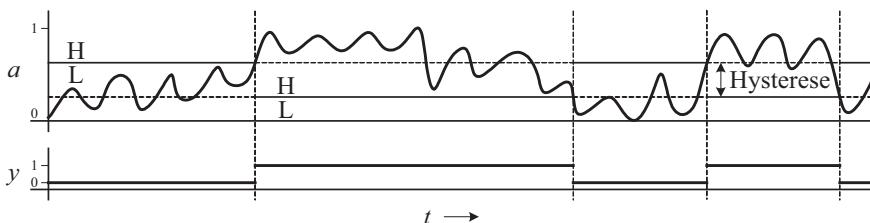

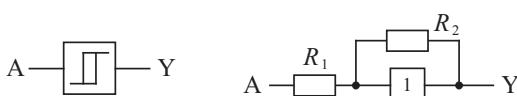

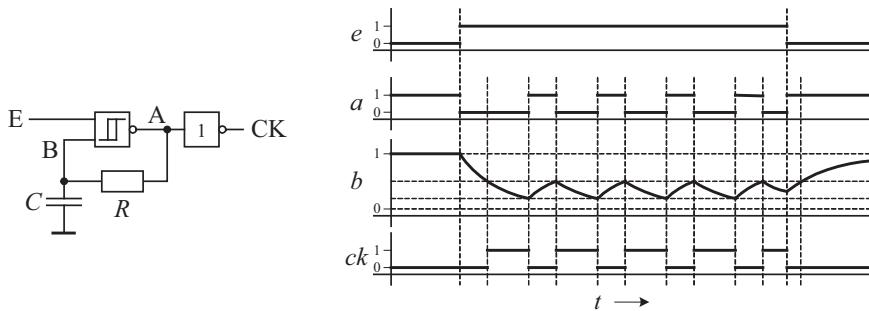

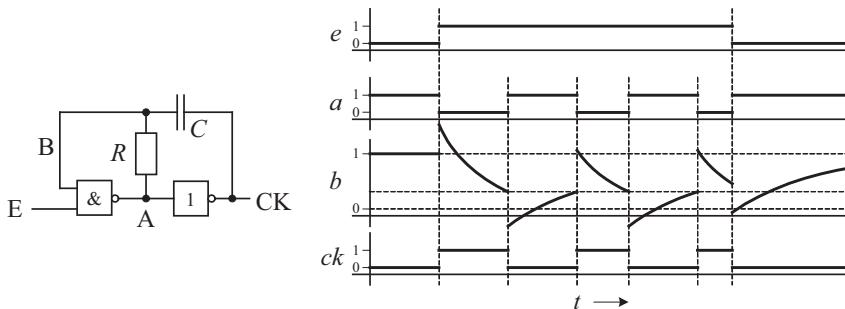

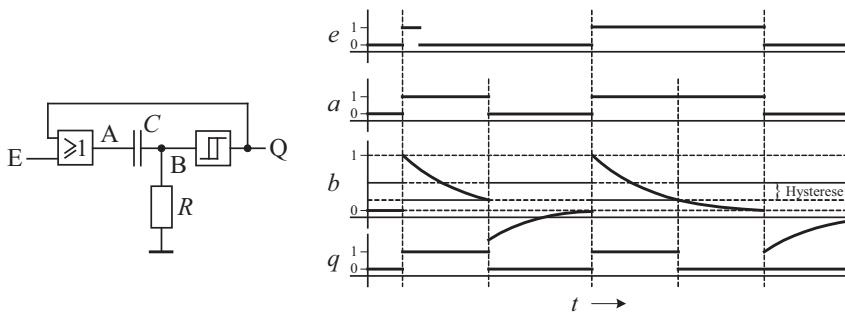

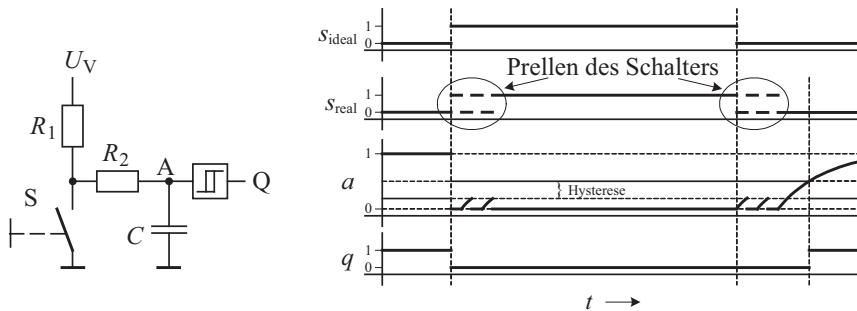

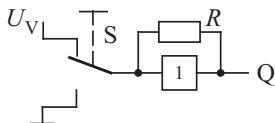

| 6.7      | Monostabile Kippstufen                   | 111        |

| 6.8      | Taktgeneratoren                          | 114        |

| 6.9      | Aufgaben                                 | 115        |

| <b>7</b> | <b>Einfache sequenzielle Schaltungen</b> | <b>117</b> |

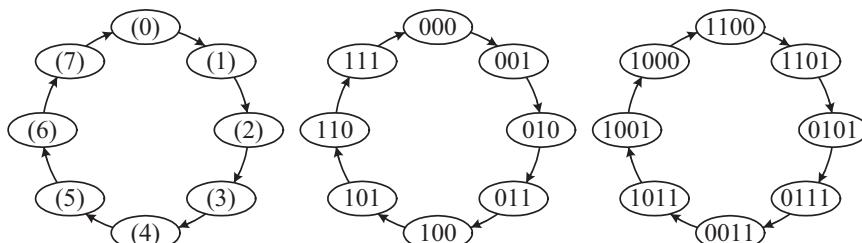

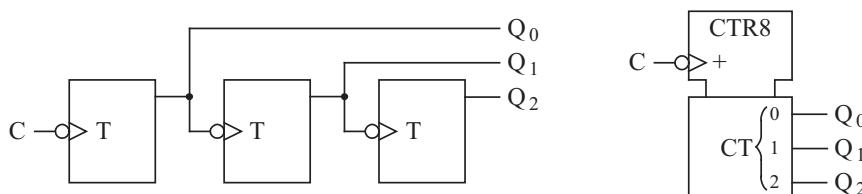

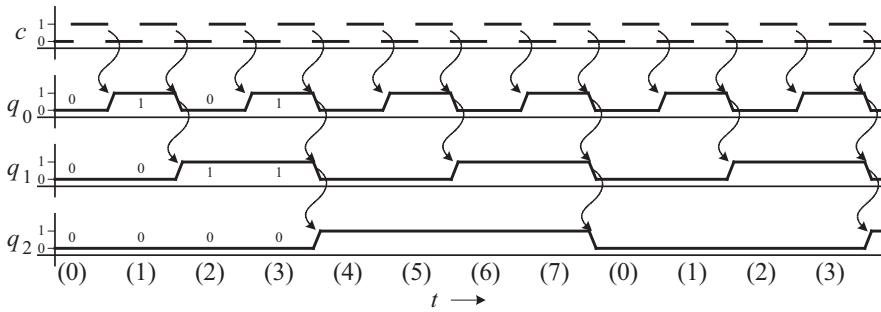

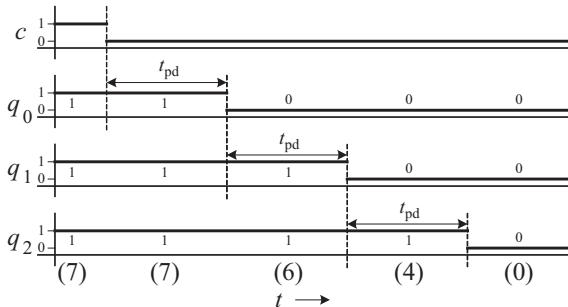

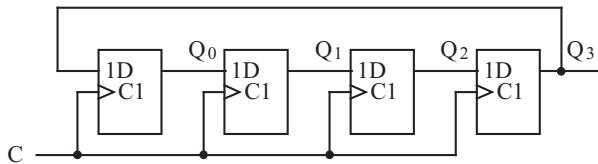

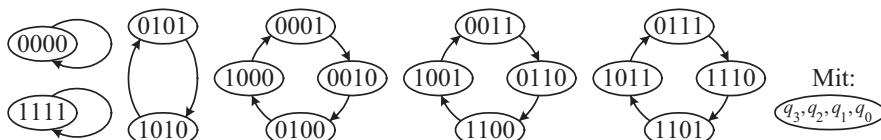

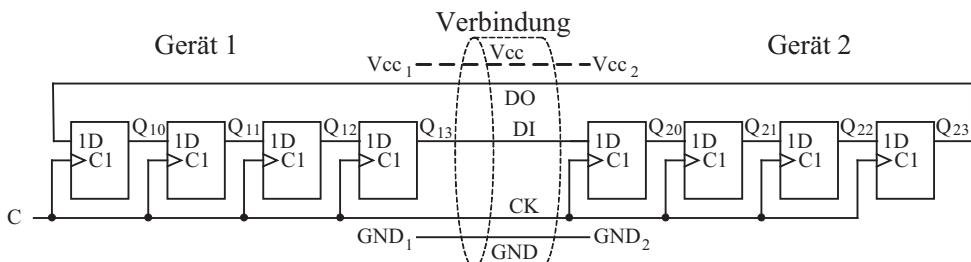

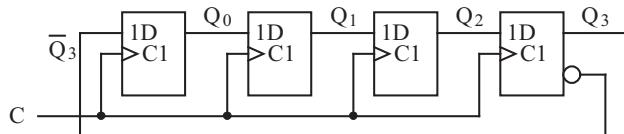

| 7.1      | Zählerschaltungen                        | 117        |

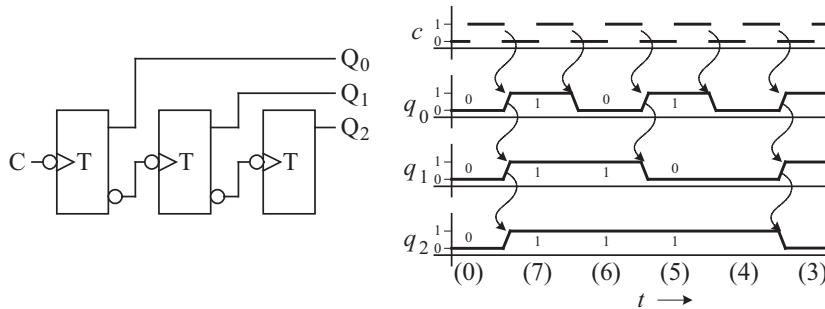

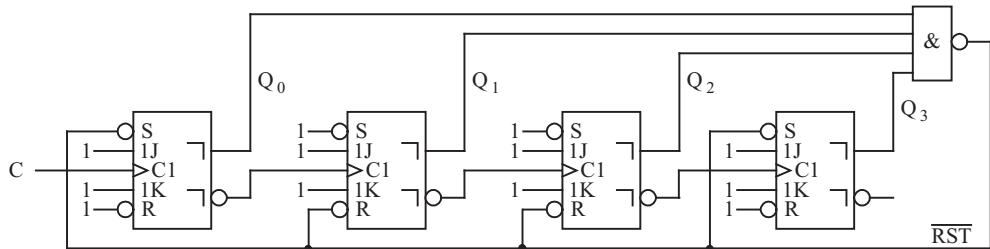

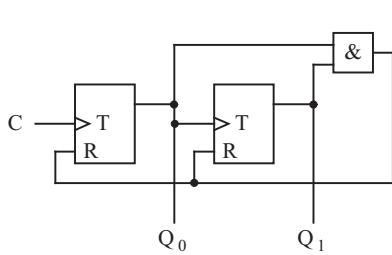

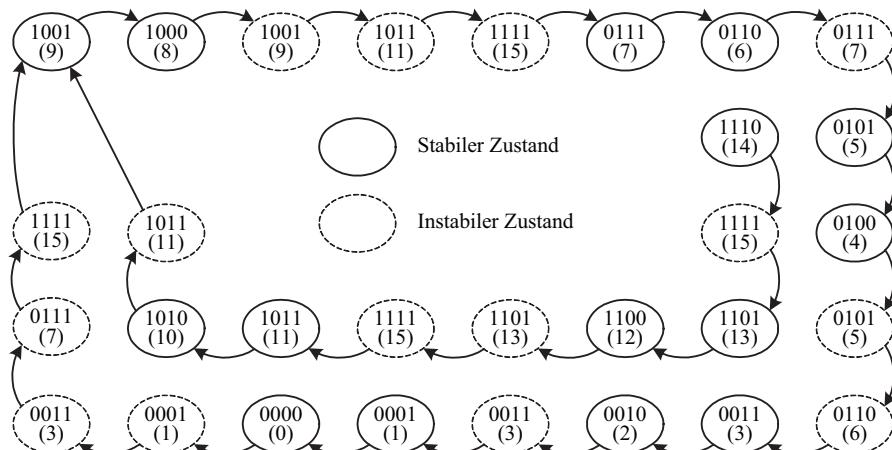

| 7.1.1    | Asynchronzähler                          | 118        |

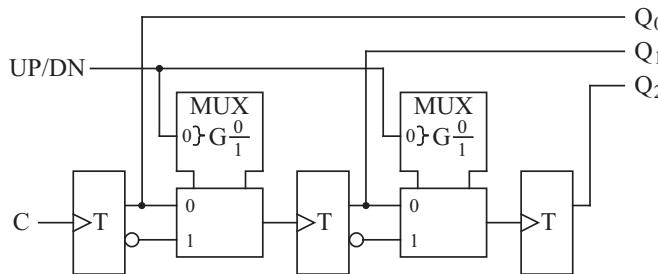

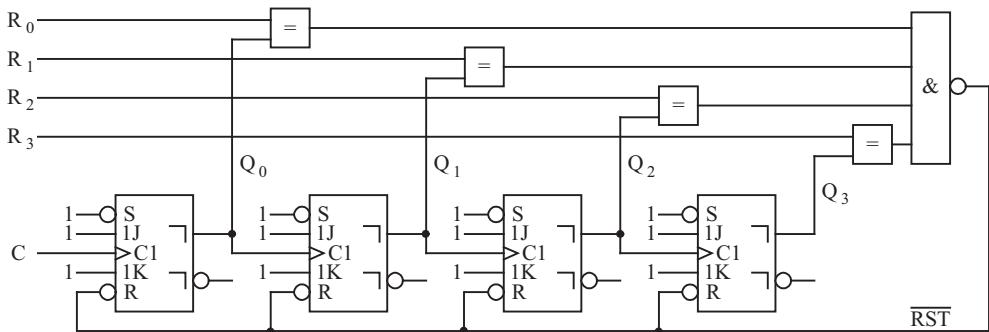

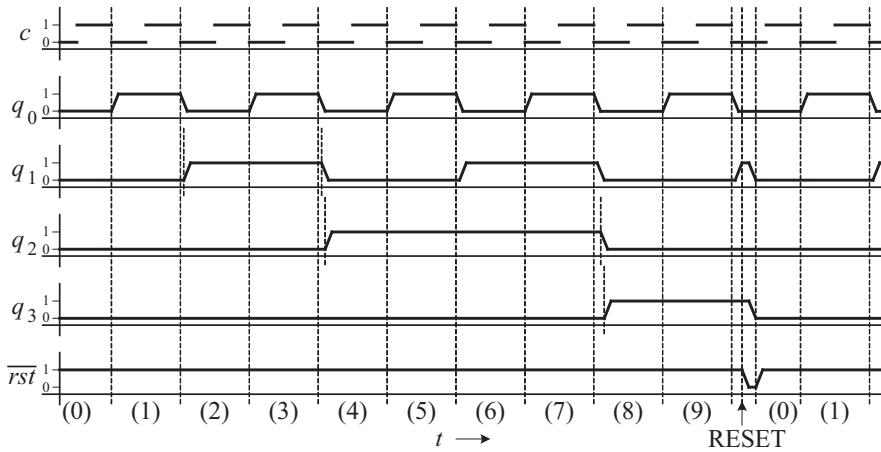

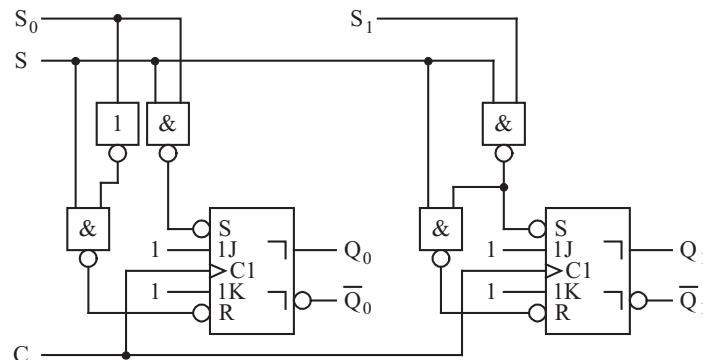

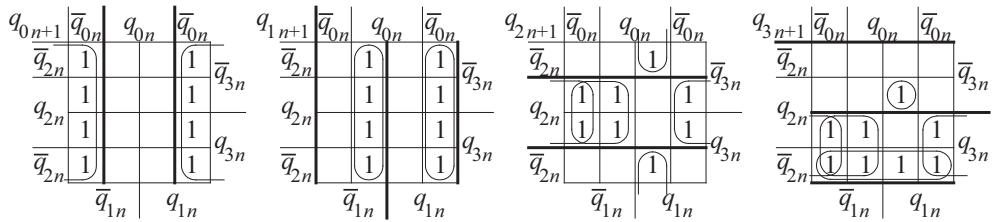

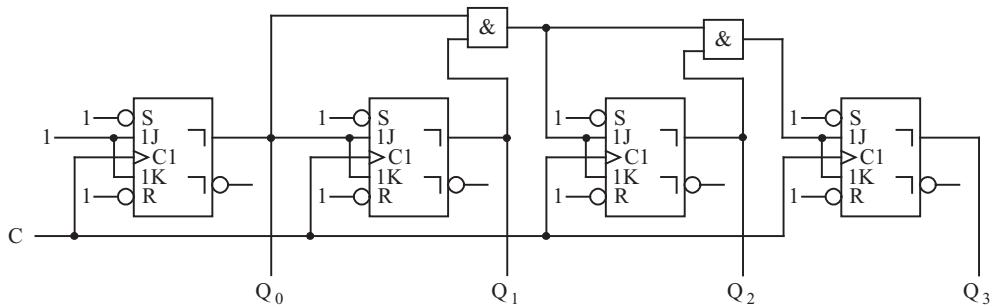

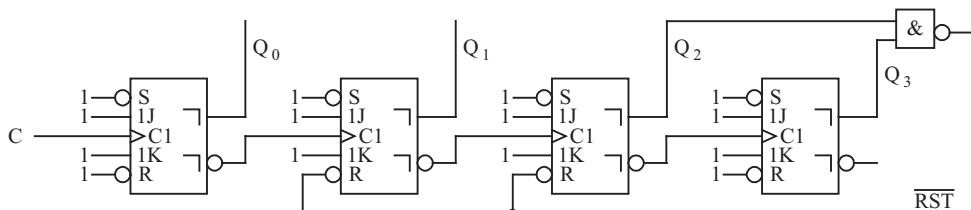

| 7.1.2    | Synchronzähler                           | 122        |

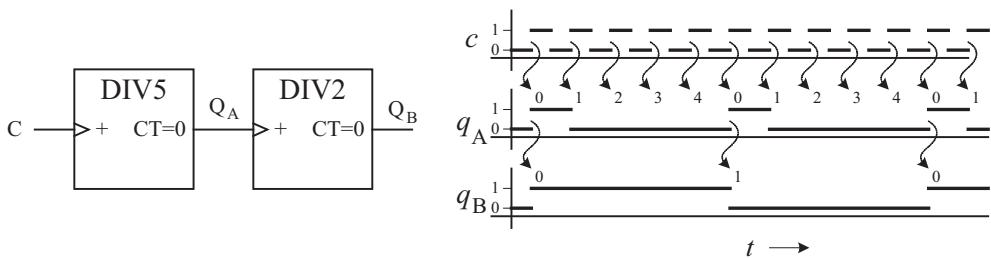

| 7.2      | Frequenzteiler                           | 131        |

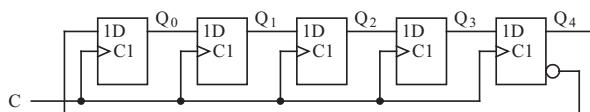

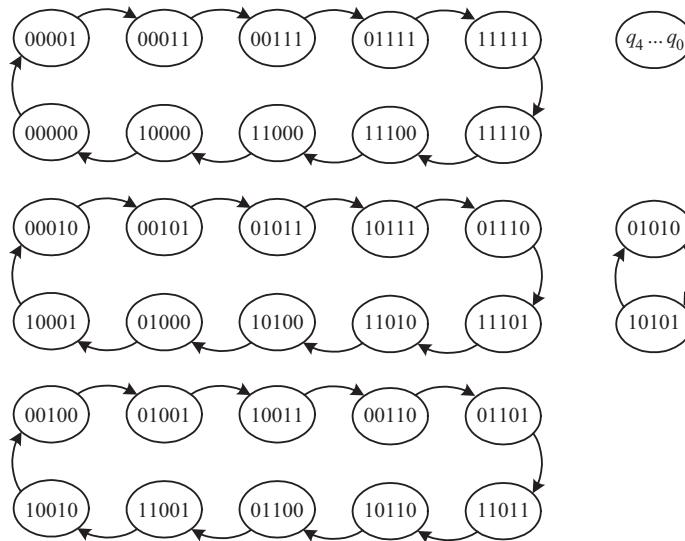

| 7.3      | Schieberegister                          | 135        |

| 7.4      | Aufgaben                                 | 139        |

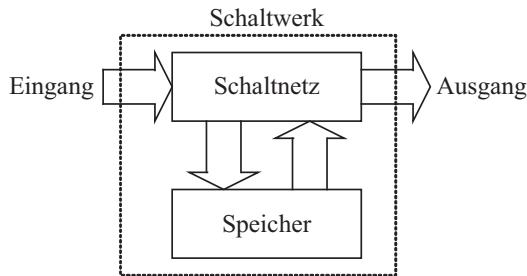

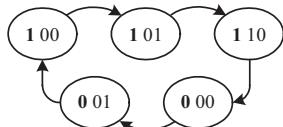

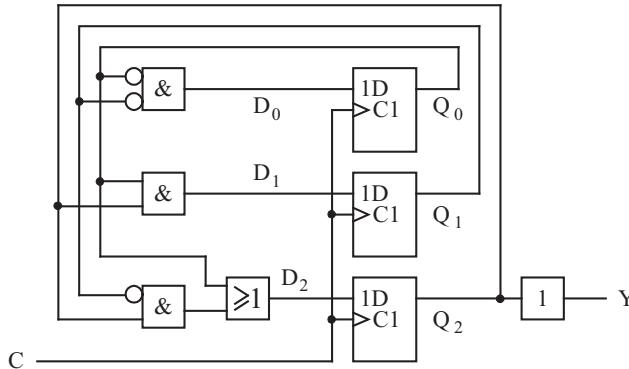

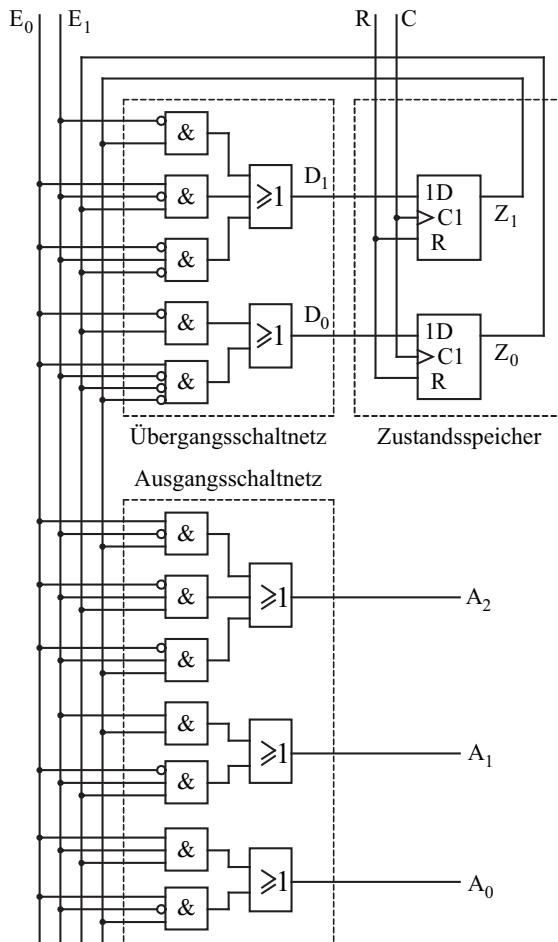

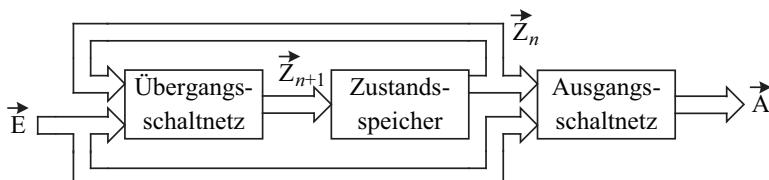

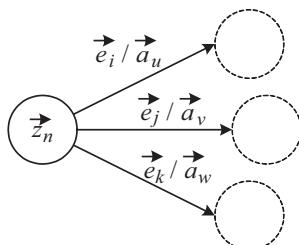

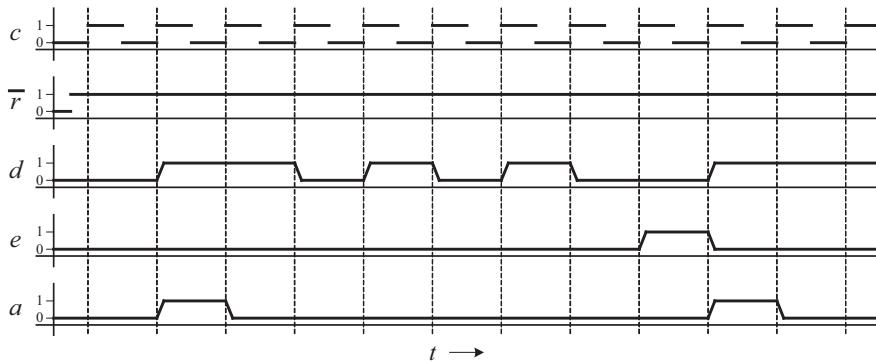

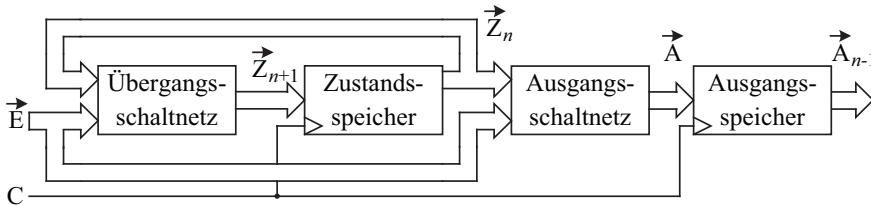

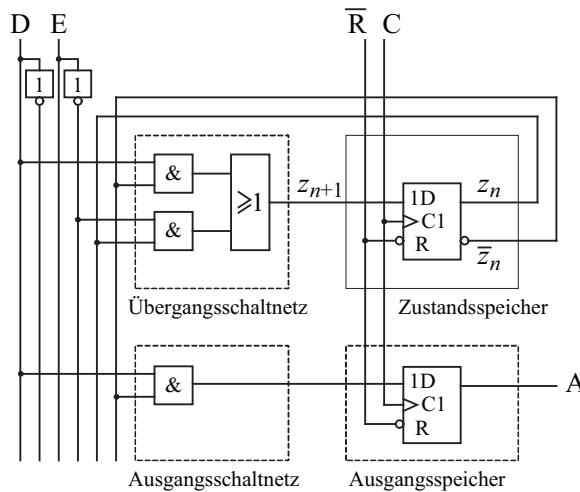

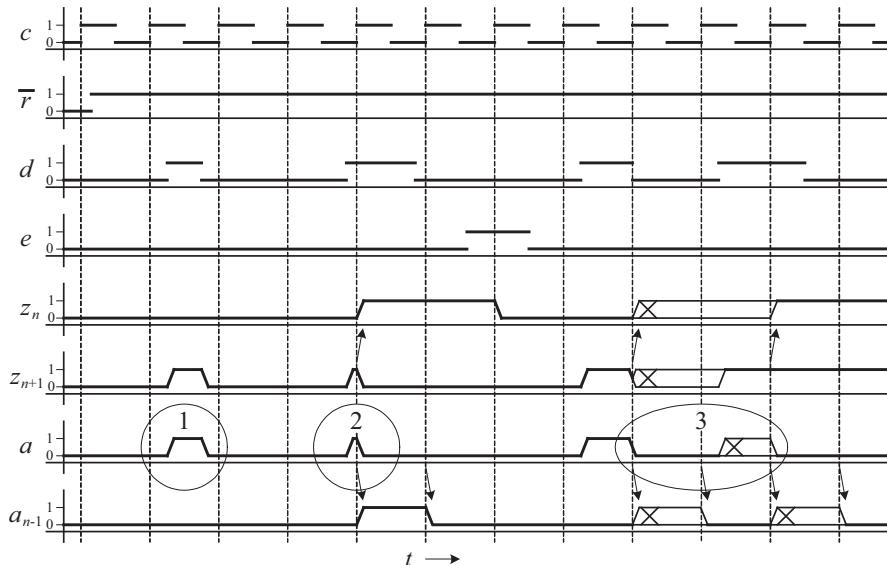

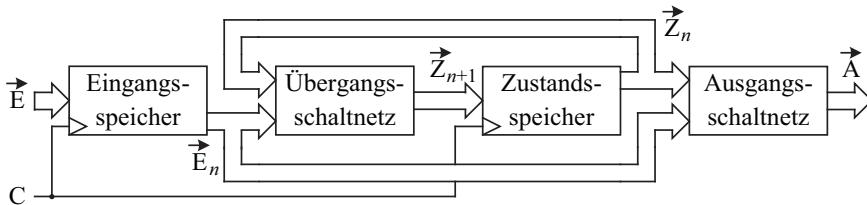

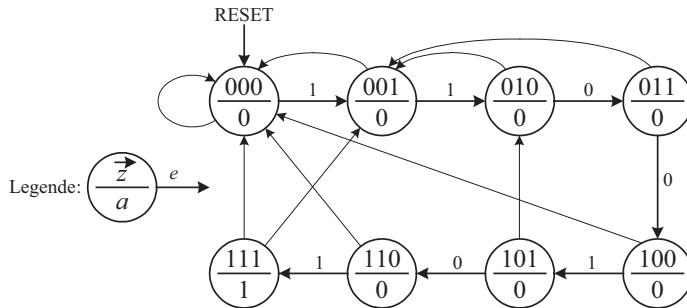

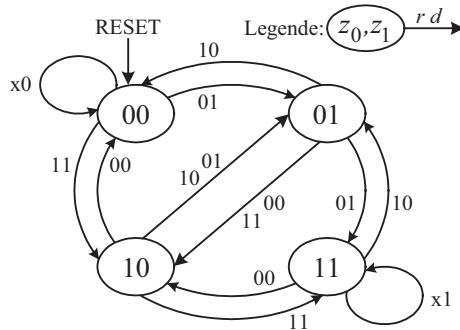

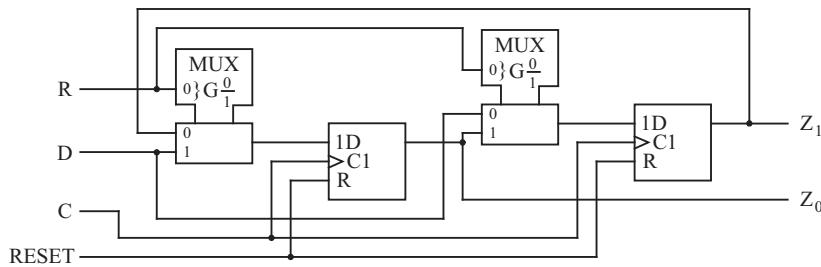

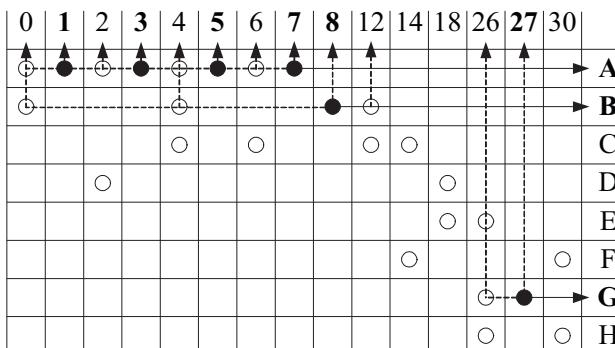

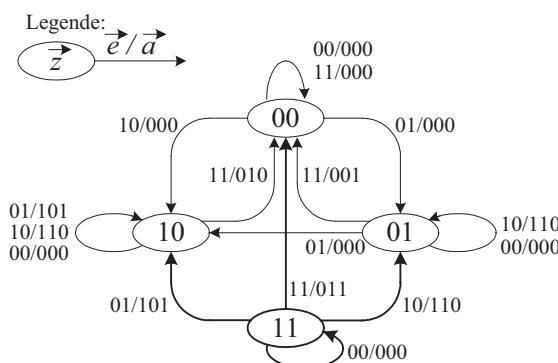

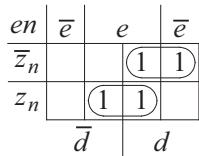

| <b>8</b> | <b>Getaktete Schaltwerke</b>             | <b>141</b> |

| 8.1      | Einführung                               | 141        |

| 8.2      | Mealy-Automat                            | 147        |

| 8.3      | Moore-Automat                            | 154        |

| 8.4      | Aufgaben                                 | 159        |

|                                                            |                                      |            |

|------------------------------------------------------------|--------------------------------------|------------|

| <b>9</b>                                                   | <b>Hardware</b>                      | <b>161</b> |

| 9.1                                                        | Einführung .....                     | 161        |

| 9.2                                                        | Schaltkreisentwicklung .....         | 162        |

| 9.3                                                        | Physikalische Randbedingungen .....  | 166        |

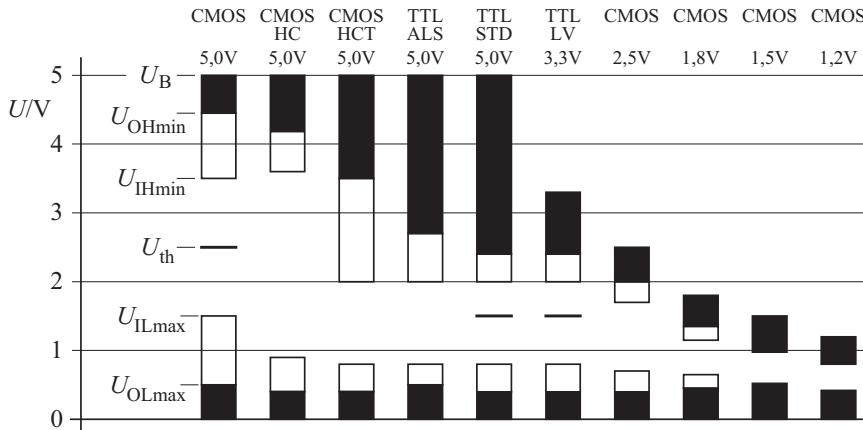

| 9.3.1                                                      | Spannungsbereiche .....              | 166        |

| 9.3.2                                                      | Strombereiche .....                  | 167        |

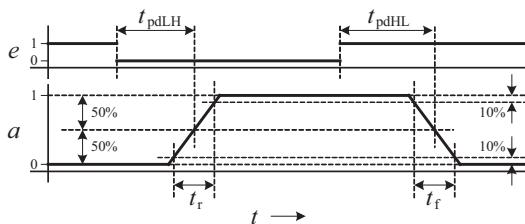

| 9.3.3                                                      | Geschwindigkeitsbereiche .....       | 169        |

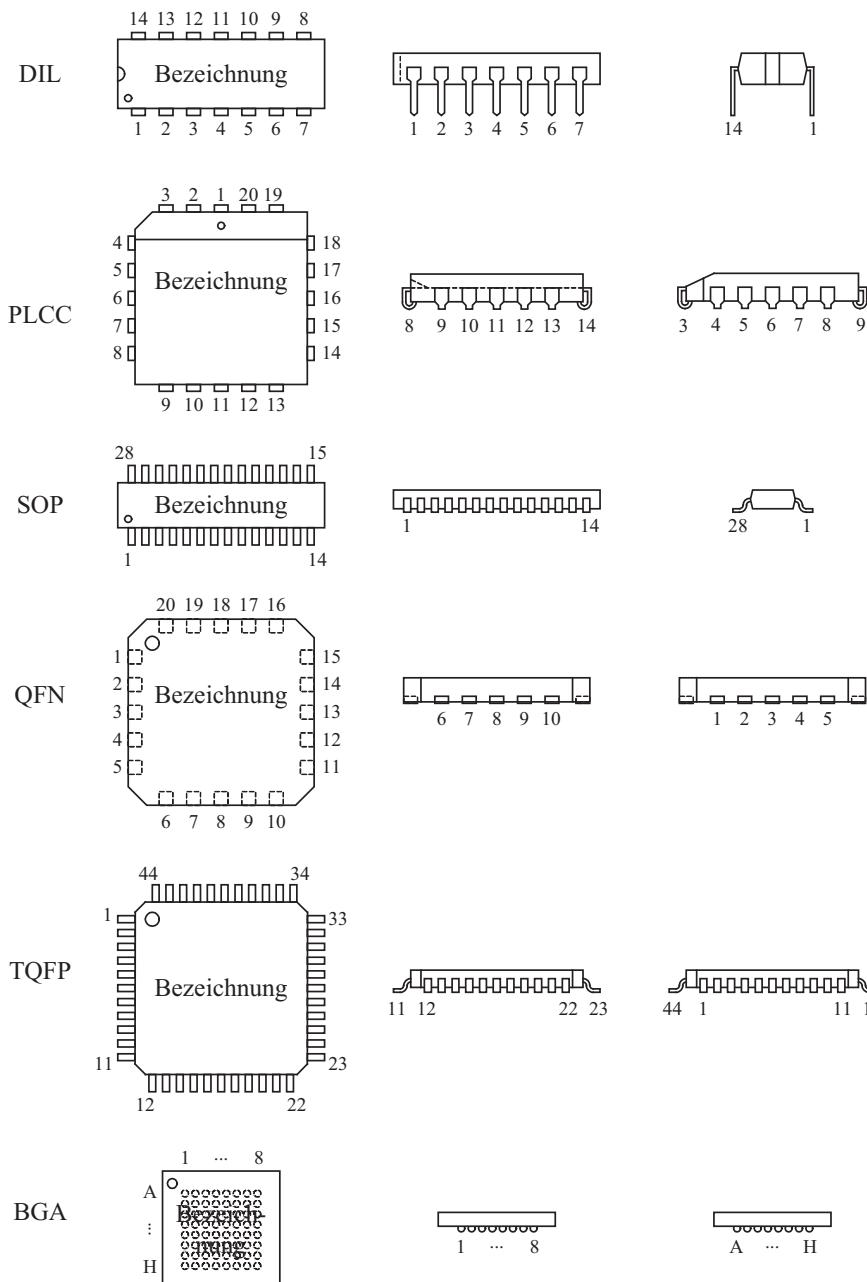

| 9.3.4                                                      | Gehäuse .....                        | 172        |

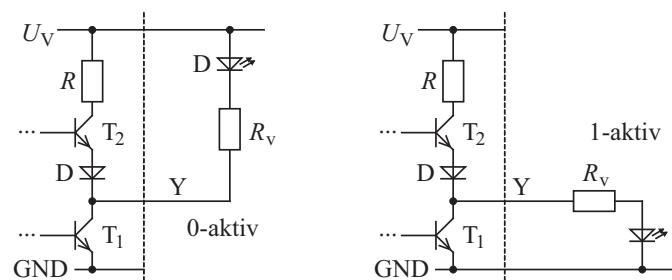

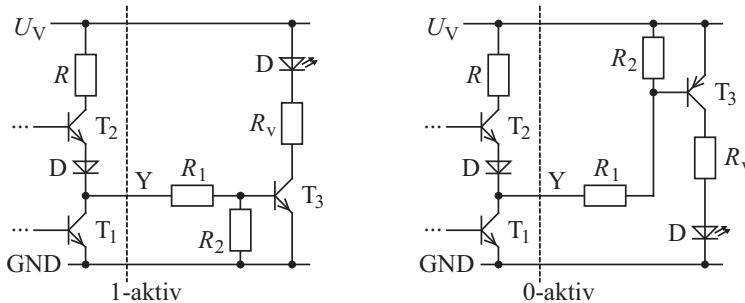

| 9.4                                                        | Spezielle Ausgänge .....             | 174        |

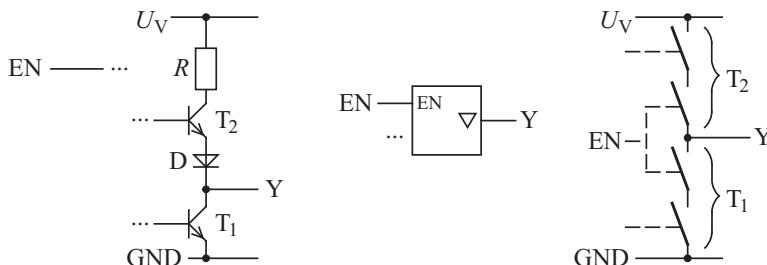

| 9.4.1                                                      | Tri-State-Ausgang .....              | 175        |

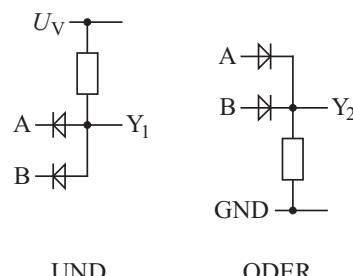

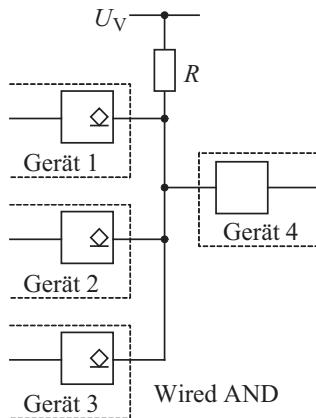

| 9.4.2                                                      | Open-Kollektor-Ausgang .....         | 177        |

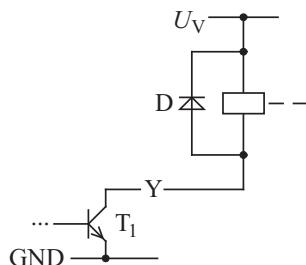

| 9.5                                                        | Spezielle Eingänge .....             | 178        |

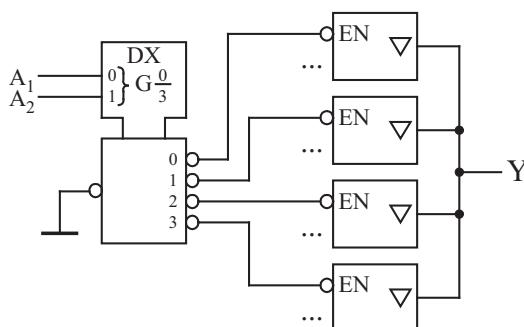

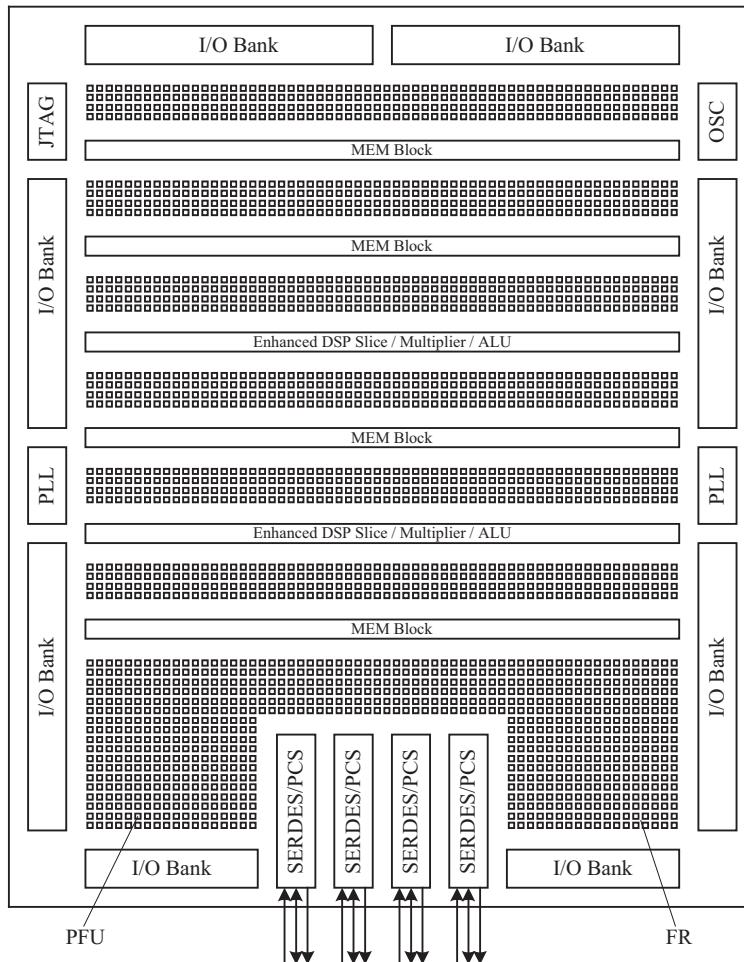

| 9.6                                                        | Strukturen komplexer Bausteine ..... | 183        |

| <b>10</b>                                                  | <b>Musterlösungen</b>                | <b>190</b> |

| 10.1                                                       | Lösungen zu Kapitel 2 .....          | 190        |

| 10.2                                                       | Lösungen zu Kapitel 3 .....          | 193        |

| 10.3                                                       | Lösungen zu Kapitel 4 .....          | 197        |

| 10.4                                                       | Lösungen zu Kapitel 5 .....          | 204        |

| 10.5                                                       | Lösungen zu Kapitel 6 .....          | 210        |

| 10.6                                                       | Lösungen zu Kapitel 7 .....          | 215        |

| 10.7                                                       | Lösungen zu Kapitel 8 .....          | 222        |

| <b>Verzeichnis von Formelzeichen und Abkürzungen</b> ..... |                                      | <b>229</b> |

| <b>Literatur</b> .....                                     |                                      | <b>235</b> |

| <b>Index</b> .....                                         |                                      | <b>237</b> |

# 1

## Einleitung

Digitaltechnische Realisierungen sind in der heutigen Zeit nicht mehr wegzudenken. Man ist es gewohnt, Handy und Digitalfernseher zu verwenden. Die Funktionsweise ist den meisten Benutzern nicht bekannt und wird für die Benutzung digital arbeitender Geräte auch nicht benötigt. Technikinteressierte möchten jedoch mehr über die Funktionsweise wissen. Hierzu könnte man ein komplexes digitaltechnisches Gerät in seine Funktionsgruppen und weiter in seine Einzelkomponenten auflösen und deren Wirkungsweise vertiefen (**Top-Down Design**). Anschließend weiß man, wie dieses Gerät funktioniert, aber die Anpassung für weitere Anwendungen wurde nicht trainiert. Dieses Buch verwendet die andere Entwurfsrichtung. Basierend auf den Grundelementen, wird deren Zusammenschaltung zu einfachen Funktionsgruppen beschrieben und erläutert, sodass hieraus komplexere Geräte für verschiedene Anwendungen erstellt werden können (**Bottom-Up Design**). Dieses Buch beschreibt die rudimentären Elemente und grundlegenden Funktionsgruppen der Digitaltechnik. In der Einleitung werden die verwendeten Begriffe erläutert.

### ■ 1.1 Analog und digitale Darstellungsformen

#### 1.1.1 Analoge Größendarstellung

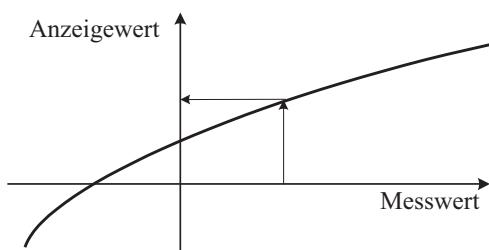

Viele uns bekannte Größen sind analoger Natur. Hierunter fallen u. a. Abstand, Temperatur, elektrische Spannung etc. Zur Beschreibung dieser Größen wurden analoge Darstellungen verwendet wie Länge an einem Referenzmaßstab (Metermaß), Flüssigkeitsthermometer, Zeigerinstrumente etc. Die verwendeten Werteangaben in diesem Bereich gehören zu den reellen Zahlen  $\mathbb{R}$ . Die Zuordnung zwischen Messwert (z. B. elektrische Spannung) und Darstellungs-wert (z. B. Winkeländerung der Zeigerposition) ist eine kontinuierliche Funktion. Bild 1.1 zeigt beispielhaft den Zusammenhang einer analogen Abbildungsfunktion. Theoretisch könnte bei

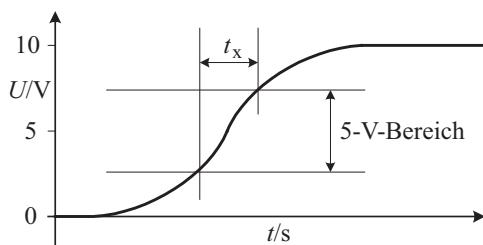

**Bild 1.1** Abbildungsfunktion

analog → analog

unendlicher Genauigkeit vom Anzeigewert auf den exakten verursachenden Messwert zurückgeschlossen werden. Grenzen sind durch die Ablesegenauigkeit gegeben, die häufig bei der dritten Stelle aufhört. Bei Mess- und Übertragungssystemen gibt es noch den unteren und oberen Grenzwert, die den Dynamikbereich der Anordnung vorgeben. Vorteil der analogen Darstellung ist u. a. die schnelle Erfassung sowie die Erkennung von Tendenzwerten (z. B. analoganzeigende Messgeräte). Dieser Vorteil wird häufig bei der Ausgabe digitaler Größen verwendet, wie z. B. bei der analoganzeigenden Digitaluhr.

### 1.1.2 Digitale Größendarstellung

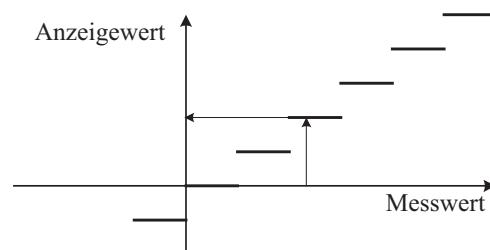

Die Bezeichnung „digital“ kommt aus dem Lateinischen (lat. *digitus* Finger (oder Zehe), zählen mit den Fingern). Sie beschreibt eine diskrete Größendarstellung also eine abzählbare Menge. Einige Größen sindzählbar (z. B. Anzahl von Eiern (Grundmenge ein Ei)), andere werden durch Quantisierung analoger Größen inzählbare digitale Einheiten unterteilt (z. B. Gewichtsklassen von Eiern (Klassen S, M, L oder XL)). Verwendet man sehr viele Klassen oder Stufen (z. B. bei Digitalwaagen), so erhält man bei vernachlässigbarer Klassenbreite bzw. Stufenhöhe einen nahezu kontinuierlichen Verlauf (ähnlich der analogen Abbildung). Bild 1.2 zeigt den Zusammenhang einer digitalen Abbildungsfunktion. Bestimmte Wertebereiche werden einem Digitalwert (einer Stufe) zugeordnet. Eine exakte Rekonstruktion des verursachenden Analogwertes ist hierbei prinzipiell nicht möglich, da ein Digitalwert immer einen Bereich der analogen Eingangsgröße abdeckt. Bei der Rekonstruktion wird normalerweise der Mittelwert des Wertebereiches der Stufe als Näherungswert verwendet. Ein anschaulicher Vergleich von analogem und digitalem Wert ist eine Treppe mit einer mitgeführten Fahrradrampe. Die Rampe gibt einen analogen Wert der Höhendifferenz wieder und die Stufen einen digitalen. Zu jeder digitalen Stufe gehört ein Bereich der zugehörigen analogen Höhendifferenz.

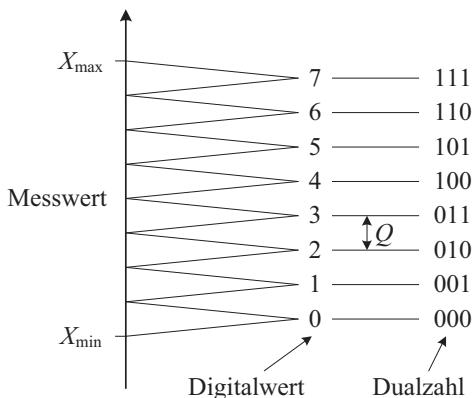

Eine häufig zu findende Darstellung entspricht Bild 1.3. Der Messwert in dem Bereich von  $X_{\min}$  bis  $X_{\max}$  wird in  $N$  äquidistante (gleichgroße) Bereiche mit der Breite  $Q$  unterteilt. Das **Quant**  $Q$  ist normalerweise  $Q = (X_{\max} - X_{\min})/N$ .

Der Digitalwert wird durch eine Zahl repräsentiert (Zahlendarstellungen werden im nächsten Kapitel erläutert), in der digitalen Welt ist dies häufig eine Dualzahl. Die Dualzahl besteht aus  $J$  binären Stellen, wodurch sich eine maximal verwendbare Anzahl von  $N = 2^J$  Stufen ergibt. In Bild 1.3 ist dieser Zusammenhang mit einem 3-stelligen Dualcode dargestellt.

Durch die ziffernmäßige Darstellung des Digitalwertes ist eine eindeutige Lesbarkeit gegeben (keine Ableseunterschiede zwischen erster und letzter Stelle). Die Auflösung ergibt sich durch die Quantisierungsstufe  $Q$ .

**Bild 1.2** Abbildungsfunktion

analog → digital

**Bild 1.3** Abbildung einer Messgröße in ein digitales Signal bzw. einen digitalen Signalwert

## ■ 1.2 Binäre und logische Zustände

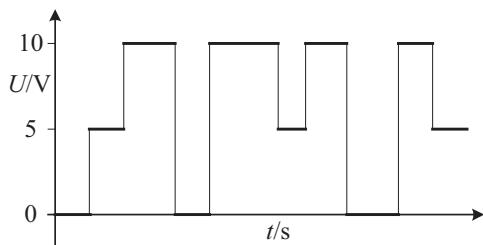

Eine digitale Größe besteht aus abzählbaren Elementen (Stufen). Ein digitaler Spannungsverlauf ist somit eine Folge von diskreten Spannungswerten (kein kontinuierlicher Übergang). Die Anzahl der Stufen ist beliebig, jedoch begrenzt durch die Unterscheidungsmöglichkeit (begrenzte Genauigkeit bei der Spannungsmessung). Bild 1.4 zeigt einen digitalen Spannungsverlauf mit drei Zuständen (0 V, 5 V und 10 V). Problematisch sind bei entsprechender Verwendung die Übergänge zwischen 0 V und 10 V und zwischen 10 V und 0 V. Aufgrund des analogen Verhaltens von Spannungswerten kann dieser Übergang nicht in der Zeit  $t = 0$  erfolgen.

**Bild 1.4** Digitales Spannungssignal mit drei Zuständen

Es wird für den Übergang immer ein gewisses, wenn auch sehr kurzes Zeitintervall benötigt. Bei schnellen Signalfolgen (häufiger Wechsel zwischen den Spannungswerten, Zeitspanne für Spannungsänderungen nicht mehr vernachlässigbar) ist der Übergang über die 5 V Stufe problematisch. Bild 1.5 zeigt einen analogen Übergang zwischen 0 V und 10 V mit der un-

**Bild 1.5** Analoger Übergang eines Spannungswechsels von 0 V auf 10 V

gewünschten Übergangszeit  $t_x$ . Der für die 5V Stufe verwendete Spannungsbereich (Messgenauigkeit dieser Stufe, etc.) wird durchlaufen und dies könnte zur Detektion dieser nicht im eigentlichen Spannungsverlauf angezeigten Spannungsstufe führen.

Ein digitales Signal mit mehr als zwei Zuständen ist deshalb für einfache Realisierungen nicht geeignet. Zwei Spannungsbereiche lassen sich durch einen Übergang (einen Schwellwert) unterscheiden. Ein zweiwertiges Signal hat zwei mögliche Zustände und wird deswegen binäres Signal genannt (lat. binär = aus 2 Einheiten bestehend). Die allgemein angewandte Digitaltechnik arbeitet mit binären Signalen.

Vorteil dieser Signale ist, dass sich die zwei Bereiche leicht unterscheiden und, was häufig vorkommt, zur Vermeidung von Störeinflüssen vergleichsweise gut verstärken lassen (ein durch Störeinflüsse verschwommenes Signal wird rekonstruiert). Der negativere Bereich wird mit L (Low) und der positivere Bereich mit H (High) gekennzeichnet. Diesen Bereichen müssen logische Zustände zugeordnet werden. Bei positiven Betriebsspannungen entspricht normalerweise H der logischen 1 (wahr, zutreffend oder ja) und L der logischen 0 (falsch, nicht zutreffend oder nein). Es existiert auch die umgedrehte Zuordnung, die in der Regel mit negativer Betriebsspannung gekoppelt ist. Sie wird als **negative Logik** bezeichnet ( $0 \hat{=} H$ ,  $1 \hat{=} L$ ). Diese Zuordnung ist bei den derzeitigen Realisierungen eigentlich nicht mehr anzutreffen und man nimmt stillschweigend die **positive Logik** an ( $1 \hat{=} H$ ,  $0 \hat{=} L$ ). Bei der Diskussion logischer Verknüpfungen werden 0 und 1, bei der hardwaremäßigen Realisierung mit Logikelementen die Bezeichnungen L und H verwendet.

Binäre Systeme sind in fast allen technischen Geräten vorhanden.

#### Vorteile

- Verarbeitet werden nur zwei Werte (0 und 1 bzw. L und H)

- Impulse (Rechteckimpulse) sind einfach und vollständig regenerierbar

- Einfache Verstärkung (Schalter, Relais)

- Verknüpfen, verteilen und sortieren von Informationen mittels logischer Schaltungen

- Speicher einfach realisierbar

- Mathematische Probleme werden auf Addition zurückgeführt und gelöst

- Verschiedene mathematische Probleme können mit derselben Schaltung gelöst werden

- Genauigkeit kann durch Vergrößern der Stellenzahl beliebig erhöht werden

#### Nachteile

- Prinzipieller Fehler durch Rasterung (Quantisierungsstufe  $Q$  bestimmt Fehlergröße)

## ■ 1.3 Zahlensysteme

### 1.3.1 Zahlendarstellungen

Im Laufe der Zeit haben sich verschiedene, teilweise anwendungsspezifische Zahlensysteme entwickelt, von denen hier einige exemplarisch vorgestellt werden.

|       |   |            |   |             |          |

|-------|---|------------|---|-------------|----------|

| 5 mal | I | wird durch | V | dargestellt | (= 5)    |

| 2 mal | V | wird durch | X | dargestellt | (= 10)   |

| 5 mal | X | wird durch | L | dargestellt | (= 50)   |

| 2 mal | L | wird durch | C | dargestellt | (= 100)  |

| 5 mal | C | wird durch | D | dargestellt | (= 500)  |

| 2 mal | D | wird durch | M | dargestellt | (= 1000) |

**Tabelle 1.1** Bündelungen des Römischen Zahlensystems

In der **Abzählschreibweise** werden gleichwertige Striche verwendet, wie es von Kaffeelisten oder Bierdeckeln bekannt ist. Zur Übersicht gibt es die Bündelung, bei der nach vier Strichen der fünfte über diese vier gezeichnet wird und diese Gruppe (dieses Symbol) eine Fünf repräsentiert. Die Position der Striche ist ohne Bedeutung. Diese Darstellung verwendet den Zahlenraum  $\mathbb{N}$  (ganze Zahlen) und ist nur für kleine Mengen einsetzbar.

Das **Römische Zahlensystem** deckt ebenfalls nur den positiven Ganzzahlenbereich  $\mathbb{N}$  ab und verwendet die Zweier- und Fünfer-Bündelung wie in Tabelle 1.1 angegeben.

Außerdem wird die Stellenschreibweise verwendet. Hierdurch entscheidet die Position über den Wert der Zahl. Die Zahl Vier wird z. B. nicht durch IIII sondern durch IV (5 – 1) dargestellt und unterscheidet sich aufgrund der Stellenschreibweise von der Sechs dargestellt durch VI (5 + 1). Das Zahlensystem ist unhandlich und eignet sich nicht für Rechenoperationen.

Bei der **Stellenschreibweise** ergibt sich der Wert nicht nur durch die verwendeten Symbole wie bei den Römischen Zahlen sondern durch die Position innerhalb der Darstellung. Das Bildungsgesetz zeigt Gleichung 1.1

$$N = \left( \sum_{j=0}^{J-1} n_j \cdot W_j \right) \quad (1.1)$$

Hierbei hat jede Stelle  $j$  einen Wert  $W_j$ . Bei der Angabe 01:02:03:04 muss der Wert jeder Stelle bekannt sein. Hier könnte es Tag:Stunde:Minute:Sekunde sein. Der Wertebereich der linken Stelle mit dem Wert 1 ist der Tag, der mit dem Faktor 24 auf eine Stundenzahl umgerechnet werden kann. Der Wert 2 (Werte von 0 bis 23 sind an dieser Stelle möglich) kann mit dem Faktor 60 auf Minuten umgerechnet werden. Der Wert 3 (Werte von 0 bis 59 sind an dieser Stelle möglich) kann mit dem Faktor 60 auf Sekunden umgerechnet werden. Der angegebene Wert umgerechnet in die kleinste Einheit, in diesem Fall die Sekunde, ergibt:

$$N = (1 \cdot (24 \cdot 60 \cdot 60) + 2 \cdot (60 \cdot 60) + 3 \cdot (60) + 4 \cdot (1)) = 93\,784 \quad (1.2)$$

Rechenoperationen mit der Stellenschreibweise sind aufgrund der Umrechnungsfaktoren, die z. B. bei der Umrechnung von Monaten in Tage vom jeweiligen Monat abhängen, ungünstig. Innerhalb der jeweiligen Stelle wird der Wert in dem genannten Beispiel bereits mit dem Polyadischen Zahlensystem beschrieben.

Das Bildungsgesetz des **Polyadischen Zahlensystems** für Ganzzahlen  $\mathbb{Z}$  zeigt Gleichung 1.3. Hierbei ergibt sich die Wertigkeit einer jeweiligen Stelle aus dem Basiswert  $B$  mit der Stellenzahl  $j$  als Exponent.

$$N = \left( \sum_{j=0}^{J-1} n_j \cdot B^j \right) \quad (1.3)$$

In dem normalerweise verwendeten **Zehnersystem** ist  $B = 10$  und  $n$  ein Element der Menge  $\{0, 1, 2, 3, 4, 5, 6, 7, 8, 9\}$ . Die Zahl 4711 ist eine 4-stellige Zahl ( $J = 4$ ). Die Darstellung des Wertes ist trivial und soll hier zur Verdeutlichung des Rechenweges verwendet werden.

$$N = (4 \cdot 10^3 + 7 \cdot 10^2 + 1 \cdot 10^1 + 1 \cdot 10^0) = 4711 \quad (1.4)$$

Diese Zahlendarstellung kann für verschiedene Basiswerte verwendet werden. In der binären Darstellung erhält man das **Dualsystem**. In diesem Fall ist  $B = 2$  mit  $n \in \{0, 1\}$ . Die Dualzahl  $1100101_2$  (Index 2 kennzeichnet das 2er-System) hat folgenden Wert:

$$N = (1 \cdot 2^6 + 1 \cdot 2^5 + 0 \cdot 2^4 + 0 \cdot 2^3 + 1 \cdot 2^2 + 0 \cdot 2^1 + 1 \cdot 2^0) = 101_{10} \quad (1.5)$$

Nach dem gleichen System ist das **Oktalsystem** ( $B = 8, n \in \{0, 1, 2, 3, 4, 5, 6, 7\}$ ) aufgebaut. Im Vergleich zu dem Dualsystem werden jeweils 3 Bit (Bit  $\hat{=}$  kleinste Einheit) zusammengefasst. Die Dualzahl  $1100101_2$  wird mit führenden Nullen auf ein Vielfaches von 3 Stellen erweitert zu 001 100 101 und jede Dreiergruppe durch das zugehörige Symbol repräsentiert gemäß 145<sub>8</sub> oder O145 (Oktal 145).

Gebräuchlicher ist das **Sezimalsystem** oder **Hexadezimalsystem**. Hierbei ist  $B = 16$  und  $n \in \{0, 1, 2, \dots, 8, 9, A, B, C, D, E, F\}$ . Da 16 Zeichen benötigt werden, ergänzt man die gebräuchlichen Ziffern um die ersten 6 Buchstaben des Alphabets. Im Vergleich zu dem Dualsystem werden hier 4 Stellen zu einer Hexadezimalziffer zusammengefasst. Die Dualzahl  $1100101_2$  wird wiederum mit führenden Nullen erweitert zu 0110 0101 und jede Vierergruppe durch das zugehörige Symbol repräsentiert gemäß 65<sub>16</sub> oder H65 (Hexadezimal 65).

Im Weiteren werden diese Zahlensysteme nicht zum Rechnen verwendet. Sie dienen gegebenenfalls zur verkürzten Schreibweise verwendeter Bitkombinationen.

Werden diese Zahlen übertragen, so muss der Empfänger wissen, in welcher Reihenfolge die Ziffern übertragen werden. Das höchstwertige Bit (in der Regel links) ist das **MSB (Most Significant Bit)** und das niedwertigste Bit (in der Regel rechts) ist das **LSB (Least Significant Bit)**.

Die Zahlendarstellung kann auch für Nachkommastellen erweitert werden. Eine 5-stellige Zahl mit zwei Vor- und drei Nachkommastellen hat das in Gleichung 1.6 angegebene Bildungsgesetz. Ein Beispiel im Dualcode zeigt Bild 1.6. Jede Nachkommastelle reduziert hierbei die Quantisierungsstufe  $Q$  auf die Hälfte. Bei drei Nachkommastellen ist dies  $2^{-3} = 0,125$  bzw.  $\pm 0,0625$ .

$$N = \left( \sum_{j=-3}^1 n_j \cdot B^j \right) \quad (1.6)$$

$$\text{Wertigkeit} \left| \begin{array}{c|c|c|c|c} 2^1 & 2^0 & 2^{-1} & 2^{-2} & 2^{-3} \\ \hline 1 & 0 & 1 & 0 & 1 \end{array} \right| = 1 \cdot 2 + 0 \cdot 1 + 1 \cdot 0,5 + 0 \cdot 0,25 + 1 \cdot 0,125 = 2,625$$

**Bild 1.6** Beispiel einer Dualzahl mit Nachkommastellen

Im **Polyadischen Zahlensystem** können Addition, Subtraktion, (Bild 1.7) Multiplikation (Bild 1.8) und Division (Bild 1.9) in gewohnter Weise durchgeführt werden.

| $b$ | $a$ | $b+a$ |                       | $b$ | $a$ | $b-a$ |                        |

|-----|-----|-------|-----------------------|-----|-----|-------|------------------------|

| 0   | 0   | 0 0   |                       | 0   | 0   | 0 0   |                        |

| 0   | 1   | 0 1   | + 0 1 1 0             | 0   | 1   | 1 1   | - 0 1 1 0              |

| 1   | 0   | 0 1   | carry $\rightarrow^1$ | 1   | 0   | 0 1   | borrow $\rightarrow^1$ |

| 1   | 1   | 1 0   | 1 0 1 0               | 1   | 1   | 0 0   | 0 1 0 0                |

|     |     |       | —                     |     |     |       | —                      |

|     |     |       | 10                    |     |     |       | 4                      |

**Bild 1.7** Beispiele für Addition und Subtraktion im Dual- und Dezimalsystem

| $b$ | $a$ | $b \cdot a$ | $11 \cdot 0101$ | $3 \cdot 05$ |

|-----|-----|-------------|-----------------|--------------|

| 0   | 0   | 0           | 11              | 15           |

| 0   | 1   | 0           | + 00            | + 0          |

| 1   | 0   | 0           | + 11            | 15           |

| 1   | 1   | 1           | + 00            |              |

|     |     |             | 0 1 1 1 1       |              |

|                 |                 |                 |                 |

|-----------------|-----------------|-----------------|-----------------|

| $1111 : 11 =$   | $101$           | $15 : 3 =$      | $05$            |

| $- 11$          | $\overline{01}$ | $- 0$           | $\overline{15}$ |

| $\overline{01}$ |                 | $\overline{15}$ |                 |

| $- 0$           | $\overline{11}$ | $- 15$          | $\overline{0}$  |

| $\overline{11}$ |                 | $\overline{0}$  |                 |

| $- 11$          | $\overline{0}$  |                 |                 |

|                 |                 |                 |                 |

**Bild 1.8** Beispiel für die Multiplikation im Dual- und Dezimalsystem

**Bild 1.9** Beispiele für die Division im Dual- und Dezimalsystem

## ■ 1.4 Codierungen

Neben den Zahlensystemen können auch spezielle Codierungen verwendet werden, um die Wertigkeit einer digitalen Bitkombination zu kennzeichnen. In diesem Abschnitt werden zwei gebräuchliche Codierungen und einige damit verbundene Begriffe vorgestellt.

### 1.4.1 Binär Codierte Dezimalziffer

Für die Darstellung einer mehrstößigen dezimalen Zahl kann jede Ziffer durch einen Dualwert repräsentiert werden. Hierdurch ist die benötigte Hardware zur Umwandlung der übertragenen Bitkombination für alle Stellen gleich. Die Codierung wird **BCD-Code** (Binär Codierte Dezimalziffer) genannt.

Der Code besteht aus vier binären Stellen (4-stellig). Eine Gruppe aus vier Stellen wird **Tetraden**, **Halbbyte** oder **Nibble** genannt. Jeder Spalte kann ein Wert zugeordnet werden, sodass sich der Beitrag des Eintrags in der entsprechenden Spalte aus dem Wert des Symbols (hier 0 oder 1) multipliziert mit dem Wert der Spalte (hier 8, 4, 2, oder 1) ergibt. Aufgrund der Wertigkeiten wird dieser Code auch 8-4-2-1-Code genannt. Unter dem Begriff **Gewicht** versteht man die Anzahl der mit 1 besetzten Stellen. In diesem Fall beträgt das Gewicht je nach Ziffer 0 bis 3 für die jeweils betrachtete Bitkombination. Unter der **Distanz** versteht man die Anzahl der unterschiedlichen Bitstellen verschiedener Codewörter. In diesem Beispiel haben wir die geringste

| Ziffer | Wertigkeit |   |   |   |

|--------|------------|---|---|---|

|        | 8          | 4 | 2 | 1 |

| 0      | 0          | 0 | 0 | 0 |

| 1      | 0          | 0 | 0 | 1 |

| 2      | 0          | 0 | 1 | 0 |

| 3      | 0          | 0 | 1 | 1 |

| 4      | 0          | 1 | 0 | 0 |

| 5      | 0          | 1 | 0 | 1 |

| 6      | 0          | 1 | 1 | 0 |

| 7      | 0          | 1 | 1 | 1 |

| 8      | 1          | 0 | 0 | 0 |

| 9      | 1          | 0 | 0 | 1 |

| -      | 1          | 0 | 1 | 0 |

| -      | 1          | 0 | 1 | 1 |

| -      | 1          | 1 | 0 | 0 |

| -      | 1          | 1 | 0 | 1 |

| -      | 1          | 1 | 1 | 0 |

| -      | 1          | 1 | 1 | 1 |

Tabelle 1.2 BCD-Code

Distanz mit dem Wert 1 z. B. zwischen den Codierungen von 0 und 1, 0 und 2, 0 und 4 als auch zwischen 2 und 6. Die größte Differenz haben wir zwischen den Codierungen 7 und 8, bei der sich alle vier Stellen unterscheiden und wir deshalb hier die Distanz 4 haben. Unter der **Hamming-Distanz** versteht man den kleinsten Abstandswert. Die Hamming-Distanz ist ein Maß für die Erkennbarkeit von Fehlern und deren Korrigierbarkeit. Ein weiterer Begriff ist stetig. Die Codierung ist **stetig**, wenn benachbarte Codewörter sich immer um die gleiche Anzahl an Bitstellen unterscheiden. In dem BCD-Code ist das nicht der Fall (Distanz 1 zwischen 0 und 1 und Distanz 4 zwischen 7 und 8). Die **Redundanz**  $R$  ist ein Maß, das die Menge nicht benötigter Kombinationen beschreibt. Die Wahrscheinlichkeit des Auftretens der verwendeten Bitkombinationen wird hierbei als gleichverteilt angenommen.

$$R = \text{ld}(N_{\text{möglich}}) - \text{ld}(N_{\text{genutzt}}) = \frac{\log(N_{\text{möglich}})}{\log(2)} - \frac{\log(N_{\text{genutzt}})}{\log(2)} \quad (1.7)$$

Für den BCD-Code ist  $R = 4 - 3,322 = 0,678$  und kennzeichnet die Menge nicht benötigter Informationseinheiten. Da jedoch nur ganze Bitstellen verwendet werden, ist dieses Übermaß hinzunehmen. Die nicht verwendeten Bitkombinationen nennt man **Pseudotetraden**.

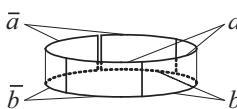

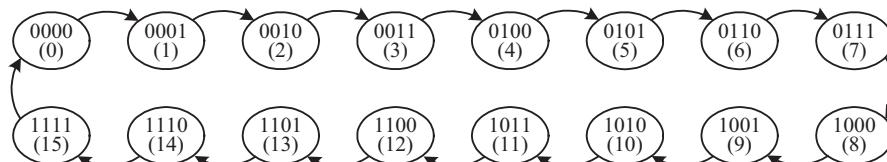

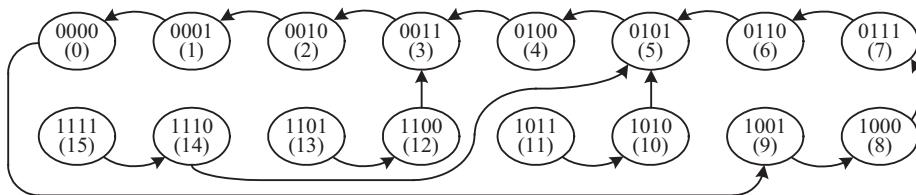

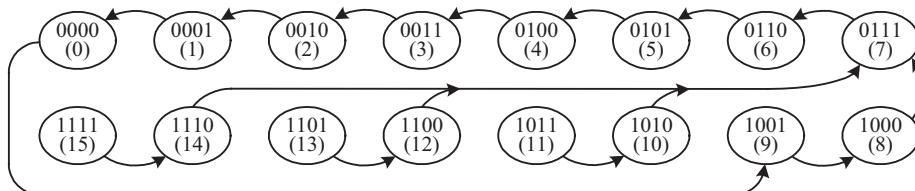

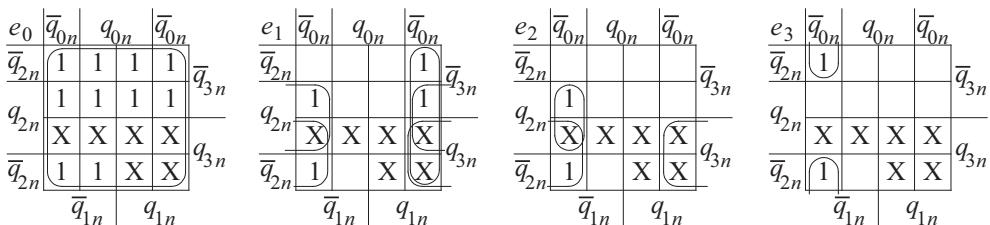

## 1.4.2 Gray-Code

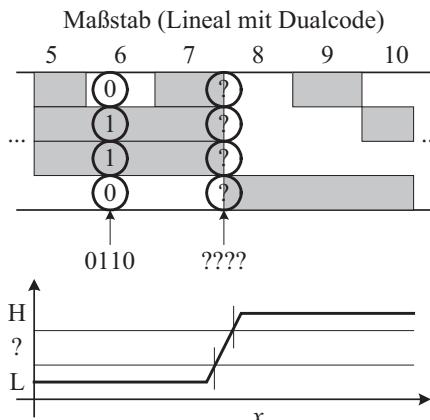

Ein Problem des Dualcodes ist die Detektion von Übergängen, z. B. zwischen den Codierungen für 7 und 8. Bild 1.10 zeigt einen Maßstab mit zwei möglichen Positionen eines Lesekopfes. In der linken Position sind die Markierungen auf dem Maßstab eindeutig erkennbar und der Lesekopf liefert die Bitkombination 0110. In der rechten Position liegt der Lesekopf genau an dem Übergang, bei dem sich alle Bitstellen ändern. Hier macht sich der analoge Charakter der Signale bemerkbar. Exemplarisch ist dies an dem positionsabhängigen Signal der Datenspur  $2^3$  im unteren Bildteil erkennbar. Es gibt einen Übergang, in dem H und L nicht eindeutig

**Bild 1.10** Signalwechsel zwischen 7 und 8 eines Maßstabes und der Signalverlauf der Datenspur

$2^3 = 8$

zugeordnet werden können. Dies trifft bei diesem Übergang für jede Datenspur zu. Hierdurch können prinzipiell alle möglichen Bitkombinationen als Ausgangssignal auftreten; Ursache ist der Wechsel mehrerer Bitstellen benachbarter Bitkombinationen. Der Dualcode ist somit für derartige Positionsbestimmungen nicht geeignet.

Abhilfe schafft eine Codierung, bei der sich benachbarte Bitkombinationen nur um eine Bitstelle unterscheiden. Dies ist der in Tabelle 1.3 angegebene **Gray-Code**.

| Ziffer | Wertigkeit |   |   |   |

|--------|------------|---|---|---|

|        | –          | – | – | – |

| 0      | 0          | 0 | 0 | 0 |

| 1      | 0          | 0 | 0 | 1 |

| 2      | 0          | 0 | 1 | 1 |

| 3      | 0          | 0 | 1 | 0 |

| 4      | 0          | 1 | 1 | 0 |

| 5      | 0          | 1 | 1 | 1 |

| 6      | 0          | 1 | 0 | 1 |

| 7      | 0          | 1 | 0 | 0 |

| 8      | 1          | 1 | 0 | 0 |

| 9      | 1          | 1 | 0 | 1 |

| 10     | 1          | 1 | 1 | 1 |

| 11     | 1          | 1 | 1 | 0 |

| 12     | 1          | 0 | 1 | 0 |

| 13     | 1          | 0 | 1 | 1 |

| 14     | 1          | 0 | 0 | 1 |

| 15     | 1          | 0 | 0 | 0 |

**Tabelle 1.3** Gray-Code

Der hier angegebene Gray-Code ist vierstellig. Die jeweiligen Bitstellen sind nicht bewertbar. Es werden alle Bitkombinationen verwendet, dadurch ist die **Hamming-Distanz** eins und die **Redundanz**  $R = 0$ . Besonderes Kennzeichen ist, dass sich benachbarte Bitstellen immer um ein Bit unterscheiden, deshalb ist dieser Code **stetig**. Bei den 16 verwendeten Bitkombinationen unterscheidet sich das letzte Codewort von dem ersten Codewort ebenfalls nur um eine Bitstelle. Dadurch ist diese Codierung **zyklisch** und für die Ermittlung einer Winkelposition in

rotierenden Messeinrichtungen geeignet. Der Gray-Code ist die Standardcodierung für absolut messende Längen- und Winkelpositionen.

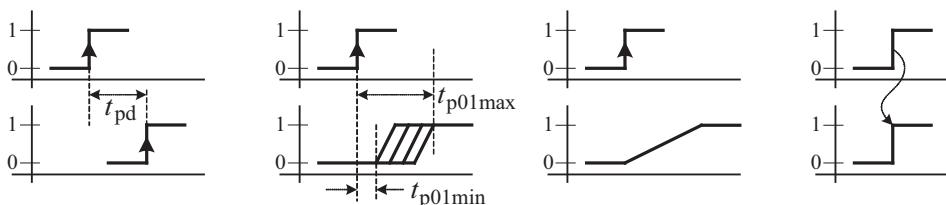

## ■ 1.5 Verarbeitungsgeschwindigkeit

Vorteil einer „einfachen“ digital arbeitenden Schaltung ist die Geschwindigkeit. Aufgrund der hohen Anzahl an (Rechen-)Operationen mit deren Steuerung ergeben sich bei rechnergestützten Anwendungen merkliche Verzögerungen. In diesem Abschnitt wird eine Übersicht gegeben, die die Vorstellung der Verarbeitungsgeschwindigkeit verdeutlicht, ohne zu sehr ins Detail zu gehen.

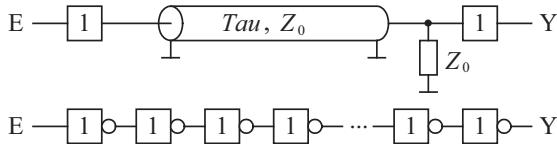

Die höchste Geschwindigkeit, die aus dem Physikunterricht bekannt ist, ist die Lichtgeschwindigkeit  $c$  mit ca. 300 000 km/s. Die Verarbeitungsgeschwindigkeiten bzw. die Reaktionszeiten verarbeitender Systeme werden durch Distanzen repräsentiert, die Licht in diesem Zeitintervall durchläuft. Eine Übersicht zeigt Tabelle 1.4.

**Tabelle 1.4** Gegenüberstellung Zeiteinheit und Strecke (Lichtgeschwindigkeit)

| Strecke (technisch) | Zeiteinheit          | Strecke (Größenordnung)                  |

|---------------------|----------------------|------------------------------------------|

| 300 000 km          | 1 s                  | Größenordnung Erde–Mond (ca. 370 000 km) |

| 30 000 km           | 0,1 s                | Größenordnung Erdumfang (ca. 44 000 km)  |

| 3 000 km            | 0,01 s               | Größenordnung Europa (Nordkap–Sizilien)  |

| 300 km              | 0,001 s = 1 ms       | ca. Luftlinie Hamburg–Frankfurt          |

| 30 km               | 0,1 ms               | (bitte selbst ergänzen)                  |

| 3 km                | 0,01 ms              | (bitte selbst ergänzen)                  |

| 300 m               | 0,001 ms = 1 $\mu$ s | (bitte selbst ergänzen)                  |

| 30 m                | 0,1 $\mu$ s          | ca. Steinwurf                            |

| 3 m                 | 0,01 $\mu$ s         | ca. Deckenhöhe in Schulgebäuden          |

| 0,3 m               | 0,001 $\mu$ s = 1 ns | ca. Länge eines DIN-A4-Blattes           |

Im normalen Tagesablauf reicht eine Zeitauflösung bis in den Sekundenbereich aus. Dies ist eine Größe, die bekannt und dadurch sehr gut vorstellbar ist. Mechanische Systeme haben aufgrund ihrer Trägheit Reaktionszeiten von ms (Millisekunden). Dies ist 1000-mal schneller als eine Sekunde (Verhältnis Millimeter im Vergleich zum Meter).

Normale Rechnersysteme (keine Hochgeschwindigkeitsrechner), die zur Steuerung einfacher Vorgänge verwendet werden, haben Reaktionszeiten von  $\mu$ s (Mikrosekunden). Die auszuführenden Operationen umfassen wenige Rechenschritte. Dies ist 1000-mal schneller als eine Millisekunde (Verhältnis Millimeter im Vergleich zum Meter).

Digitale Verarbeitungseinheiten haben Reaktionszeiten von wenigen Nanosekunden. Es ist 1000-mal schneller als eine Mikrosekunde (Verhältnis Millimeter im Vergleich zum Meter). Bis das Ergebnis einer einfachen Logikverknüpfung bei Standardgattern vorliegt, legt Licht näherungsweise die Strecke einer Schreibtischslänge zurück. Der Vorteil dieser hohen Geschwindigkeit ist ohne technische Hilfsmittel wie Oszilloskope etc. schwer nachvollziehbar. Die Längenangabe bei Lichtgeschwindigkeiten soll hierbei helfen.

# 2

## Logische Verknüpfungen

In diesem Kapitel werden logische Verknüpfungen erläutert. Die verwendeten Signale können nur einen von zwei Zuständen annehmen, die 0 oder 1 sind und gegebenenfalls auch als „falsch“ oder „wahr“ interpretiert werden können. Zwischenwerte gibt es in der binären Darstellung nicht, so ist ein Schalter entweder geschlossen oder offen. Eine Berechnung analoger Signalwerte unter Berücksichtigung von Widerstandswerten etc. entsprechend der analogen Schaltungstechnik entfällt. Hierdurch wird die Beschreibung der Zusammenhänge deutlich einfacher, wodurch sich der enorme Vorteil binär arbeitender Schaltungen ergibt. Aus den Grundelementen, die sehr schnelle Verarbeitungszeiten (Reaktionszeiten) haben, können komplexe Verknüpfungen zusammengesetzt werden bis hin zu den bekannten Rechner-systemen. In einigen Fällen ist es jedoch notwendig, den analogen Charakter der verwendeten Signalgrößen zu betrachten, da sie durch analoge Spannungsübergänge und Laufzeiten auf Leitungen etc. nicht immer vernachlässigbares Störverhalten aufweisen. Die Realisierung digitaler Schaltungen strebt jedoch an, dass diese Effekte in der normalen Anwendung vernachlässigt werden können. Wahrscheinlichkeiten oder Zwischenwerte, wie sie in der statistischen Beschreibung oder der Fuzzy-Logik verwendet werden, gibt es in der binären Darstellung nicht.

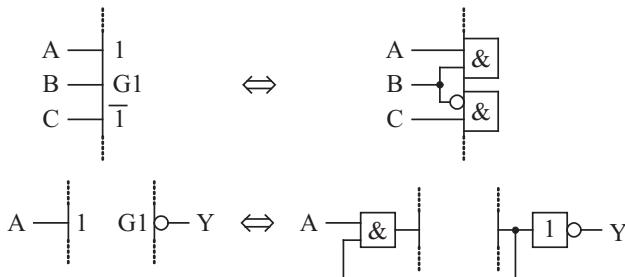

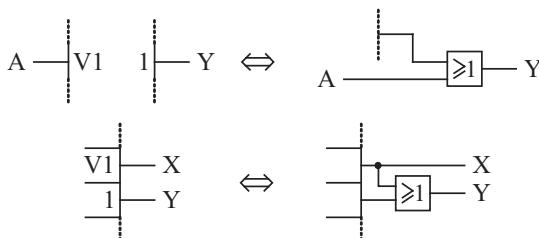

Die Darstellung von Formeln und Symbolen ist in verschiedenen Normen festgelegt. Diese sind u. a.:

DIN 1338 Formelschreibweise und Formelsatz

DIN 5473 Logik und Mengenlehre – Zeichen und Begriffe

DIN EN 60617-7 Graphische Symbole für Schaltpläne – Teil 7: Schaltzeichen für Schalt- und Schutzeinrichtungen

DIN EN 60617-12 Graphische Symbole für Schaltpläne – Teil 12: Binäre Elemente

DIN 66 000 Informationsverarbeitung – Mathematische Zeichen und Symbole der Schalt-algebra

### ■ 2.1 Grundfunktionen und Grundglieder

#### 2.1.1 UND-Verknüpfung

Die Aussage „Wenn es Tag ist und es wolkenlos ist, dann scheint die Sonne“ enthält eine **UND-Verknüpfung**. Die Schlussfolgerung  $z = \text{„Es scheint die Sonne“}$  ist dann und nur dann zutreffend oder wahr, wenn  $a = \text{„Es ist Tag“}$  und  $b = \text{„Es ist wolkenlos“}$  zutreffend ist (beide Aussagen müssen wahr  $\hat{=} 1$  sein). Da in der binären Darstellung nur wahr  $\hat{=} 1$  und falsch  $\hat{=} 0$  existiert, gibt es z. B. den Zustand „teilbewölkt“ nicht.

| $b$ | $a$ | $z$ |

|-----|-----|-----|

| 0   | 0   | 0   |

| 0   | 1   | 0   |

| 1   | 0   | 0   |

| 1   | 1   | 1   |

**Tabelle 2.1** Wahrheitstabelle einer UND-Verknüpfung

Logische Verknüpfungen können in Tabellenform dargestellt werden. Diese Darstellungen heißen **Wahrheitstabelle** oder **Schaltbelegungstabelle**. Bei zwei zu verknüpfenden Aussagen gibt es vier Kombinationsmöglichkeiten  $b : a \in \{0:0; 0:1; 1:0; 1:1\}$ . Tabelle 2.1 zeigt den Zusammenhang in tabellarischer Form.

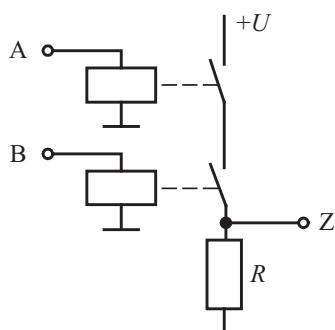

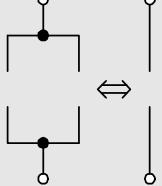

Am Ausgang einer **UND-Verknüpfung** wird nur dann eine 1 ausgegeben, wenn alle Eingänge den Zustand 1 haben. Eine mögliche schaltungstechnische Realisierung ist die Reihenschaltung von Schaltkontakten. Bild 2.1 zeigt beispielhaft eine mögliche Relaisschaltung, die eine UND-Verknüpfung darstellt. Eine grundlegende Realisierung von Logikverknüpfungen durch Schaltkontakte als Basis anwendbarer Rechenregeln wird im nächsten Kapitel vertieft.

Bei einer UND-Verknüpfung (Sprechweise: „ $a$  und  $b$ “) reicht eine 0 an den Eingängen aus, um eine 0 am Ausgang zu erzeugen. Die 0 setzt sich durch.

Am Ausgang Z liegt nur dann der Zustand  $z = 1$  (H-Pegel) an, wenn beide Eingänge A und B die Zustände  $a = b = 1$  (H-Pegel) aufweisen und beide Relais aktiv und dadurch die Schaltkontakte geschlossen sind. In der Darstellung ist berücksichtigt, dass die Großbuchstaben A, B und Z (nicht kursiv geschrieben) den physikalischen Schaltungsknoten (Anschluss bzw. Leitungselement) repräsentieren und die Kleinbuchstaben  $a$ ,  $b$  und  $z$  (kursiv geschrieben) die zugehörigen Logikwerte, die jeweils den Zustand 0 oder 1 annehmen können. Hierbei wird die Zuordnung zwischen Schaltungsknoten und der zugehörigen Variable durch den Buchstaben selbst repräsentiert (z. B.  $a$  ist der Zustand auf Leitung A).

Jede Schaltung, die die Wahrheitstabelle einer UND-Verknüpfung erfüllt, ist ein UND-Glied. Weitere Bezeichnungen sind z. B. **UND-Gatter**, **UND-Element**, **Konjunktion** oder **AND-Glied**.

Eingänge werden, wenn keine andere Randbedingung eine Abweichung erfordert, mit den ersten Buchstaben des Alphabets und Ausgänge mit den letzten Buchstaben des Alphabets gekennzeichnet.

**Bild 2.1** Realisierung einer UND-Verknüpfung mit einer Relaisschaltung

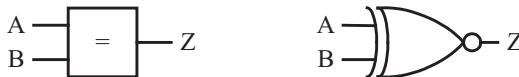

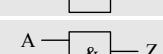

**Bild 2.2** Schaltzeichen für eine UND-Verknüpfung

Gleichung 2.1 zeigt gebräuchliche formelmäßige Darstellungen einer UND-Verknüpfung. Im Weiteren wird das Symbol „ $\wedge$ “ verwendet.

$$z = a \wedge b \quad \text{bzw.} \quad z = a \cdot b \quad \text{bzw.} \quad z = a \& b \quad (2.1)$$

Eine grafische Darstellung der UND-Verknüpfung zeigt Bild 2.2. Diese Symbole dienen zur grafischen Beschreibung. Die linke Darstellung wird im Weiteren verwendet. Die rechte Darstellung ist häufig im englischsprachigen Raum zu finden.

## 2.1.2 ODER-Verknüpfung

Die Aussage „Wenn ich Hunger habe oder wenn ich Durst habe, dann gehe ich in ein Restaurant“ enthält eine **ODER-Verknüpfung**. Die Aussage  $z = \text{„Ich gehe in ein Restaurant“}$  ist dann zutreffend oder wahr, wenn die Aussage  $a = \text{„Ich habe Hunger“}$  oder die Aussage  $b = \text{„Ich habe Durst“}$  zutreffend oder wahr ist. Tabelle 2.2 zeigt diesen Zusammenhang in Form einer Wahrheitstabelle.

| $b$ | $a$ | $z$ |

|-----|-----|-----|

| 0   | 0   | 0   |

| 0   | 1   | 1   |

| 1   | 0   | 1   |

| 1   | 1   | 1   |

**Tabelle 2.2** Wahrheitstabelle einer ODER-Verknüpfung

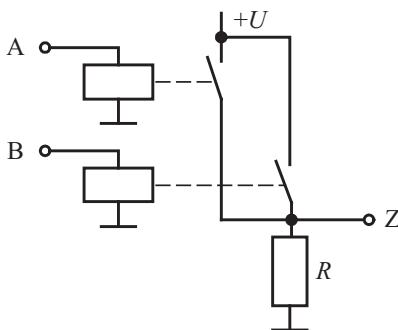

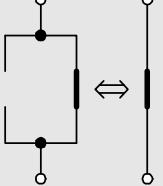

Das Ausgangssignal einer **ODER-Verknüpfung** ist dann 1, wenn eines oder mehrere der Eingänge den Zustand 1 haben, also ein 1-Signal führen. Eine mögliche schaltungstechnische Realisierung mit Relais zeigt Bild 2.3. Das Ausgangssignal  $z$  hat dann ein 1-Signal, wenn eines oder beide Relaiskontakte über die Eingangszustände  $a$  bzw.  $b$  über ein 1-Signal aktiviert und geschlossen sind.

**Bild 2.3** Realisierung einer ODER-Verknüpfung mit einer Relaischaltung

Bei einer ODER-Verknüpfung (Sprechweise: „a oder b“) reicht eine 1 an den Eingängen aus, um eine 1 am Ausgang zu erzeugen. Die 1 setzt sich durch.

Jede Schaltung, die die Wahrheitstabelle einer **ODER-Verknüpfung** erfüllt, ist ein ODER-Glied. Weitere Bezeichnungen sind **ODER-Gatter**, **ODER-Element**, **Disjunktion** oder **OR-Glied**.

Gleichung 2.2 zeigt gebräuchliche formelmäßige Darstellungen einer ODER-Verknüpfung. Im Weiteren wird das Symbol „ $\vee$ “ verwendet.

$$z = a \vee b \quad \text{bzw.} \quad z = a + b \quad \text{bzw.} \quad z = a \# b \quad (2.2)$$

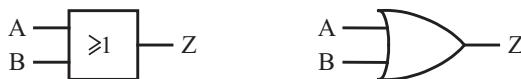

Eine grafische Darstellung der ODER-Verknüpfung zeigt Bild 2.4. Diese Symbole dienen zur grafischen Beschreibung. Die linke Darstellung wird im Weiteren verwendet. Die rechte Darstellung ist häufig im englischsprachigen Raum zu finden.

**Bild 2.4** Schaltzeichen für eine ODER-Verknüpfung

### 2.1.3 NEGATION

Die Aussage „Wenn ich nicht genügend Punkte in der Klausur habe, dann bin ich durch die Prüfung gefallen“ enthält eine **NEGATION**. Die Aussage  $z = \text{„Ich bin durch die Prüfung gefallen“}$  ist dann zutreffend oder wahr, wenn  $a = \text{„Ich habe genügend Punkte in der Klausur“}$  nicht zutrifft bzw. falsch ist. Der Zusammenhang wird in Tabelle 2.3 dargestellt.

| $a$ | $z$ |

|-----|-----|

| 0   | 1   |

| 1   | 0   |

**Tabelle 2.3** Wahrheitstabelle einer NEGATION

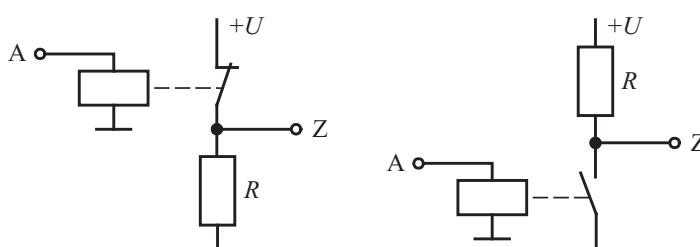

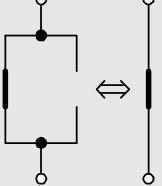

Die NEGATION invertiert den Logikwert, sodass aus einer 1 (wahr) eine 0 (falsch) wird und umgekehrt. Bild 2.5 zeigt mögliche schaltungstechnische Realisierungen.

Bei einer NEGATION (Sprechweise: „nicht a“ bzw. „nicht [...]“) wird der Logikzustand gewechselt (durch eine Negation wird aus einer wahren Aussage (1) eine falsche Aussage (0) und umgekehrt.

**Bild 2.5** Realisierung einer NEGATION

Jede Schaltung, die die Wahrheitstabelle einer **NEGATION** erfüllt, ist ein **NICHT-Glied**. Weitere Bezeichnungen sind **NICHT-Element** oder **NOT-Glied**.

Gleichung 2.3 zeigt gebräuchliche Darstellungen für eine NEGATION. Im Weiteren wird der Überstrich (Negationsstrich) verwendet.

$$z = \overline{a} \quad \text{bzw.} \quad z = \neg a \quad \text{bzw.} \quad z = / a \quad \text{bzw.} \quad z = !a \quad (2.3)$$

Eine grafische Darstellung der NEGATION zeigt Bild 2.6. Die linke Darstellung wird im Weiteren verwendet. Der Negationskreis wird bei der Negation an den Ausgang gezeichnet. Bei komplexeren Symbolen kann er jedoch auch an den Eingängen auftreten. Die rechte Darstellung ist häufig im englischsprachigen Raum zu finden.

**Bild 2.6** Schaltzeichen für eine NEGATION

## 2.1.4 Verstärker

Im Zusammenhang der Grundelemente sei noch der Verstärker erwähnt. Die Logikaus sage des Signals wird dabei nicht verändert. Er wird verwendet, um Signale, die z. B. übertragungsbedingt die Logikpegel nicht mehr sicher repräsentieren können (durch Störeinflüsse „verrauscht“ sind), zu regenerieren. Ein weiterer Punkt ist die eindeutige Datenflussrichtung, da das Eingangssignal das Ausgangssignal beeinflusst aber das Ausgangssignal keine Rückwirkung auf das Eingangssignal hat. Hiermit können Übertragungspunkte (Eingangsverstärker einer Schaltung oder eines IC (Integrated Circuit)) definiert werden.

Gleichung 2.4 zeigt eine übliche Darstellung.

$$z = a \quad (2.4)$$

Eine grafische Darstellung der Verstärkung zeigt Bild 2.7. Die linke Darstellung wird im Weiteren verwendet. Die rechte Darstellung ist häufig im englischsprachigen Raum zu finden. Das nach rechts zeigende Dreiecksymbol wird allgemein auch als Verstärkungssymbol verwendet.

**Bild 2.7** Schaltzeichen für eine Verstärkung

Die Datenflussrichtung ist in dem eigentlichen Symbol nicht zu erkennen. Es ist jedoch allgemein üblich, eine Datenflussrichtung in einem Schaltbild von links-oben nach rechts-unten zu zeichnen (in den bisherigen Darstellungen von links nach rechts). Hieraus ergibt sich die Datenflussrichtung von A nach Z. Ausnahmen bestätigen jedoch manchmal die Regel.

## ■ 2.2 Zusammengesetzte Elemente

### 2.2.1 NAND-Verknüpfung

Die NAND-Verknüpfung ist eine Zusammenschaltung einer UND-Verknüpfung mit einer nachgeschalteten NEGATION (s. Bild 2.8).

**Bild 2.8** Aufbau eines NAND-Gliedes

Tabelle 2.4 zeigt die Wahrheitstabelle einer NAND-Verknüpfung und Gleichung 2.5 die gleichungsmäßige Beschreibung in verschiedenen Darstellungsvarianten. Im Weiteren wird die erste Darstellung verwendet, da hier der Negationsstrich gleichzeitig eine Klammerwirkung über der unter ihm angegebenen Verknüpfung beinhaltet, wodurch sich eine übersichtliche Darstellung ergibt.

| $b$ | $a$ | $z$ |

|-----|-----|-----|

| 0   | 0   | 1   |

| 0   | 1   | 1   |

| 1   | 0   | 1   |

| 1   | 1   | 0   |

**Tabelle 2.4** Wahrheitstabelle einer NAND-Verknüpfung

$$z = \overline{a \wedge b} \quad \text{bzw.} \quad z = a \overline{\wedge} b \quad \text{bzw.} \quad z = a | b \quad \text{bzw.} \quad z = \neg(a \cdot b) \quad (2.5)$$

Bei einer NAND-Verknüpfung (Sprechweise: „ $a$  nand  $b$ “) reicht eine 0 an den Eingängen aus, um eine 1 am Ausgang zu erzeugen. Eine 0 erzwingt die 1.

Eine grafische Darstellung der NAND-Verknüpfung zeigt Bild 2.9. Die linke Darstellung wird im Weiteren verwendet. Die rechte Darstellung ist häufig im englischsprachigen Raum zu finden.

**Bild 2.9** Schaltzeichen für eine NAND-Verknüpfung

### 2.2.2 NOR-Verknüpfung

Die NOR-Verknüpfung ist eine Zusammenschaltung einer ODER-Verknüpfung mit einer nachgeschalteten NEGATION (s. Bild 2.10).

**Bild 2.10** Aufbau eines NOR-Gliedes

| $b$ | $a$ | $z$ |

|-----|-----|-----|

| 0   | 0   | 1   |

| 0   | 1   | 0   |

| 1   | 0   | 0   |

| 1   | 1   | 0   |

**Tabelle 2.5** Wahrheitstabelle einer NOR-Verknüpfung

Tabelle 2.5 zeigt die Wahrheitstabelle einer NOR-Verknüpfung und Gleichung 2.6 die gleichungsmäßige Beschreibung in verschiedenen Darstellungsvarianten. Im Weiteren wird die erste Darstellung verwendet, da hier der Negationsstrich gleichzeitig eine Klammerwirkung über der unter ihm angegebenen Verknüpfung beinhaltet.

$$z = \overline{a \vee b} \quad \text{bzw.} \quad z = a \overline{\vee} b \quad \text{bzw.} \quad z = a \downarrow b \quad \text{bzw.} \quad z = \neg(a + b) \quad (2.6)$$

Bei einer NOR-Verknüpfung (Sprechweise: „ $a$  nor  $b$ “) reicht eine 1 an den Eingängen aus, um eine 0 am Ausgang zu erzeugen. Eine 1 erzwingt die 0.

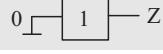

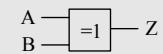

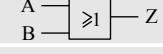

Eine grafische Darstellung der NOR-Verknüpfung zeigt Bild 2.11. Die linke Darstellung wird im Weiteren verwendet. Die rechte Darstellung ist häufig im englischsprachigen Raum zu finden.

**Bild 2.11** Schaltzeichen für eine NOR-Verknüpfung

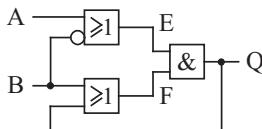

### 2.2.3 ANTIVALENZ-Verknüpfung

Die ANTIVALENZ-Verknüpfung gibt am Ausgang eine 1 aus, wenn beide Eingänge unterschiedliche Logikzustände haben. Das Verhalten zeigt Tabelle 2.6.

| $b$ | $a$ | $z$ |

|-----|-----|-----|

| 0   | 0   | 0   |

| 0   | 1   | 1   |

| 1   | 0   | 1   |

| 1   | 1   | 0   |

**Tabelle 2.6** Wahrheitstabelle einer ANTIVALENZ-Verknüpfung

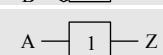

Die ANTIVALENZ-Verknüpfung gilt als eine der Grundverknüpfungen und hat deshalb ein eigenes Symbol. Die mathematische Beschreibung zeigt Gleichung 2.7 und die grafische ist in Bild 2.12 dargestellt.

$$z = a \leftrightarrow b \quad \text{bzw.} \quad z = a \Leftrightarrow b \quad \text{bzw.} \quad z = a \oplus b \quad (2.7)$$

**Bild 2.12** Schaltzeichen für eine ANTIVALENZ-Verknüpfung

Bei einer ANTIVALENZ-Verknüpfung (Sprechweise: „ $a$  xor  $b$ “) wird dann eine 1 ausgegeben, wenn nur einer der beiden Eingänge den Zustand 1 aufweist.

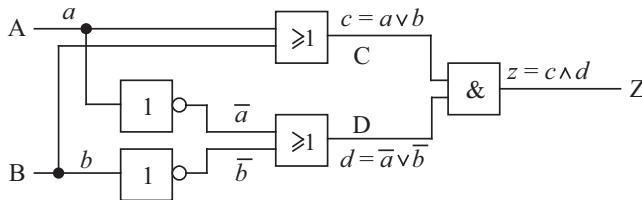

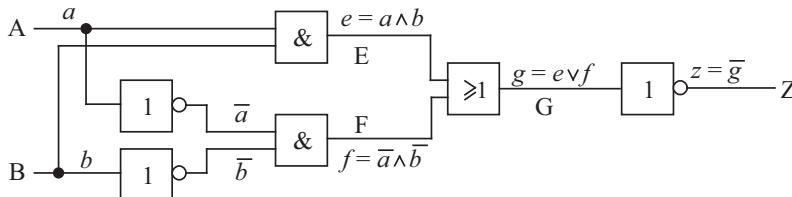

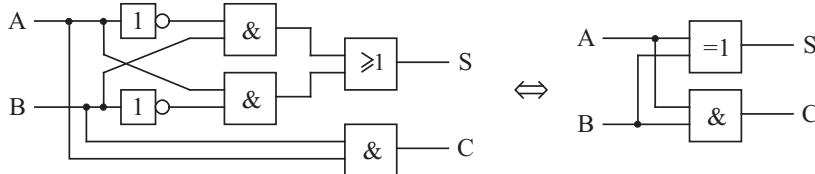

Als elektronisches Grundelement wird diese Verknüpfung aus den bereits bekannten Grundelementen zusammengesetzt. Eine Realisierung zeigt Bild 2.13 und eine weitere Bild 2.14.

**Bild 2.13** Mögliche Realisierung einer Antivalenz-Verknüpfung aus Grundelementen

**Bild 2.14** Eine alternative Realisierung einer Antivalenz-Verknüpfung aus Grundelementen

Die zugehörigen Schaltfunktionen zeigt Gleichung 2.8. Die Gültigkeit kann mithilfe einer Wahrheitstabelle überprüft werden. Für jeden internen Schaltungsknoten wird der Logikwert basierend auf den Eingangssignalen bestimmt. Tabelle 2.7 zeigt diesen Zusammenhang. Es ist zu erkennen, dass beide Schaltungen die ANTIVALENZ-Verknüpfung realisieren.

$$z = c \wedge d = (a \vee b) \wedge (\bar{a} \vee \bar{b}) = \bar{g} = \overline{e \vee f} = \overline{(a \wedge b) \vee (\bar{a} \wedge \bar{b})} \quad (2.8)$$

Andere Bezeichnungen sind ANTIVALENZ-Glied, EXKLUSIVE-ODER-Glied, XOR-Verknüpfung oder EXKLUSIVE-ODER-Verknüpfung.

**Tabelle 2.7** Wahrheitstabelle der Realisierungen einer ÄQUIVALENZ-Verknüpfung

| $b$ | $a$ | $\bar{b}$ | $\bar{a}$ | $c = a \vee b$ | $d = \bar{a} \vee \bar{b}$ | $e = a \wedge b$ | $f = \bar{a} \wedge \bar{b}$ | $g = e \vee f$ | $z = c \wedge d = \bar{g}$ |

|-----|-----|-----------|-----------|----------------|----------------------------|------------------|------------------------------|----------------|----------------------------|

| 0   | 0   | 1         | 1         | 0              | 1                          | 0                | 1                            | 1              | 0                          |

| 0   | 1   | 1         | 0         | 1              | 1                          | 0                | 0                            | 0              | 1                          |

| 1   | 0   | 0         | 1         | 1              | 1                          | 0                | 0                            | 0              | 1                          |

| 1   | 1   | 0         | 0         | 1              | 0                          | 1                | 0                            | 1              | 0                          |

## 2.2.4 ÄQUIVALENZ-Verknüpfung

Die ÄQUIVALENZ-Verknüpfung gibt am Ausgang eine 1 aus, wenn beide Eingänge identische Logikzustände haben. Das Verhalten wird in Tabelle 2.8 in der Wahrheitstabelle angegeben.

| $b$ | $a$ | $z$ |

|-----|-----|-----|

| 0   | 0   | 1   |

| 0   | 1   | 0   |

| 1   | 0   | 0   |

| 1   | 1   | 1   |

**Tabelle 2.8** Wahrheitstabelle einer ÄQUIVALENZ-Verknüpfung

Die ÄQUIVALENZ-Verknüpfung gilt als eine der Grundverknüpfungen und hat deshalb ein eigenes Symbol. Die mathematische Beschreibung zeigt Gleichung 2.9 und die grafische ist in Bild 2.15 dargestellt.

$$z = a \leftrightarrow b \quad \text{bzw.} \quad z = a \Leftrightarrow b \quad \text{bzw.} \quad z = a \odot b \quad \text{bzw.} \quad z = \overline{a \oplus b} \quad (2.9)$$

**Bild 2.15** Schaltzeichen für eine ÄQUIVALENZ-Verknüpfung

Bei einer ÄQUIVALENZ-Verknüpfung (Sprechweise: „ $a$  Doppelpfeil  $b$ “) wird dann eine 1 ausgegeben, wenn alle Eingänge den gleichen Zustand aufweisen.

Als elektronisches Grundelement wird diese Verknüpfung ähnlich der Antivalenz zusammengesetzt. Da ANTIVALENZ- und ÄQUIVALENZ-Verknüpfung invers sind, kann hierfür die Schaltung Bild 2.12 am Ausgang negiert bzw. in der Schaltung aus Bild 2.13 die letzte Negation weggelassen werden.

Weitere Bezeichnungen sind ÄQUIVALENZ-Glied oder XNOR-Verknüpfung.

## 2.2.5 Implikation

Die Implikation beschreibt eine logische Folgebeziehung. Sie beschreibt den Zusammenhang „wenn  $b$ , so  $a$ “ oder „aus  $b$  folgt  $a$ “ bzw. „ $b$  implizit  $a$ “. Ist Aussage  $b$  wahr, so muss Aussage  $a$  ebenfalls wahr sein. Ist dies nicht der Fall, so ist diese Relation falsch. Aussage  $a$  kann jedoch richtig sein, auch wenn  $b$  falsch ist. Die Implikation gibt somit am Ausgang eine 0 (falsch) aus, wenn am ersten Eingang eine 1 (erste Aussage ist richtig) und am zweiten Eingang eine 0 (zweite Aussage ist falsch) anliegt („aus wahr folgt falsch“ ist falsch). Das Verhalten gibt Tabelle 2.9 in der Wahrheitstabelle an.

Die Implikation gilt als eine wichtige Verknüpfung in der Aussagenlogik. Die mathematische Beschreibung zeigt Gleichung 2.10.

$$z = b \rightarrow a \quad \text{bzw.} \quad z = b \Rightarrow a \quad (2.10)$$

| $b$ | $a$ | $z$ |

|-----|-----|-----|

| 0   | 0   | 1   |

| 0   | 1   | 1   |

| 1   | 0   | 0   |

| 1   | 1   | 1   |

**Tabelle 2.9** Wahrheitstabelle der IMPLIKATION

In der Digitaltechnik wird dieser Zusammenhang aus den einfach zu realisierenden Grundelementen ODER und NEGATION entsprechend Gleichung 2.11 zusammengesetzt.

$$z = a \vee \overline{b} \quad (2.11)$$

## 2.2.6 Inhibition

Der Begriff Inhibition bedeutet Hemmung oder Unterdrückung einer Einflussgröße. In der Logik entspricht dies der negierten Implikation. Tabelle 2.10 zeigt diesen Zusammenhang als Wahrheitstabelle und Gleichung 2.12 als mathematische Beschreibung basierend auf der Implikation.

| $b$ | $a$ | $z$ |

|-----|-----|-----|

| 0   | 0   | 0   |

| 0   | 1   | 0   |

| 1   | 0   | 1   |

| 1   | 1   | 0   |

**Tabelle 2.10** Wahrheitstabelle der INHIBITION

$$z = \overline{b \rightarrow a} \quad \text{bzw.} \quad z = \overline{a \vee \overline{b}} \quad \text{bzw.} \quad z = \overline{a} \wedge b \quad (2.12)$$

## 2.2.7 Verknüpfungen bei Gliedern mit zwei Eingängen

Zwei Eingangsvariablen mit binären Signalen können vier Eingangskombinationen repräsentieren (vier Zeilen in der Wahrheitstabelle). Diese vier Kombinationsmöglichkeiten können 16 binäre Ausgangskombinationen aufweisen. Tabelle 2.11 stellt diese Möglichkeiten in einer Übersicht dar.

Es gibt durchaus unterschiedliche Darstellungsmöglichkeiten der Schaltfunktion, sodass die Äquivalenz durch die Gleichung entsprechend Realisierung Bild 2.12 oder Gleichung entsprechend Bild 2.13 repräsentiert werden kann. Ein Vorteil (oder Nachteil) ist, dass einige Zusammenhänge durch unterschiedliche, aber gleich komplexe (gleichwertige) Beschreibungen dargestellt werden können. Ein Beispiel zeigen Gleichung 2.13 bis Gleichung 2.16 bei der gleichungsmäßigen Beschreibung einer XOR-Verknüpfung.

$$z = a \leftrightarrow b = \overline{(a \wedge b) \vee (\overline{a} \wedge \overline{b})} \quad (2.13)$$

$$z = a \leftrightarrow b = (a \vee b) \wedge (\overline{a} \vee \overline{b}) \quad (2.14)$$

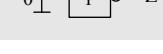

**Tabelle 2.11** Verknüpfungen bei Gliedern mit zwei Eingängen (Übersicht)

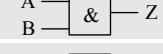

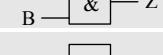

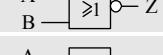

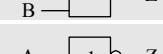

| Wahrheitstabelle<br><i>ba</i><br>00 01 10 11 | Schaltfunktion<br>(Math. Gleichung) | Logische<br>Verknüpfung | Schaltsymbol<br>(Beispiel)                                                           |

|----------------------------------------------|-------------------------------------|-------------------------|--------------------------------------------------------------------------------------|

| 0 0 0 0                                      | $z = 0$                             | Konstante 0<br>(Falsum) |    |

| 0 0 0 1                                      | $z = a \wedge b$                    | $a$ UND $b$             |    |

| 0 0 1 0                                      | $z = \bar{a} \wedge b$              | Inhibition              |    |

| 0 0 1 1                                      | $z = b$                             | Identität $b$           |    |

| 0 1 0 0                                      | $z = a \wedge \bar{b}$              | Inhibition              |    |

| 0 1 0 1                                      | $z = a$                             | Identität $a$           |    |

| 0 1 1 0                                      | $z = a \leftrightarrow b$           | $a$ XOR $b$             |    |

| 0 1 1 1                                      | $z = a \vee b$                      | $a$ ODER $b$            |    |

| 1 0 0 0                                      | $z = \overline{a \vee b}$           | $a$ NOR $b$             |    |

| 1 0 0 1                                      | $z = a \leftrightarrow b$           | $a$ Äquivalent $b$      |   |

| 1 0 1 0                                      | $z = \bar{a}$                       | Nicht $a$               |  |

| 1 0 1 1                                      | $z = \bar{a} \vee b$                | Implikation             |  |

| 1 1 0 0                                      | $z = \bar{b}$                       | Nicht $b$               |  |

| 1 1 0 1                                      | $z = a \vee \bar{b}$                | Implikation             |  |

| 1 1 1 0                                      | $z = \overline{a \wedge b}$         | $a$ NAND $b$            |  |

| 1 1 1 1                                      | $z = 1 = \bar{0}$                   | Konstante 1<br>(Verum)  |  |

$$z = a \leftrightarrow b = (a \wedge \bar{b}) \vee (\bar{a} \wedge b) \quad (2.15)$$

$$z = a \leftrightarrow b = \overline{(a \vee b) \wedge (\bar{a} \vee b)} \quad (2.16)$$

Die Umwandlung von Gleichungen wird in Kapitel 3 und systematisches Vorgehen bei einer Minimierung in Kapitel 4 vertieft.

## 2.2.8 Wichtige Glieder mit mehr als zwei Eingängen

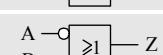

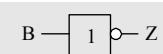

Die elektronischen Grundelemente sind neben der NEGATION die UND- als auch die ODER-Verknüpfung sowie deren Kombinationen zur NAND- und NOR-Verknüpfung. Antivalenz und Äquivalenz werden aus diesen Elementen nachgebildet. In diesem Abschnitt wird das Verhalten aufgezeigt, wenn mehr als 2 Eingänge verwendet werden.

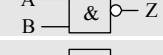

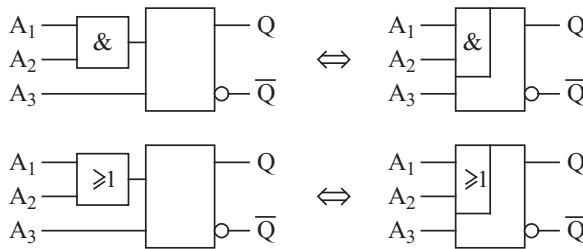

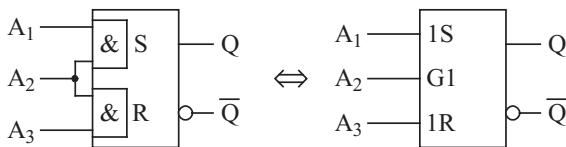

Bei der UND- als auch ODER-Verknüpfung (mit und oder nachfolgender Negation) bleibt weiterhin erhalten, dass eine 0 oder eine 1 in der Ausgangsspalte auftaucht. Die grafische Darstellung zeigt Bild 2.16. Tabelle 2.12 zeigt die Ausgangssignale bei 4 Eingangssignalen.

**Bild 2.16** Schaltzeichen mit vier Eingängen (UND, ODER, NAND, NOR)

**Tabelle 2.12** Verknüpfungen bei Gliedern mit vier Eingängen

| $d \ c \ b \ a$ | & | $\geq 1$ | = | $2k$ | $2k+1$ | $= 2$ | $\geq 2$ |

|-----------------|---|----------|---|------|--------|-------|----------|

| 0 0 0 0         | 0 | 0        | 1 | 1    | 0      | 0     | 0        |

| 0 0 0 1         | 0 | 1        | 0 | 0    | 1      | 0     | 0        |

| 0 0 1 0         | 0 | 1        | 0 | 0    | 1      | 0     | 0        |

| 0 0 1 1         | 0 | 1        | 0 | 1    | 0      | 1     | 1        |

| 0 1 0 0         | 0 | 1        | 0 | 0    | 1      | 0     | 0        |

| 0 1 0 1         | 0 | 1        | 0 | 1    | 0      | 1     | 1        |

| 0 1 1 0         | 0 | 1        | 0 | 1    | 0      | 1     | 1        |

| 0 1 1 1         | 0 | 1        | 0 | 0    | 1      | 0     | 1        |

| 1 0 0 0         | 0 | 1        | 0 | 0    | 1      | 0     | 0        |

| 1 0 0 1         | 0 | 1        | 0 | 1    | 0      | 1     | 1        |

| 1 0 1 0         | 0 | 1        | 0 | 1    | 0      | 1     | 1        |

| 1 0 1 1         | 0 | 1        | 0 | 0    | 1      | 0     | 1        |

| 1 1 0 0         | 0 | 1        | 0 | 1    | 0      | 1     | 1        |

| 1 1 0 1         | 0 | 1        | 0 | 0    | 1      | 0     | 1        |

| 1 1 1 0         | 0 | 1        | 0 | 0    | 1      | 0     | 1        |

| 1 1 1 1         | 1 | 1        | 1 | 1    | 0      | 0     | 1        |

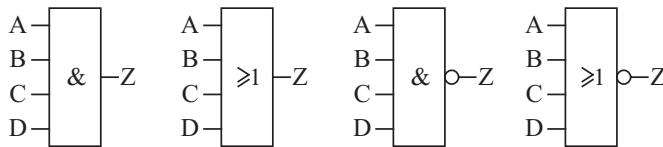

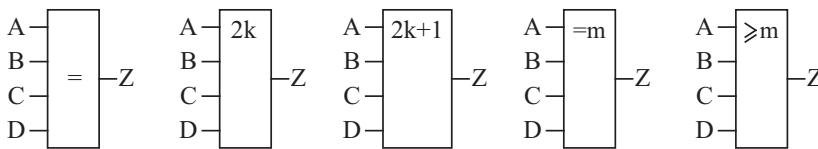

Bei der Äquivalenz müssen bei mehreren Eingängen alle Eingangssignale identisch sein, so dass es nur in der ersten und letzten Zeile der Wahrheitstabelle (mit im Dualcode sortierten Eingangskombinationen) zu einer 1 im generierten Ausgangssignal führt. Dieses Verhalten ist häufig unerwünscht. Der Baustein wird deshalb zu einer Paritätserkennung (GERADE-Element) erweitert. Bei zwei Eingängen entspricht dies der ÄQUIVALENZ-Verknüpfung. Bei mehreren Eingängen wird am Ausgang eine 1 erzeugt, wenn eine gerade Anzahl an 1-Signalen an den Eingängen anliegt, also eine binäre Addition (duale Addition ohne Übertrag) eine 0 liefert. Das Symbol hat die Kennzeichnung  $2k$  und wird in Bild 2.17 dargestellt. Das Verhalten beschreibt Tabelle 2.12.

Die Antivalenz wird ähnlich erweitert und man erhält eine Imparitätserkennung (UNGERADE-Element, Modulo-2-Element). Das Ausgangssignal liefert eine 1, wenn die Anzahl der an den

**Bild 2.17** Weitere Schaltzeichen mit vier Eingängen (Äquivalenz-, Gerade-, Ungerade-, m-aus-n-, Schwellwert-Element)

Eingängen anliegenden 1-Signale ungerade ist, also die binäre Addition aller Eingangssignale eine 1 liefert. Das Symbol hat die Kennung  $2k+1$  und wird in Bild 2.17 dargestellt. Das Verhalten beschreibt Tabelle 2.12.

Eine andere Erweiterung der Antivalenz ist die Bezeichnung „ $= m$ “ und führt zu dem  $m$ -aus- $n$ -Element (mit  $n$  Eingangsanschlüssen). Liegt genau die Anzahl an 1-Signalen an, wie in dem Symbol mit  $m$  angegeben ist, so führt das Ausgangssignal ein 1-Signal. Bei allen anderen Kombinationen ist das Ausgangssignal 0. Tabelle 2.12 zeigt ein Beispiel für  $m = 2$ .

Eine weitere Erweiterung der ODER-Verknüpfung ist das Schwellwert-Element. Verwendet man mehrere Eingänge, so ist das Ausgangssignal 1, wenn die Anzahl der an den Eingängen anliegenden 1-Signale größer oder gleich der im Symbol „ $\geq m$ “ angegebenen Anzahl  $m$  ist. Dabei ist  $m$  immer kleiner als die Anzahl der Eingangsanschlüsse  $n$ . Für  $m = 1$  erhält man das Symbol  $\geq 1$  und somit die Beschreibung der bekannten ODER-Verknüpfung mit zwei Eingängen. Tabelle 2.12 zeigt ein Beispiel für  $m = 2$ .

## ■ 2.3 Schaltungsanalyse

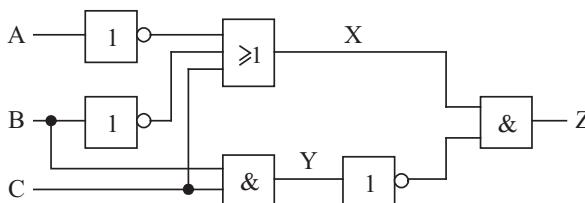

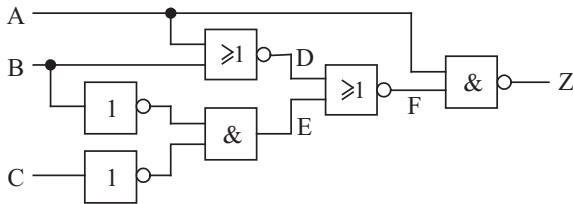

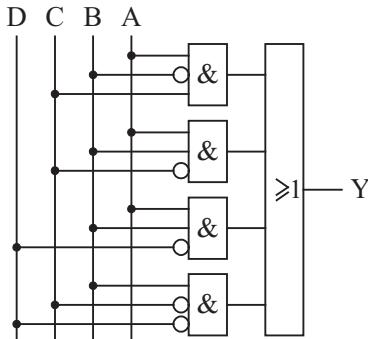

Bei der Schaltungsanalyse ist die Schaltung als Verknüpfung von Logikelementen gegeben. Die Aufgabe besteht darin, eine mathematische Beschreibung des Verhaltens zu ermitteln. Bild 2.18 zeigt z. B. eine Schaltung, deren Verhalten ermittelt werden soll.

**Bild 2.18** Digitale Verknüpfung

Eine Möglichkeit besteht darin, die Struktur der Schaltung durch die Gleichung auszudrücken, wie es auch schon bei der Antivalenzschaltung angewendet wurde. Gleichung 2.17 bestimmt die Gleichung aus der Topologie.

$$z = x \wedge \bar{y} = (\bar{a} \vee \bar{b} \vee c) \wedge \bar{b} \wedge c \quad (2.17)$$

Es ist auch möglich, das Verhalten mithilfe einer Wahrheitstabelle zu bestimmen, um somit eine äquivalente Schaltungsbeschreibung zu erhalten, die das Verhalten der Schaltung

**Tabelle 2.13** Verhaltensanalyse der Schaltung aus Bild 2.17

| $c$ | $b$ | $a$ | $\bar{c}$ | $\bar{b}$ | $\bar{a}$ | $x$ | $y$ | $\bar{y}$ | $z$ |

|-----|-----|-----|-----------|-----------|-----------|-----|-----|-----------|-----|

| 0   | 0   | 0   | 1         | 1         | 1         | 1   | 0   | 1         | 1   |

| 0   | 0   | 1   | 1         | 1         | 0         | 1   | 0   | 1         | 1   |

| 0   | 1   | 0   | 1         | 0         | 1         | 1   | 0   | 1         | 1   |

| 0   | 1   | 1   | 1         | 0         | 0         | 0   | 0   | 1         | 0   |

| 1   | 0   | 0   | 0         | 1         | 1         | 1   | 0   | 1         | 1   |

| 1   | 0   | 1   | 0         | 1         | 0         | 1   | 0   | 1         | 1   |

| 1   | 1   | 0   | 0         | 0         | 1         | 1   | 1   | 0         | 0   |

| 1   | 1   | 1   | 0         | 0         | 0         | 1   | 1   | 0         | 0   |

wiedergibt, aber nicht die Topologie. Tabelle 2.13 demonstriert das Vorgehen. Es werden drei Eingangsvariablen verwendet und somit sind  $2^3 = 8$  Eingangskombinationen möglich. Die Kombinationen sind unabhängig, lediglich zur besseren Übersicht sind sie entsprechend des Dualcodes sortiert. Da einige Eingangsgrößen negiert verwendet werden, sind alle Eingangsgrößen in der negierten Form aufgeführt. Die Zwischengröße  $x$  ist die ODER-Verknüpfung der Größen  $\bar{a}, \bar{b}$  und  $c$ . Es bietet sich an, entsprechend des Zusammenhangs der ODER-Verknüpfung (die 1en setzen sich durch) die von jedem verwendeten Eingang erzeugten 1en in die Spalte  $x$  einzutragen und anschließend die freien Plätze mit den 0en aufzufüllen. So erhält man die Zwischengröße  $x$ . Die Zwischengröße  $y$  ist die UND-Verknüpfung der Größen  $b$  und  $c$ . Es empfiehlt sich entsprechend des Zusammenhangs der UND-Verknüpfung (die 0en setzen sich durch) die von jedem verwendeten Eingang erzeugten 0en in die Spalte  $y$  einzutragen und anschließend die freien Plätze mit den 1en aufzufüllen. Dieses Signal wird invertiert und man erhält damit die Zwischengröße  $\bar{y}$ . Das Ausgangssignal ist die UND-Verknüpfung der Zwischengrößen  $x$  und  $\bar{y}$ . Ergänzt man die Spalte  $z$ , so erhält man das Verhalten der Schaltung.

Das Verhalten der so ermittelten Wahrheitstabelle kann z. B. in der in Gleichung 2.18 angegebenen zwei Formen gleichungsmäßig beschrieben werden.

$$z = \overline{(a \wedge b \wedge \bar{c}) \vee (\bar{a} \wedge b \wedge c) \vee (a \wedge b \wedge c)} = \bar{b} \vee (\bar{a} \wedge \bar{c}) \quad (2.18)$$

Somit ist das Verhalten der Schaltung in diesem Beispiel bereits durch drei Gleichungen (eine Beschreibungsform in Gleichung 2.17 und zwei Formen in Gleichung 2.18) definiert worden. Je nach Vorgehen können sich unterschiedliche Gleichungen ergeben. In Kapitel 3 werden grundlegende Rechenregeln behandelt, mit denen in Kapitel 4 ein strukturiertes Vorgehen bei der Bestimmung der günstigsten (kürzesten) Gleichung demonstriert und geübt wird.

## ■ 2.4 Aufgaben

1. Kontrollieren Sie mithilfe der Wahrheitstabelle die Gültigkeit der Gleichungen 2.13 bis 2.16 für die Realisierung einer XOR-Verknüpfung.

2. Überprüfen Sie mithilfe der Wahrheitstabelle die Äquivalenz der in Gleichung 2.17 und in Gleichung 2.18 angegebenen Verknüpfungen (drei Beschreibungen).

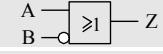

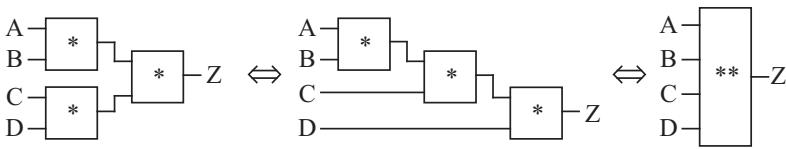

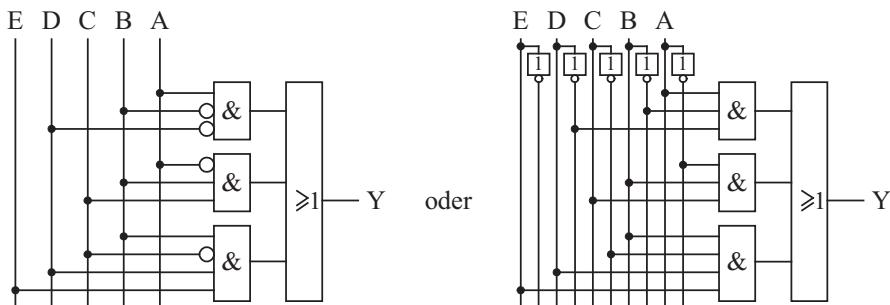

**Bild 2.19** Digitale Verknüpfungsstrukturen

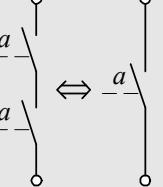

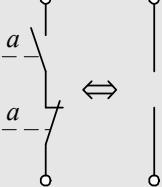

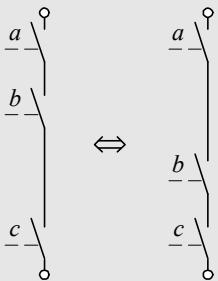

- Überprüfen Sie mithilfe der Wahrheitstabelle die Behauptung der in Bild 2.19 angegebenen Topologie der Verknüpfungselemente für UND-Verknüpfungen („\*“ entspricht „&“ entspricht „\*\*“).

- Überprüfen Sie den in Aufgabe 3 verifizierten Zusammenhang für NAND-Verknüpfungen.

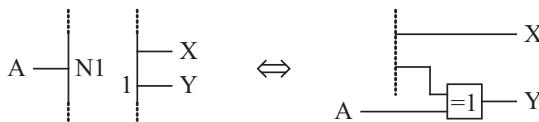

- Welche Verknüpfung liefert die in Bild 2.19 angegebene Topologie, wenn „\*“ eine XOR-Verknüpfung repräsentiert („\*“ entspricht „= 1“). Bestimmen Sie das Element, das mit „\*\*“ gekennzeichnet ist.

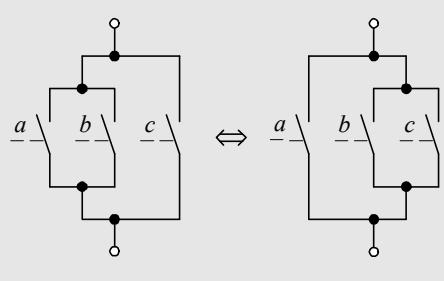

- Lässt sich das in Bild 2.19 mit „\*\*“ gekennzeichnete Element auch für ÄQUIVALENZ-Verknüpfungen („\*“ entspricht „=“) bestimmen?

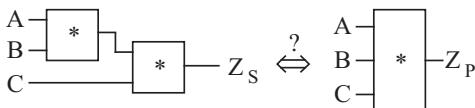

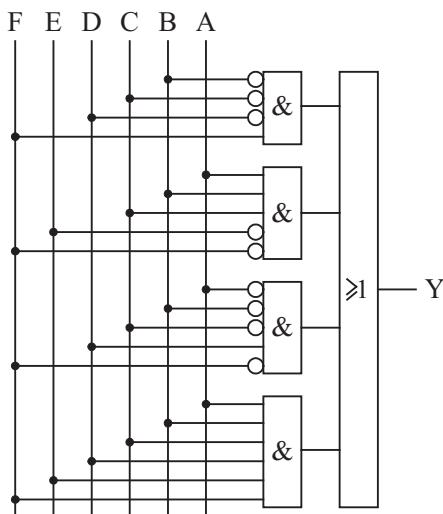

- Vergleichen Sie das Verhalten der in Bild 2.20 angegebenen Topologie für die Verknüpfung „= 1“ („\*“ entspricht „= 1“) und die Verknüpfung „=“ („\*“ entspricht „=“).

**Bild 2.20** Digitale Verknüpfungsstrukturen

# 3

## Schaltalgebra

In diesem Kapitel werden die Grundlagen der Schaltalgebra beschrieben. Es ist die formale Darstellung logischer Verknüpfungen. Hiermit lassen sich die Zusammenhänge darstellen und vereinfachen.

Erste Verknüpfungen der mathematischen Aussagenlogik gehen zurück auf Sokrates, Platon und Aristoteles (500–300 v. Chr.). Wichtige Vorarbeiten zur Algebra der Logik lieferte u. a. William Hamilton (schott. Philosoph und Logiker, 1788–1856). Eine geschlossene Darstellung logischer Probleme in algebraischer Form entwickelte George Boole (brit. Mathematiker und Logiker, 1815–1864). Er drückte logische Begriffe durch mathematische Symbole aus und wendete algebraische Gesetze an. Die hieraus entstandene **Boolesche Algebra** ist eine Mengenalgebra. Eine Untergruppe, die **Schaltalgebra**, dient zur Beschreibung und Optimierung von Schaltungen.

Weiterentwicklungen erfolgten von Augustus De Morgan (engl. Mathematiker, 1806–1871) durch die nach ihm benannten Gesetze zur Umwandlung von UND-Verknüpfungen in ODER-Verknüpfungen und umgekehrt. Weiterentwickelt wurde das Gesetz von Claude Shannon (US-amerikanischer Mathematiker, 1916–2001). Ursprünglich diente es zur Analyse und Minimierung von Relaischaltungen und wird inzwischen zur formalen Beschreibung und Umformung von Schaltnetzen verwendet.

### ■ 3.1 Variable und Konstante

Die Schaltalgebra basiert auf der Darstellung binärer Größen. Es gibt somit nur zwei Werte, den Wert 1 und den Wert 0. Eine **Konstante** repräsentiert diesen Wert unabhängig von irgendwelchen Einflussgrößen. Eine **Schaltvariable** oder **logische Variable** ist von Eingangsgrößen abhängig und repräsentiert je nach Randbedingung den Wert 1 oder den Wert 0. Den Werten können Aussagen zugeordnet werden wie „fährt Fahrrad“ oder „hat Urlaub“. Bei einer 1 ist die Aussage wahr bzw. zutreffend. Bei einer 0 ist die Aussage falsch bzw. nicht zutreffend. Zwischenwerte gibt es aufgrund der binären Darstellung nicht. Zur Darstellung der Variable werden Buchstaben verwendet ( $a, b, c, \dots$ ). Hierbei beschreiben Kleinbuchstaben (kursiv geschrieben) den Logikzustand der Variable. In einer schaltungstechnischen Realisierung sind diese Logikwerte auf Leitungen, auch Knoten genannt, vorhanden, die mit dem entsprechenden Großbuchstaben (nicht kursiv) gekennzeichnet sind (A, B, C,  $\dots$ ).

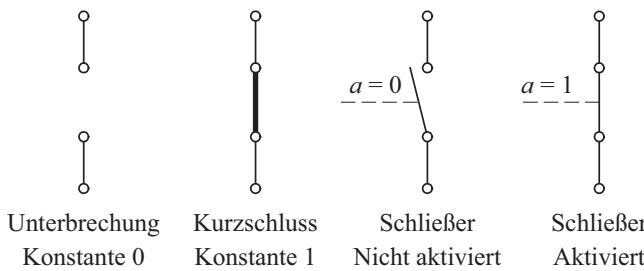

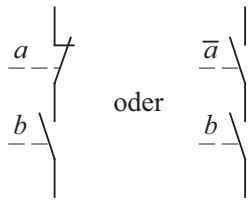

Zur Beschreibung des Verhaltens bedient man sich mechanischer Schaltkontakte (z. B. Relaiskontakte). Wie bei der Zuordnung einer positiven ( $1 \doteq H$ ,  $0 \doteq L$ ) oder negativen Logik ( $1 \doteq L$ ,  $0 \doteq H$ ) könnte man auch hier eine andere Zuordnung festlegen. Es wird bei dieser Zuordnung die Leitfähigkeit eines Netzwerkes mit (Relais-)Kontakten verwendet. Das Netzwerk kann z. B.

eine Unterbrechung aufweisen („Unterbrechung“ entspricht 0) oder einen Strompfad („Kurzschluss“ entspricht 1).

Ein offener Kontakt oder eine offene Verbindung repräsentiert den Wert 0 und ein geschlossener Kontakt oder eine geschlossene Verbindung den Wert 1.

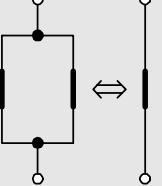

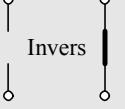

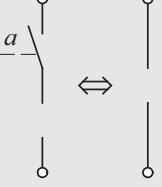

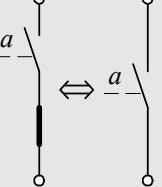

Die Konstante mit dem Wert 1 (Verum) stellt einen immer geschlossenen Schaltkontakt (Kurzschluss) und mit dem Wert 0 (Falsum) einen immer vorhandenen offenen Schaltkontakt (Unterbrechung) dar. Diese Beschreibung eignet sich zur anschaulichen Darstellung von einfachen Logikverknüpfungen. Bild 3.1 zeigt die binären Konstanten und logischen Variablen mit den beiden Zuständen in der Kontakt- oder Schalterdarstellung.

**Bild 3.1** Darstellung von logischen Konstanten und Variablen durch Schaltkontakte

## ■ 3.2 Rechenregeln

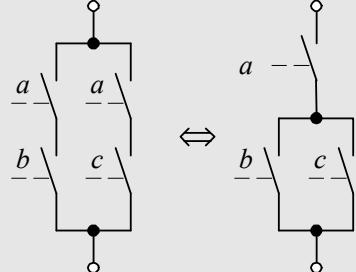

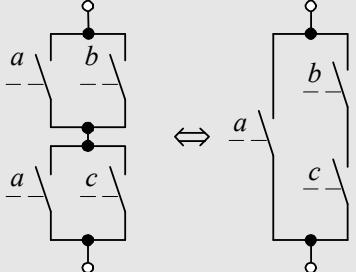

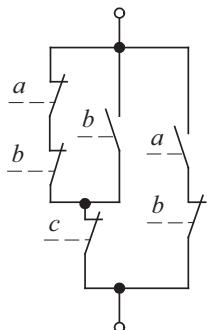

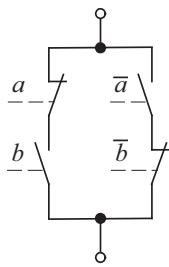

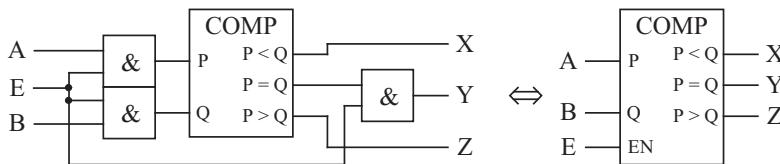

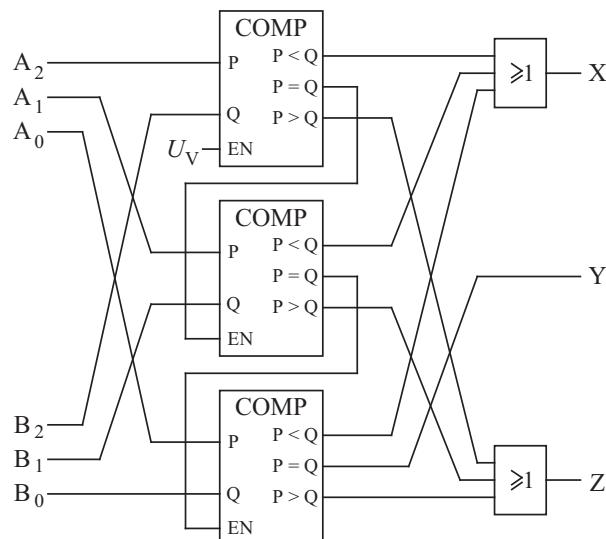

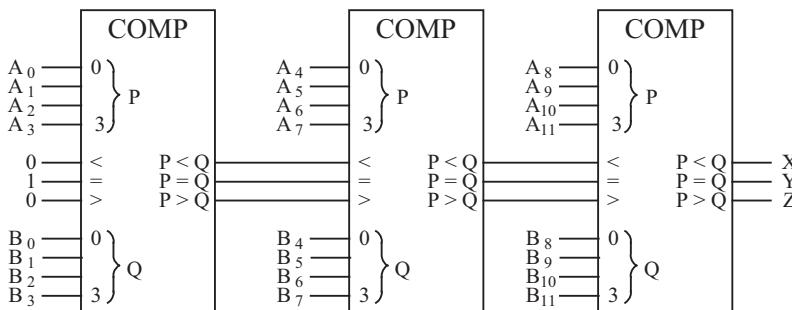

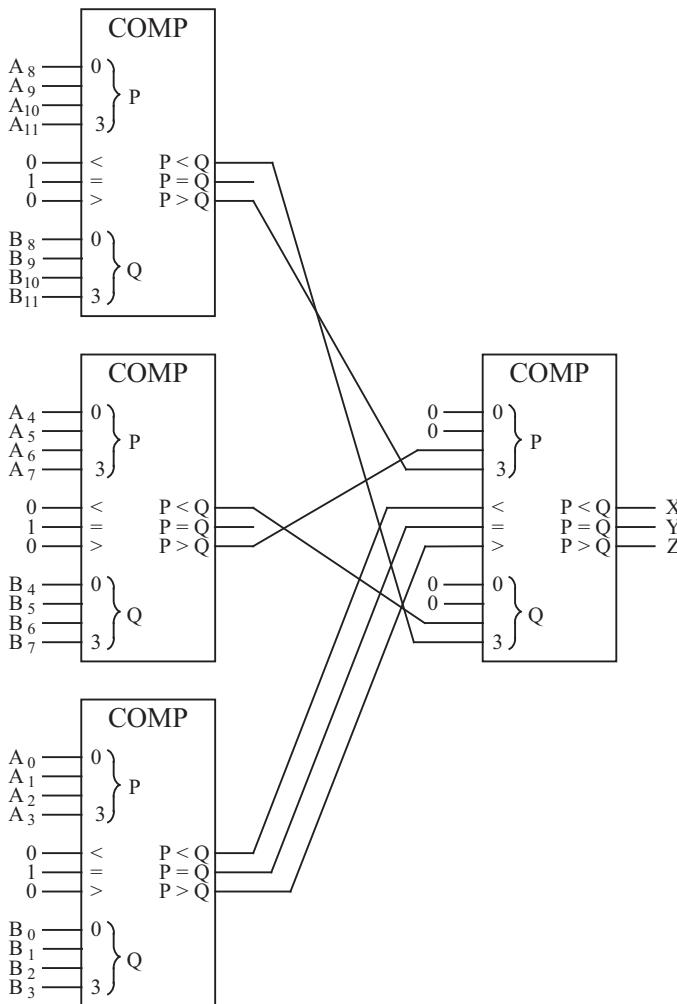

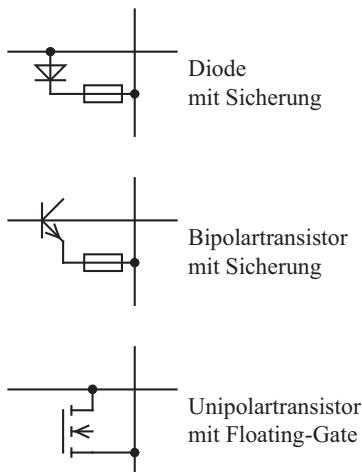

### 3.2.1 Postulate