# Elektrik/Elektronik-Architekturen im Kraftfahrzeug

Thilo Streichert · Matthias Traub

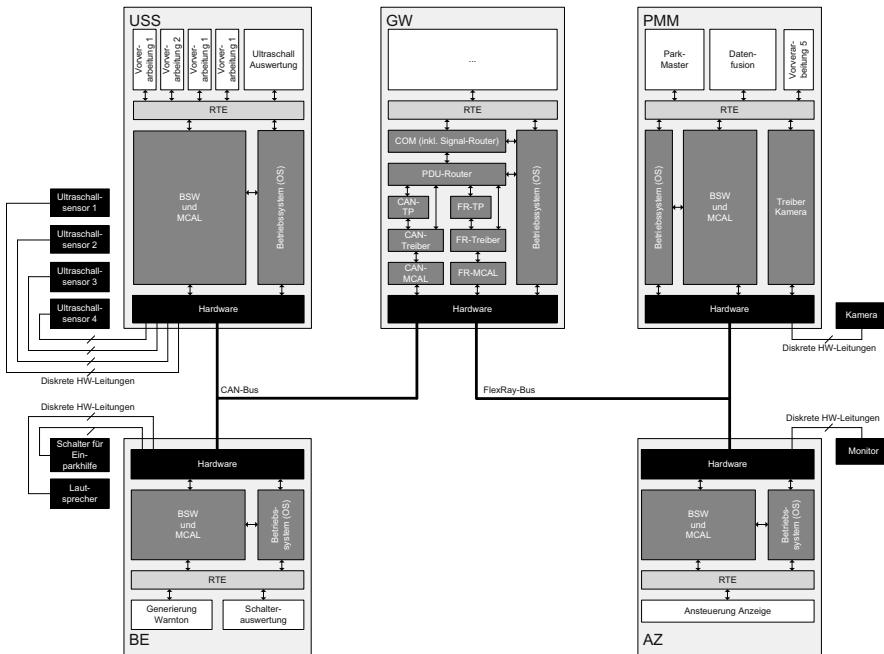

# Elektrik/Elektronik- Architekturen im Kraftfahrzeug

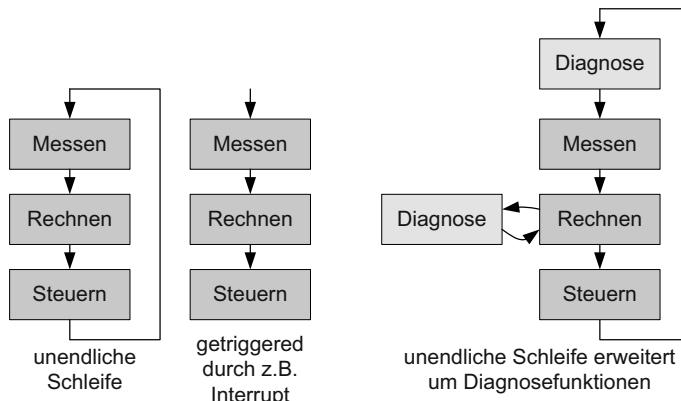

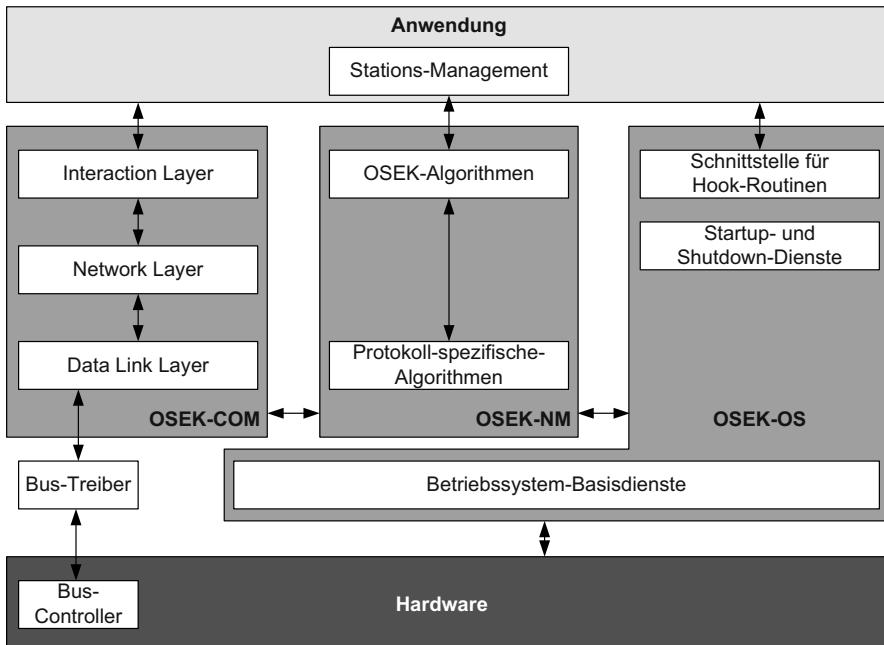

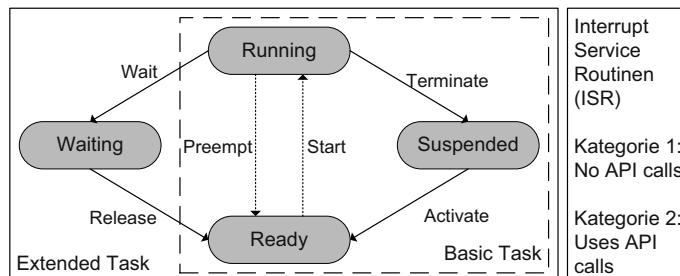

Modellierung und Bewertung

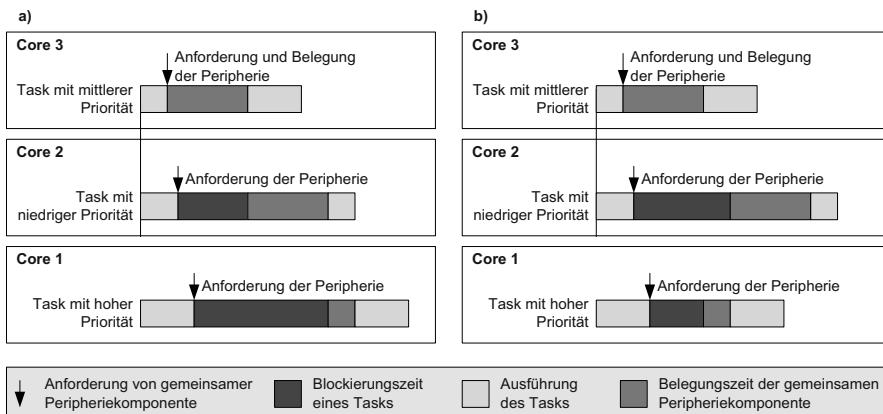

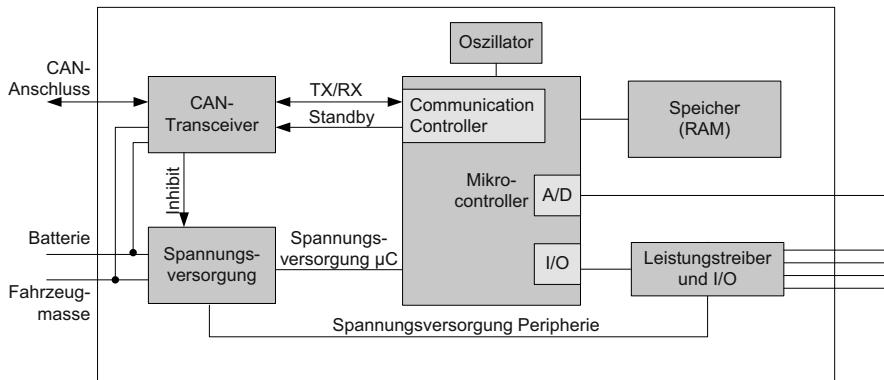

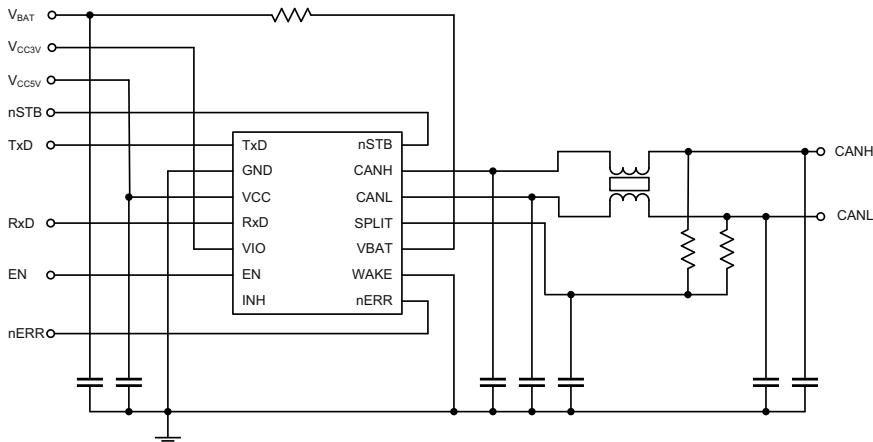

von Echtzeitsystemen

Springer Vieweg

Thilo Streichert

Stuttgart

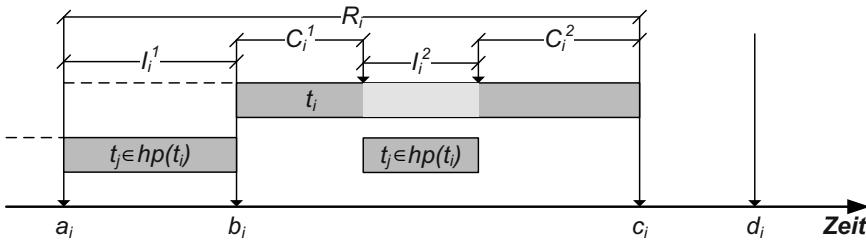

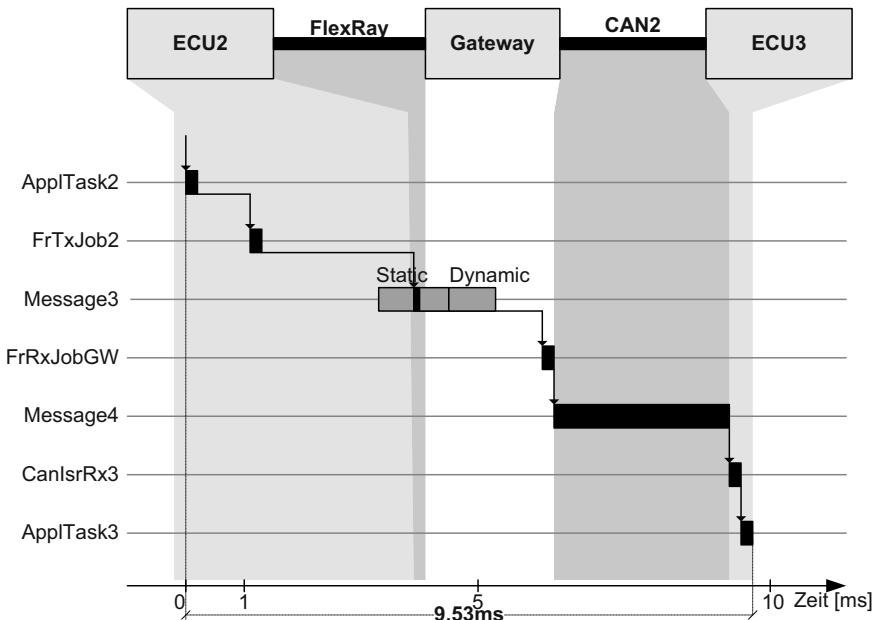

Deutschland

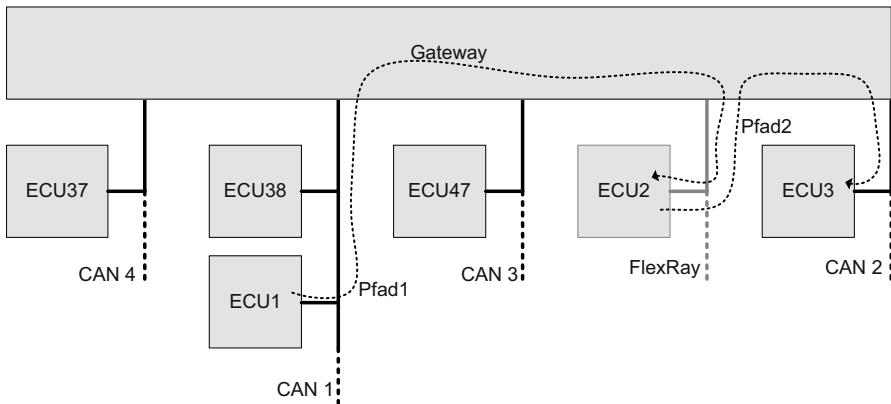

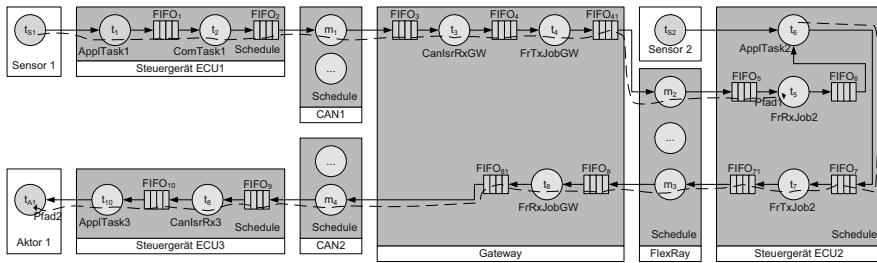

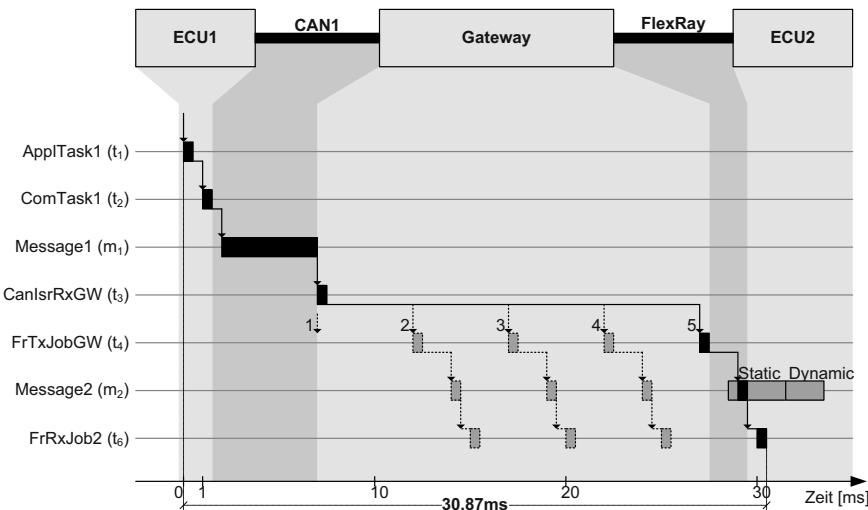

Matthias Traub

München

Deutschland

ISBN 978-3-642-25477-2

DOI 10.1007/978-3-642-25478-9

ISBN 978-3-642-25478-9 (eBook)

Die Deutsche Nationalbibliothek verzeichnetet diese Publikation in der Deutschen Nationalbibliografie; detaillierte bibliografische Daten sind im Internet über <http://dnb.d-nb.de> abrufbar.

Springer Vieweg

© Springer-Verlag Berlin Heidelberg 2012

Das Werk einschließlich aller seiner Teile ist urheberrechtlich geschützt. Jede Verwertung, die nicht ausdrücklich vom Urheberrechtsgesetz zugelassen ist, bedarf der vorherigen Zustimmung des Verlags. Das gilt insbesondere für Vervielfältigungen, Bearbeitungen, Übersetzungen, Mikroverfilmungen und die Einspeicherung und Verarbeitung in elektronischen Systemen.

Die Wiedergabe von Gebrauchsnamen, Handelsnamen, Warenbezeichnungen usw. in diesem Werk berechtigt auch ohne besondere Kennzeichnung nicht zu der Annahme, dass solche Namen im Sinne der Warenzeichen- und Markenschutz-Gesetzgebung als frei zu betrachten wären und daher von jedermann benutzt werden dürften. frei zu betrachten wären und daher von jedermann benutzt werden dürften.

Gedruckt auf säurefreiem Papier

Springer Vieweg ist eine Marke von Springer DE. Springer DE ist Teil der Fachverlagsgruppe Springer Science+Business Media

[www.springer-vieweg.de](http://www.springer-vieweg.de)

# Vorwort

Dieses Buch behandelt das Thema *Elektrik/Elektronik-Architekturen im Kraftfahrzeug*. Der Fokus liegt dabei auf der *Modellierung und Bewertung von Echtzeitsystemen*, die in der Automotive-Elektronik zum Einsatz kommen. In dem Titel des Buches stecken implizit einige Themenkomplexe, die auf einen Satz kondensiert sind. Fangen wir mit der *Modellierung* an: Unter Modellierung verstehen wir allgemein wie man auf strukturierte Art und Weise von einer Idee zu einer Implementierung gelangt. Hierbei helfen Methoden und Werkzeuge, die den Entwurf unterstützen und Entwurfsergebnisse konsistent dokumentieren. In diesem Zusammenhang geht dieses Buch auf die Entwurfsprozesse sowie Kooperationsmodelle mit Zulieferern, anderen Automobilherstellern, der Gesetzgebung und akademischen Einrichtungen ein.

Innerhalb eines Entwurfsprozesses gibt es immer wieder Phasen, in denen überprüft werden muss, ob die Idee, das Konzept oder die Umsetzung das erfüllen, was ursprünglich gefordert wurde. Aus diesem Grund taucht der Begriff *Bewertung* in dem Titel des Buchs auf. Hierbei sind mehrere Interpretationsmöglichkeiten denkbar: Einerseits soll eine Idee oder ein Konzept hinsichtlich bestimmter Optimierungskriterien wie Systemkosten, Gewicht, Leistungsaufnahme oder anderer Größen analysiert werden. Andererseits kann auch die Funktionstüchtigkeit bewertet werden – also ob ein bestimmtes Eingangsereignis für ein System eine bestimmte Reaktion auslöst. Neben dieser funktionalen Bewertung spielt die zeitliche Analyse eine wichtige Rolle, da eine Reaktion nicht zu einem beliebigen Zeitpunkt kommen darf, sondern in einem gewissen Zeitintervall. Die zeitliche Analyse von Elektrik/Elektronik-Architekturen im Kraftfahrzeug ist nur partiell behandelt worden. Das zeitliche Verhalten eines Systems ist aber aus Sicht eines Kunden eine erlebbare Eigenschaft. Deshalb setzt dieses Buch einen Schwerpunkt auf die zeitliche Analyse. Der Fokus liegt dabei sowohl auf dem zeitlichen Verhalten von einzelnen Komponenten und Netzwerken als auch auf den verteilten eingebetteten Systemen.

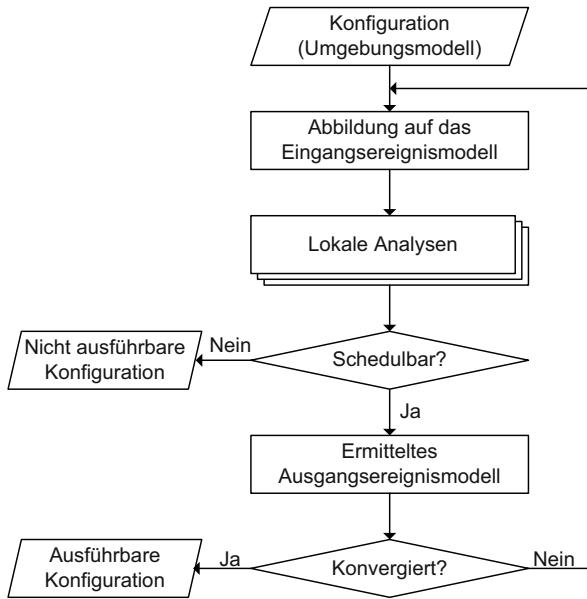

Was in welcher Phase eines Entwurfsprozesses analysierbar ist, stellt oft die eigentliche Herausforderung dar. Häufig liegen in frühen Entwurfsphasen viele Informationen bislang noch nicht vor, um eine präzise Aussage über die Güte, die

Funktionsfähigkeit oder das zeitliche Verhalten zu treffen. Somit muss eine Analyse im Entwurfsprozess wiederholt ausgeführt und iterativ verfeinert werden sowie eine fortlaufende Dokumentation der zeitlichen Eigenschaften der Systeme erfolgen. Diese Informationen können dann bei einer Neuentwicklung als initiale Daten dienen.

In diesem Buch haben wir den Fokus auf die Modellierung und die Bewertung im Bereich der Elektrik/Elektronik-Architekturen im Kraftfahrzeug gelegt. Dies ist nicht nur eine Einschränkung auf den Bereich der Automobilelektronik, sondern auch auf den Bereich der fahrzeuginternen Umsetzung. Hierunter verstehen wir die Komponenten (Steuergeräte) und die Bussysteme, die im Fahrzeug verbaut sind. Die Kommunikationsverbindungen, welche über die Grenzen eines Fahrzeugs hinweggehen, nehmen im Zusammenhang mit Diagnosefunktionen, Internet im Fahrzeug, Integration von Consumer Electronic oder Car-to-X einen immer größeren Stellenwert ein, sind aber einer anderen Netzwerkklasse zuzuordnen als das klassische fahrzeuginterne Netzwerk. Während das klassische Netzwerk statisch während des Entwurfsprozess definiert wird, unterliegt die Kommunikation mit der Außenwelt einer gewissen Veränderung. Es handelt sich also um ein dynamisches Netzwerk, bei dem Verbindungen zu beliebigen Zeitpunkten aufgebaut und unterbrochen werden können. Im Kontext der internen Vernetzung werden in diesem Buch Abstraktionsebenen und Besonderheiten von Architekturen im Kraftfahrzeug vorgestellt. Aus den Abstraktionsebenen geht ein formales Modell hervor, das in den folgenden Kapiteln anschaulich beschrieben wird.

Das Buch gibt eine Einführung in die beschriebene Thematik. Es wird dabei zunächst der etablierte technische Stand der E/E-Entwicklung aufgezeigt und darüber hinaus Methoden zur zeitlichen Bewertung von Echtzeitsystemen im Kraftfahrzeug erläutert. Diese Methoden befinden sich teilweise in der Integration in den Entwurfsfluss der E/E-Entwicklung und sind teilweise noch Forschungsgegenstand. Das Buch richtet sich an folgende Gruppe interessierter Leser:

- Für Leser, die sich bereits bestens im Bereich der E/E-Architekturen auskennen, sind die vertiefenden Kapitel zur zeitlichen Bewertung von Software, Komponenten oder ganzen Netzwerken interessant.

- Leser, die an der Einführung in das Themengebiet der E/E-Architekturen interessiert sind, erhalten in den ersten Kapiteln einen guten Überblick.

- Gleiches gilt für Studierende der Elektrotechnik, Informatik oder verwandter Fachrichtungen. Für diese Zielgruppe schafft das Buch eine Verbindung zwischen den einzelnen Fachvorlesungen wie zum Beispiel zu Betriebssystemen zu Kommunikationssystemen und zu vernetzten eingebetteten Systemen. In diesem Kontext stellt das vorliegende Buch die Zusammenhänge der einzelnen Disziplinen dar und zeigt deren Einsatz im Umfeld der Elektrik/Elektronik im Kraftfahrzeug auf.

Das Buch gliedert sich in die folgenden Kapitel: Das erste Kapitel stellt eine Einleitung in die Automobilwelt dar. Es zeigt die Ebenen der Wertschöpfungskette auf und geht auf die Organisationsstrukturen der Hersteller ein. Weiterhin werden der Entwicklungsprozess, die Zusammenarbeit mit externen Partnern und die histo-

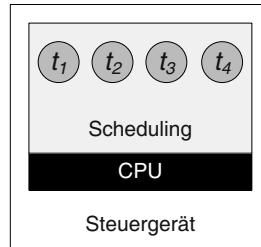

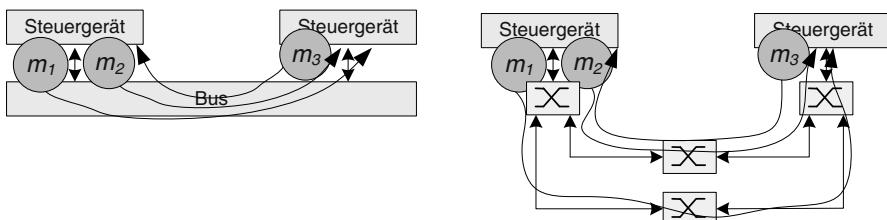

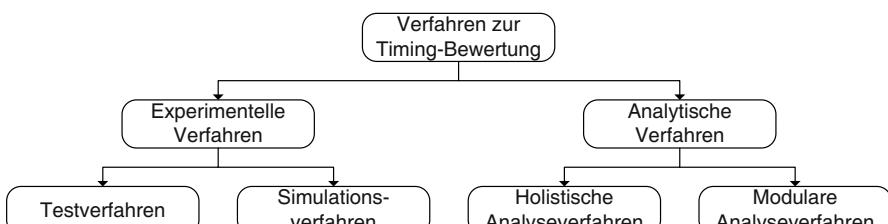

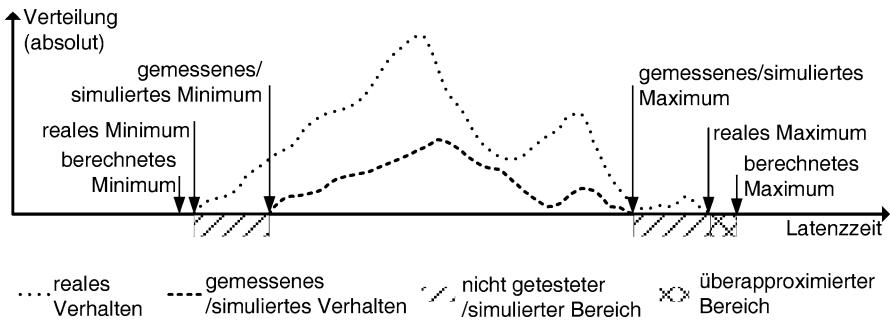

rische Entwicklung der Elektronik im Kraftfahrzeug beleuchtet. Im zweiten Kapitel erfolgt eine Einführung in das Themengebiet der E/E-Architekturen im Kraftfahrzeug. Es werden die einzelnen Abstraktionsebenen einer solchen Elektrik/Elektronik-Architektur beschrieben. Ferner erfolgt eine Vorstellung verschiedener Architekturnalternativen, und es wird eine Übersicht über die hierfür anwendbaren Bewertungsmöglichkeiten gegeben. Anschließend geht Kap. 3 auf die im Kraftfahrzeug zum Einsatz kommende Software-Architektur und deren Entwicklungsprozess ein. Hierzu gehören die Betriebssysteme und verschiedenen Standards, wie z. B. OSEK und AUTOSAR. In Kap. 4 erfolgt eine Einführung in das Thema Steuergeräte und Echtzeit-Rechnerstrukturen. Der Fokus liegt dabei auf dem prinzipiellen Aufbau eines Steuergeräts sowie auf den verwendeten Prozessoren, Mikrocontrollern und Peripheriekomponenten. Das Kap. 5 geht auf die Kommunikationsgrundlagen ein, welche für die verwendeten Kommunikationssysteme im Kraftfahrzeug von Bedeutung sind. In Kap. 6 wird das Thema Timing-Bewertung anhand von Begriffsdefinitionen eingeführt. Weiterhin werden die typischen Ereignismodelle vorgestellt, welche für die Beschreibung des Zeitverhaltens eines Systems eine zentrale Rolle spielen. Daran anschließend folgen drei Kapitel, die sich mit unterschiedlichen Aspekten der zeitlichen Bewertung beschäftigen. Zunächst stellt Kap. 7 die Bewertung des zeitlichen Verhaltens von Software im Detail vor. In Kap. 8 werden Methoden zur zeitlichen Bewertung unter Berücksichtigung des Schedulings auf einzelnen Prozessoren oder Arbitrierungsverfahren von Bussystemen erläutert. Methoden für die Bewertung vernetzter Systeme sind in Kap. 9 beschrieben.

Unser Dank gilt unseren Kolleginnen und Kollegen. Die vielen gemeinsamen Diskussionen und Dialoge zu diesem Themengebiet bilden die Grundlage für dieses Buch.

Weiterhin möchten wir uns bei Dr.-Ing. Bernd Hense bedanken, der uns seine Vorlesungsunterlagen zur Verfügung stellte und auf dessen Abbildungen wir zurückgreifen durften.

Unser ganz besonderer Dank gilt unseren Familien, Melanie mit Konstantin und Berenike mit Lorenz und Kilian, die uns den Freiraum gegeben haben und uns auch in schwierigen Phasen eine große Unterstützung waren.

Ferner gilt unser Dank dem Springer Verlag und seinen Mitarbeiterinnen Frau Butz und Frau Hellwig, die uns in vielerlei Hinsicht unterstützt haben.

Stuttgart, München

Oktober 2011

*Thilo Streichert

Matthias Traub*

# Inhaltsverzeichnis

|                                                                   |      |

|-------------------------------------------------------------------|------|

| <b>Abkürzungen</b> .....                                          | xiii |

| <b>Symbole</b> .....                                              | xvii |

| <b>1 Einleitung</b> .....                                         | 1    |

| 1.1 Wertschöpfungskette und Unternehmensstruktur .....            | 1    |

| 1.2 Produkt- und Entwicklungszyklen .....                         | 7    |

| 1.2.1 Entwicklungsprozess .....                                   | 7    |

| 1.2.2 Kooperationsmodelle zwischen OEM und Zulieferer .....       | 10   |

| 1.3 Historische Entwicklung der Elektronik im Kraftfahrzeug ..... | 11   |

| <b>2 Grundlagen der Elektrik/Elektronik-Architekturen</b> .....   | 15   |

| 2.1 Ebenen der E/E-Architektur .....                              | 15   |

| 2.1.1 Funktionsumfang .....                                       | 18   |

| 2.1.2 Funktions-/Softwarearchitektur .....                        | 19   |

| 2.1.3 Vernetzungsarchitektur .....                                | 21   |

| 2.1.4 Komponententopologie .....                                  | 25   |

| 2.1.5 Bewertungsmetriken für E/E-Architekturen .....              | 28   |

| 2.2 Einflüsse durch Gesetzgebung und Standardisierung .....       | 32   |

| 2.3 E/E-Architekturkonzepte .....                                 | 40   |

| 2.3.1 Funktionsorientiertes Konzept .....                         | 41   |

| 2.3.2 Zentralisiertes Konzept .....                               | 42   |

| 2.3.3 Räumlichorientiertes Master/Slave-Konzept .....             | 43   |

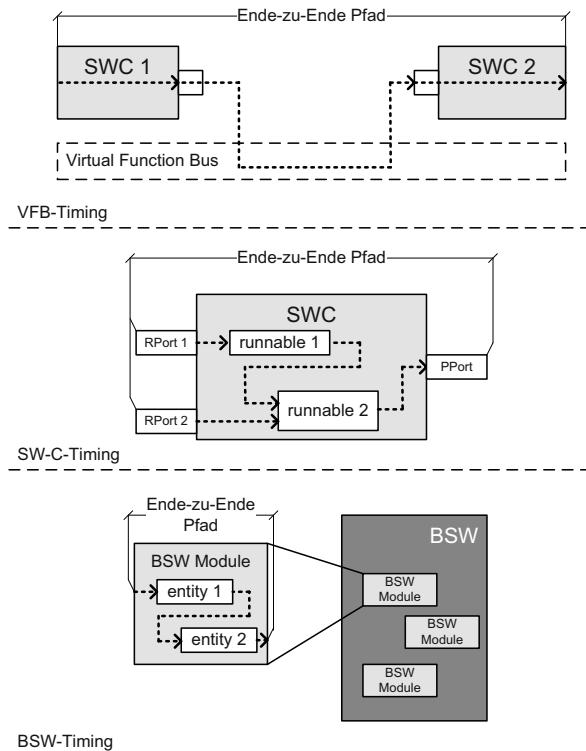

| 2.4 Ebenen der Timing-Bewertung .....                             | 46   |

| 2.5 Verfahren zu Timing-Bewertung .....                           | 49   |

| <b>3 Software-Architektur und -Entwicklung</b> .....              | 51   |

| 3.1 Software-Architektur von Steuergeräten .....                  | 52   |

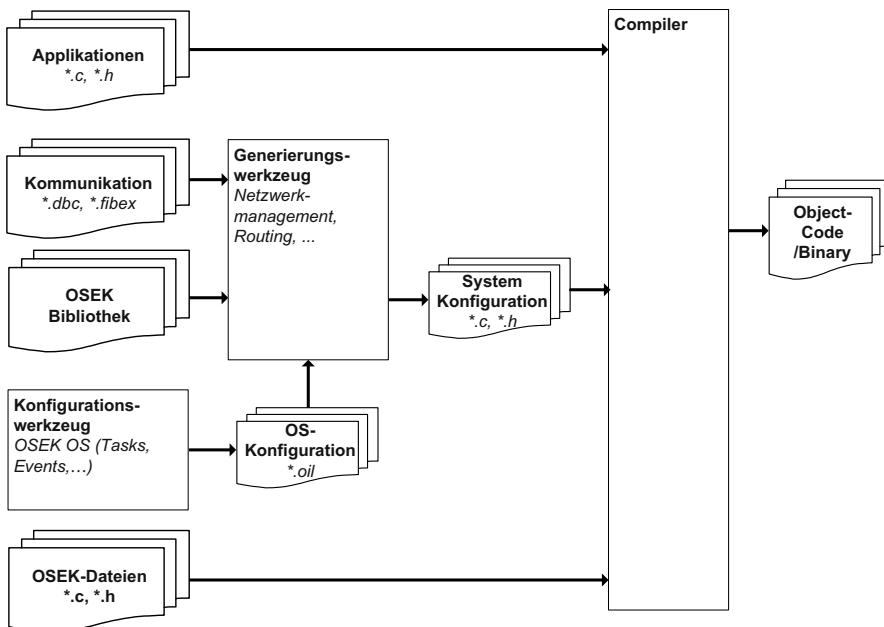

| 3.1.1 OSEK/VDX .....                                              | 52   |

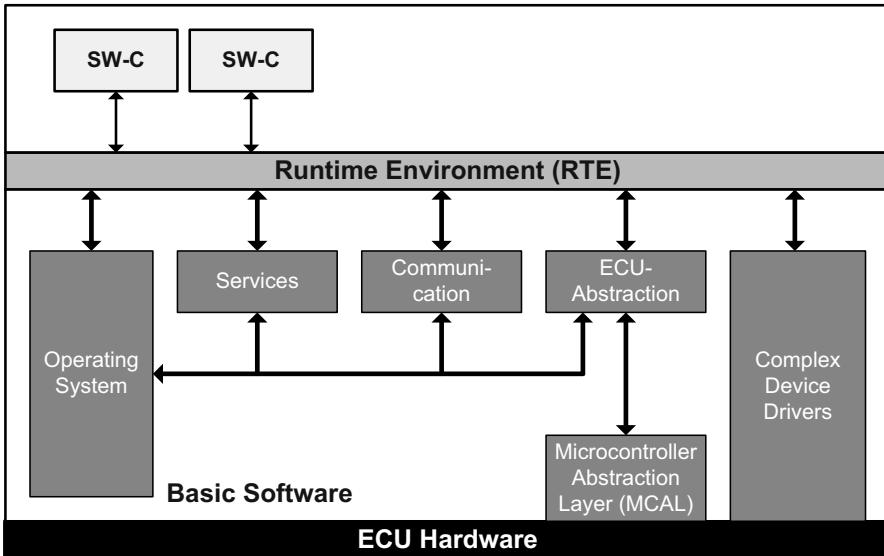

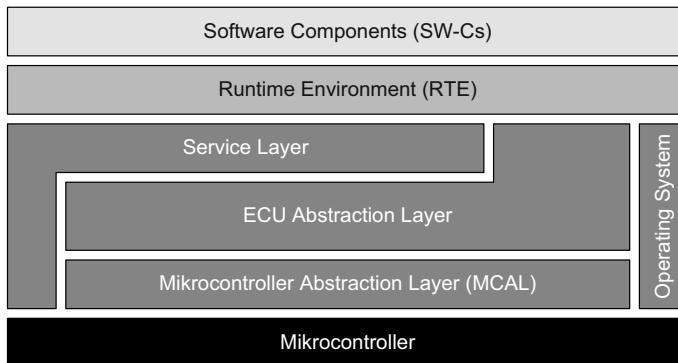

| 3.1.2 AUTOSAR .....                                               | 57   |

| 3.2 Software-Entwicklungsprozess .....                            | 67   |

|                                                                |            |

|----------------------------------------------------------------|------------|

| 3.2.1 MISRA-Regeln .....                                       | 68         |

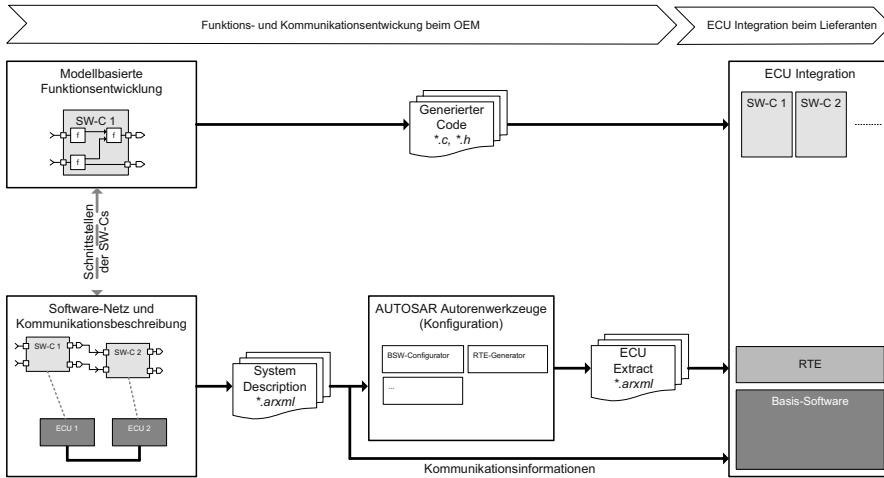

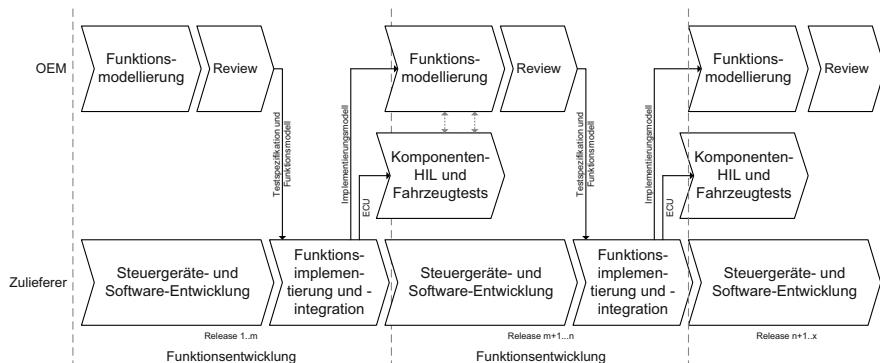

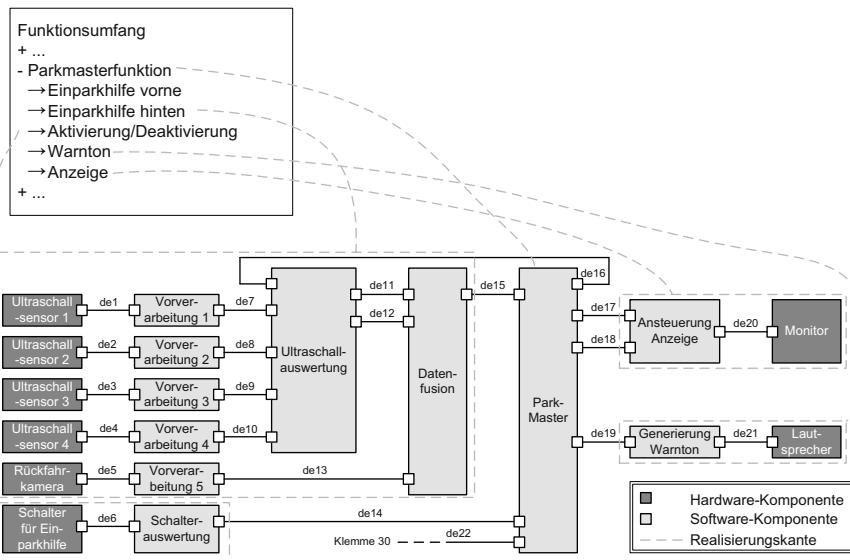

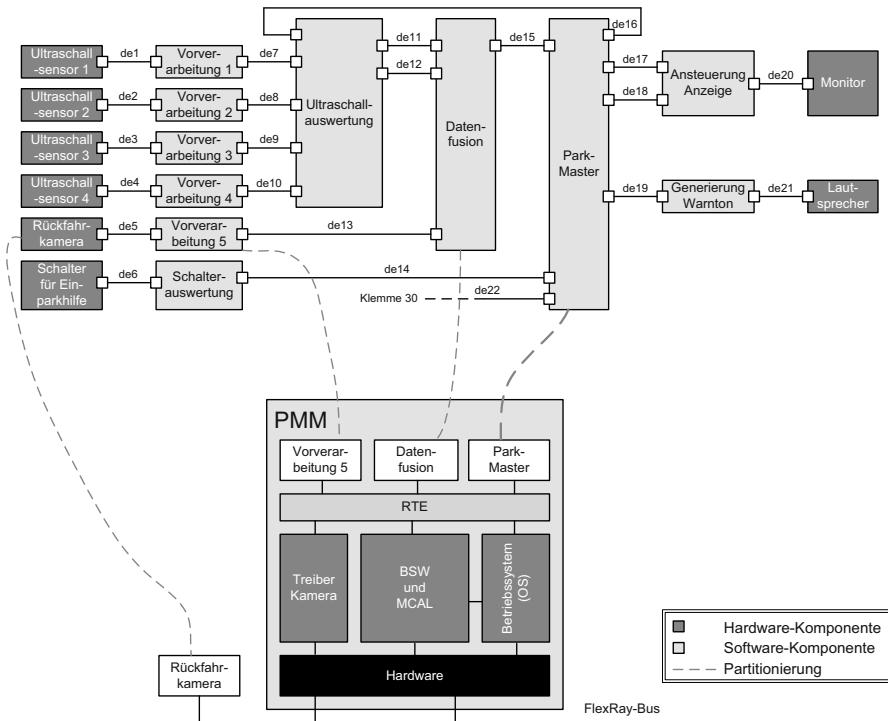

| 3.3 Modellbasierte Funktionsentwicklung .....                  | 69         |

| 3.4 Fallstudie: Von der Funktion zur Software .....            | 72         |

| <b>4 Steuergeräte und Echtzeit-Rechnerstrukturen .....</b>     | <b>77</b>  |

| 4.1 Aufbau und Anforderungen an Steuergeräte .....             | 77         |

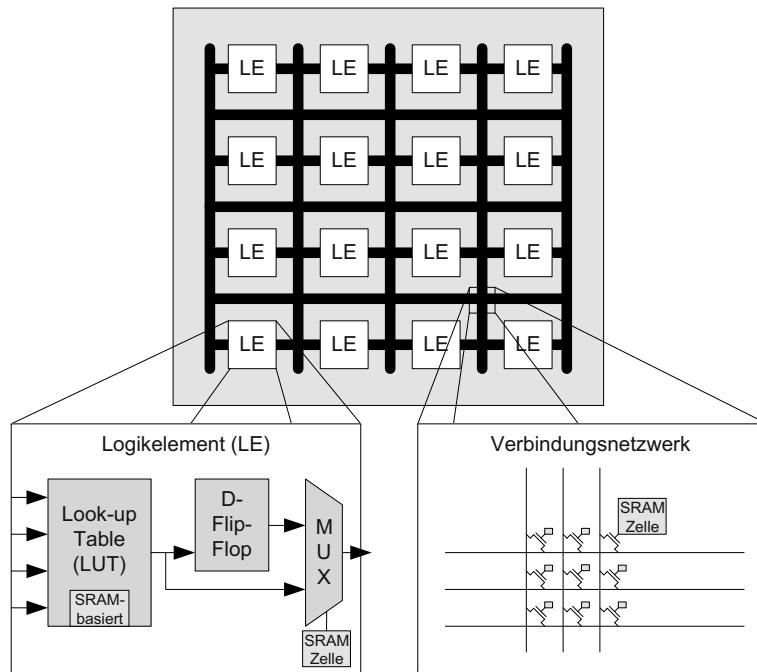

| 4.2 Rechnerarchitekturen und programmierbare Hardware .....    | 80         |

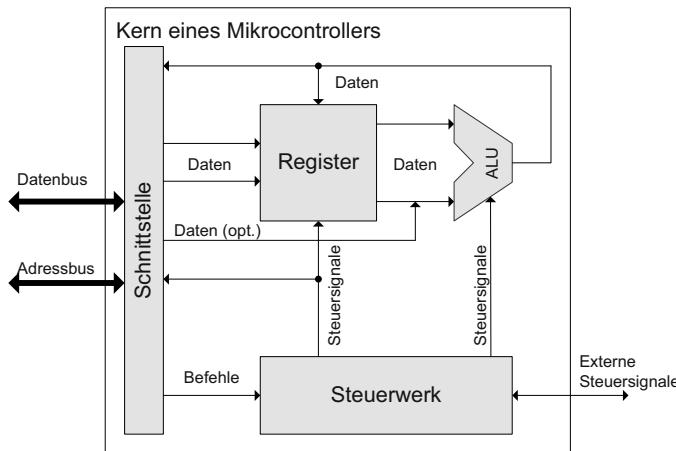

| 4.3 Komponenten eines Prozessors .....                         | 84         |

| 4.3.1 Kern eines Prozessors .....                              | 84         |

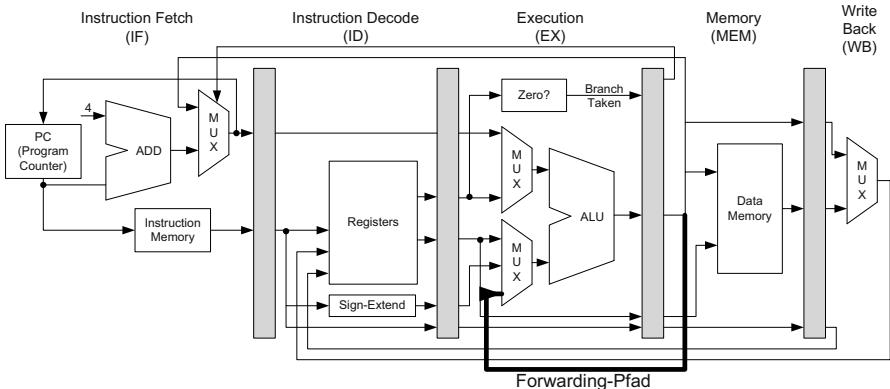

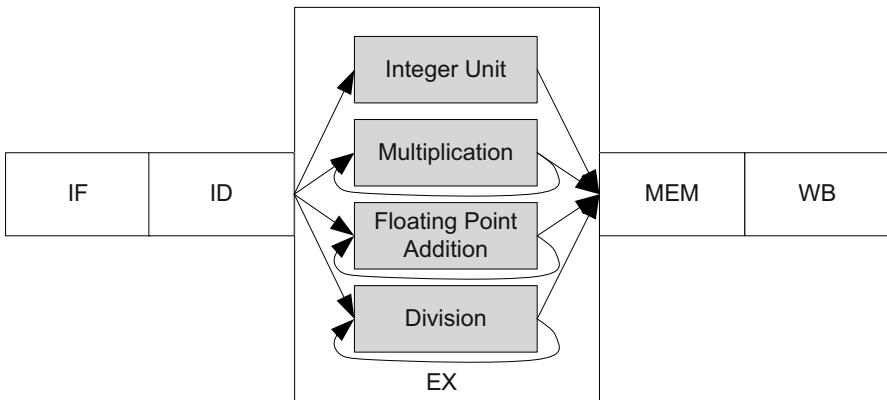

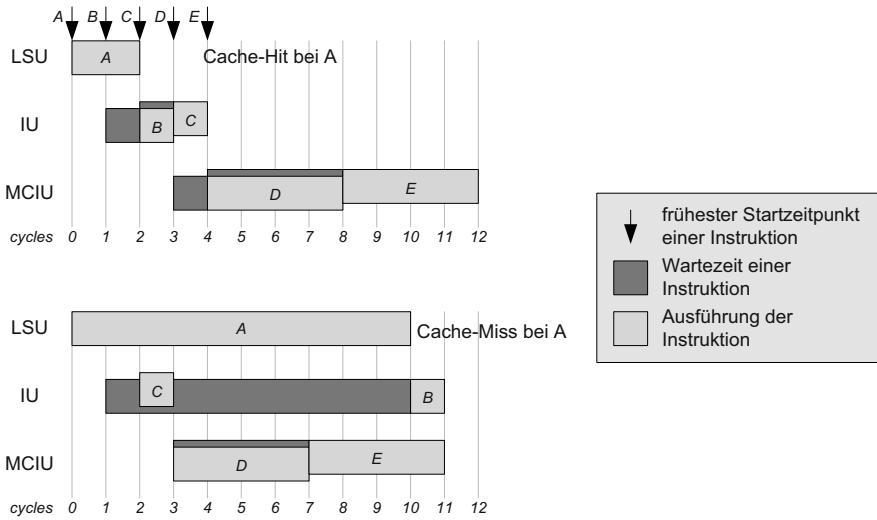

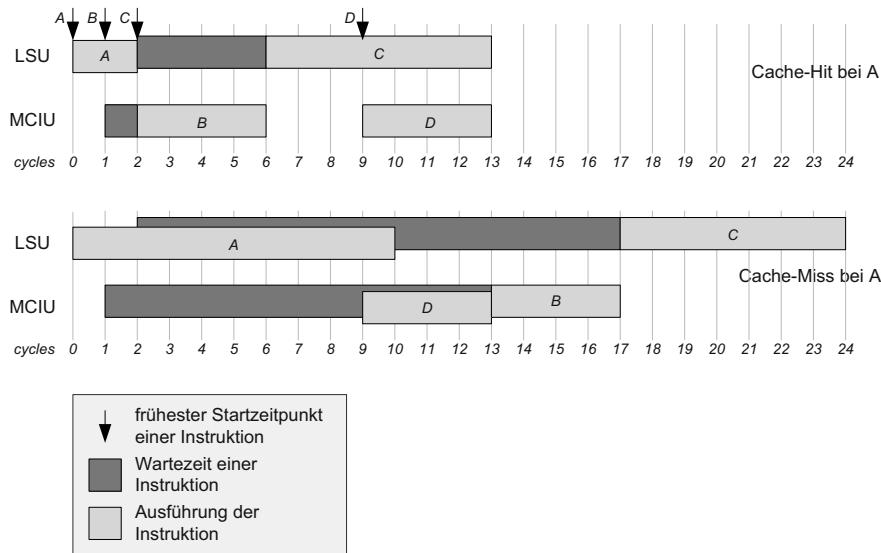

| 4.3.2 Pipelines .....                                          | 85         |

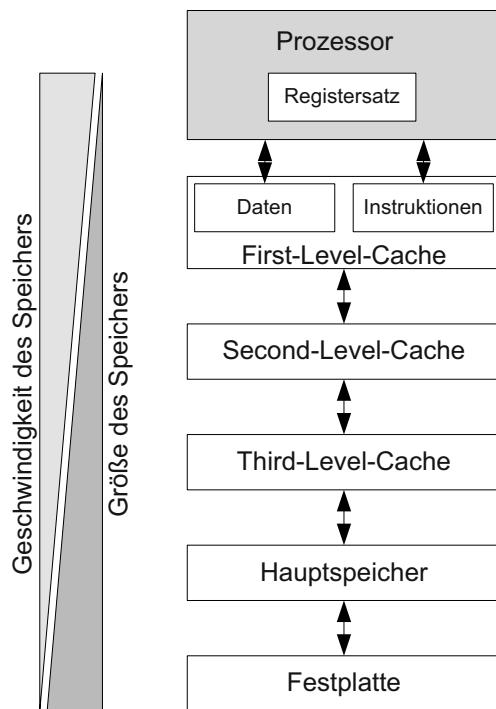

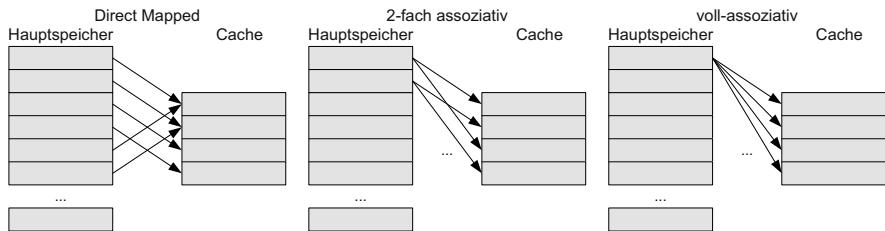

| 4.3.3 Speicherhierarchien .....                                | 90         |

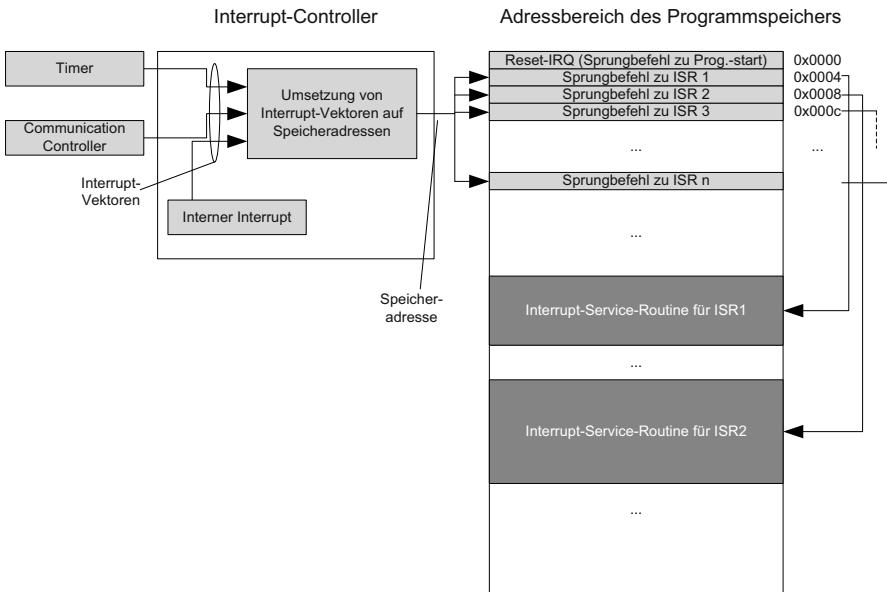

| 4.3.4 Unterbrechungen (Interrupts) .....                       | 95         |

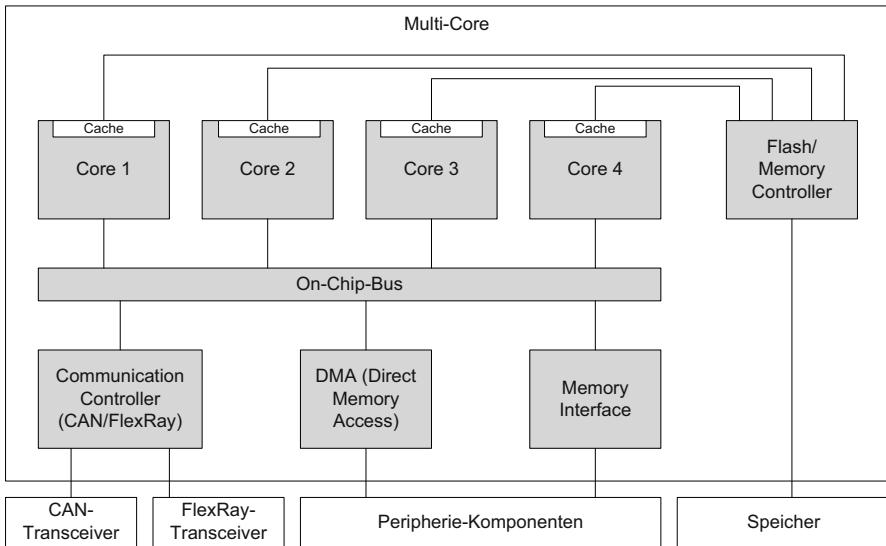

| 4.3.5 Multi-Core-Architekturen .....                           | 97         |

| 4.4 Peripheriekomponenten von CPUs .....                       | 100        |

| 4.5 Fallstudie: Architekturalternativen für Steuergeräte ..... | 104        |

| 4.5.1 Ausgangssituation .....                                  | 104        |

| 4.5.2 Entwicklungsteam .....                                   | 106        |

| 4.5.3 Architekturalternativen .....                            | 107        |

| 4.5.4 Zusammenstellung der Bauteile .....                      | 107        |

| 4.5.5 Bewertung der Architekturalternativen .....              | 110        |

| <b>5 Kommunikationsgrundlagen .....</b>                        | <b>115</b> |

| 5.1 Kommunikationssysteme .....                                | 116        |

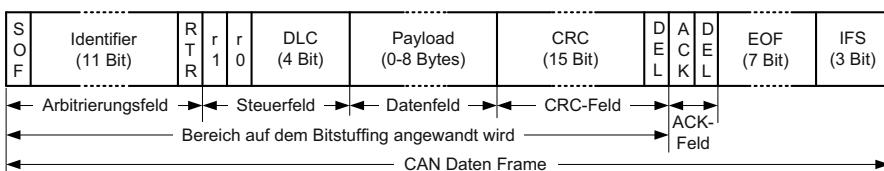

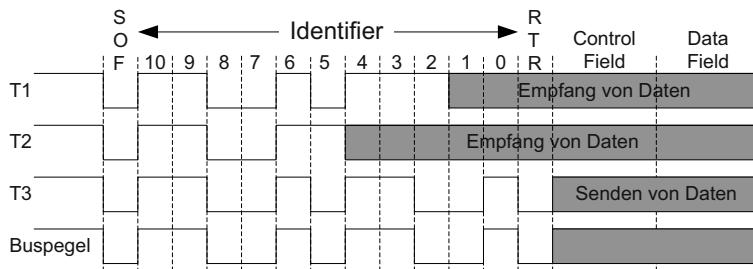

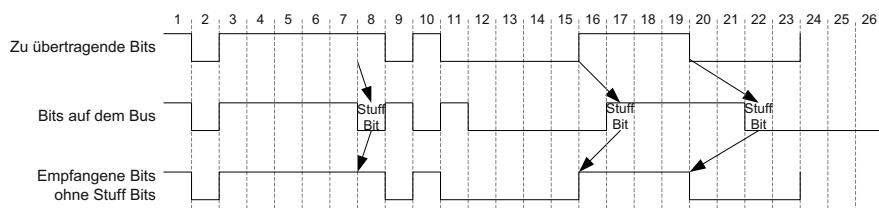

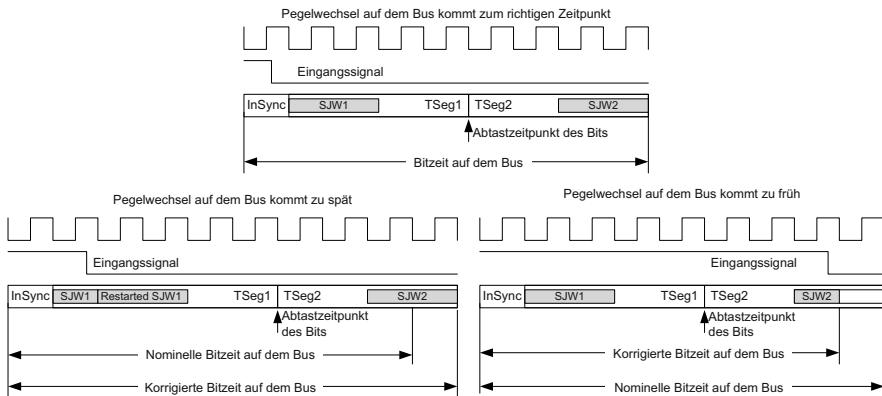

| 5.1.1 Controller Area Network .....                            | 116        |

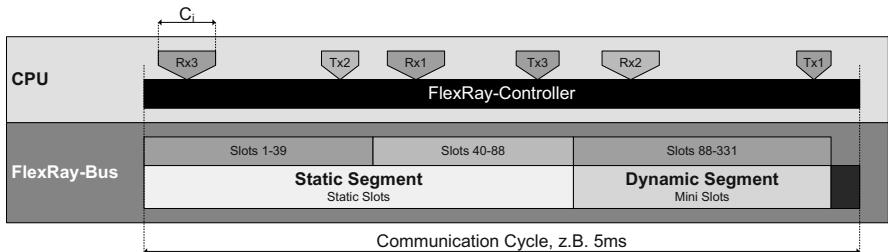

| 5.1.2 FlexRay .....                                            | 121        |

| 5.1.3 Local Interconnect Network (LIN) .....                   | 126        |

| 5.1.4 Ethernet-basierte Kommunikation .....                    | 129        |

| 5.2 Konfiguration der Busse .....                              | 135        |

| 5.2.1 Konfiguration des CAN-Bus .....                          | 137        |

| 5.2.2 Konfiguration des FlexRay-Bus .....                      | 137        |

| 5.2.3 Konfiguration des LIN-Bus .....                          | 138        |

| 5.3 Sicherheitskritische Kommunikation .....                   | 138        |

| 5.4 Fallstudie .....                                           | 140        |

| 5.4.1 Konfiguration des CAN-Busses .....                       | 142        |

| 5.4.2 Konfiguration des FlexRay-Busses .....                   | 142        |

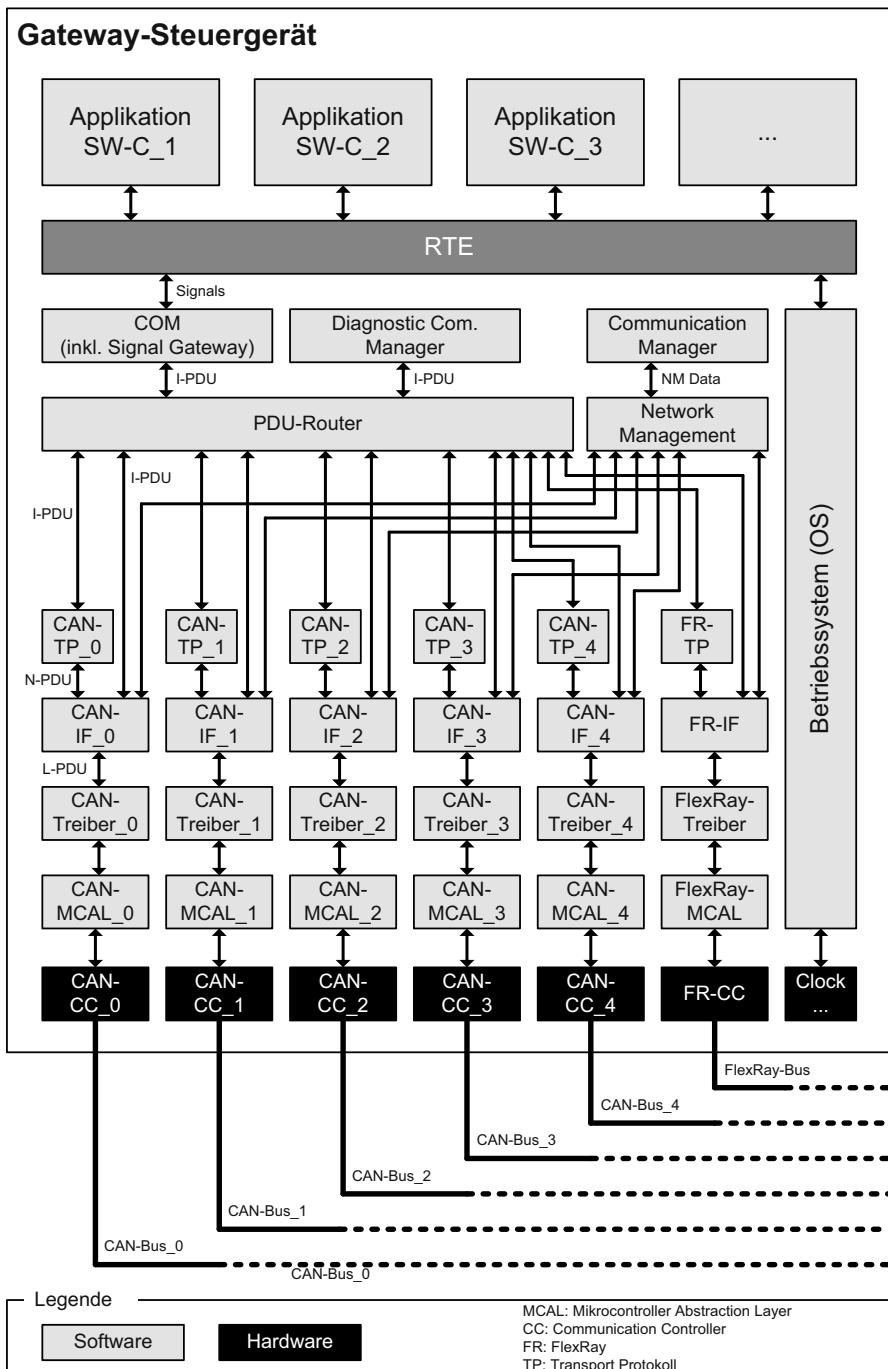

| 5.4.3 Routingtabelle des Gateways .....                        | 143        |

| <b>6 Begriffe und Kenngrößen der Timing-Bewertung .....</b>    | <b>145</b> |

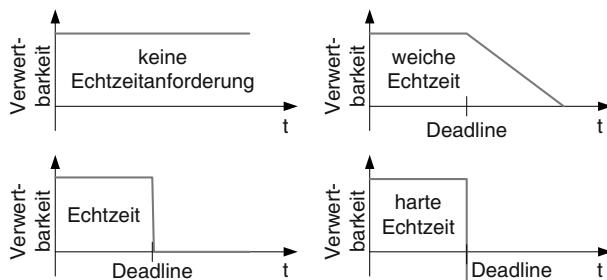

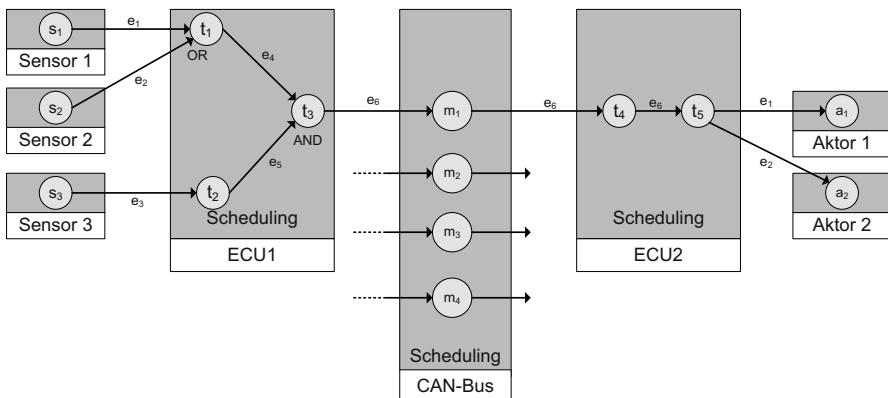

| 6.1 Eingebettete verteilte Echtzeitsysteme .....               | 145        |

| 6.2 Begriffsdefinitionen .....                                 | 146        |

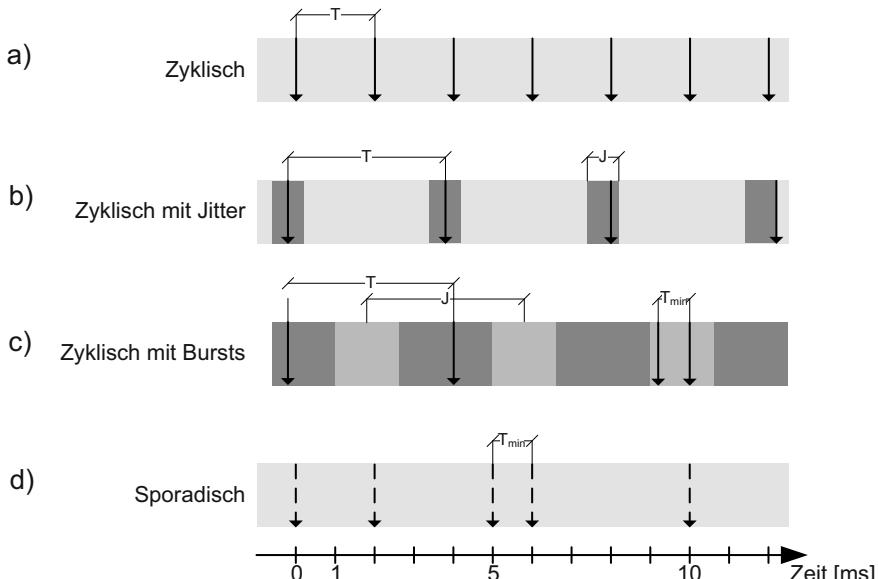

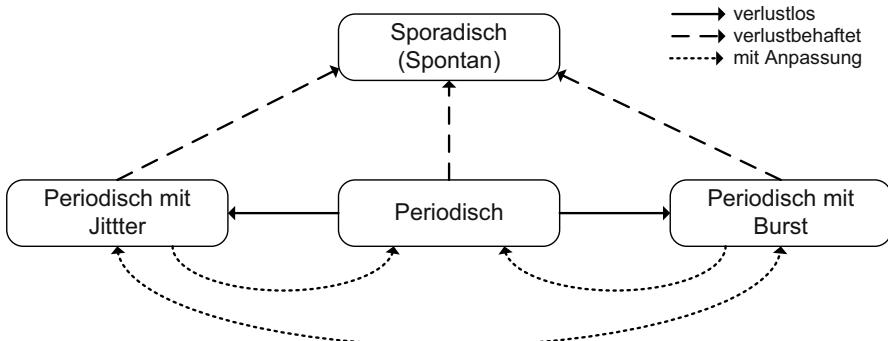

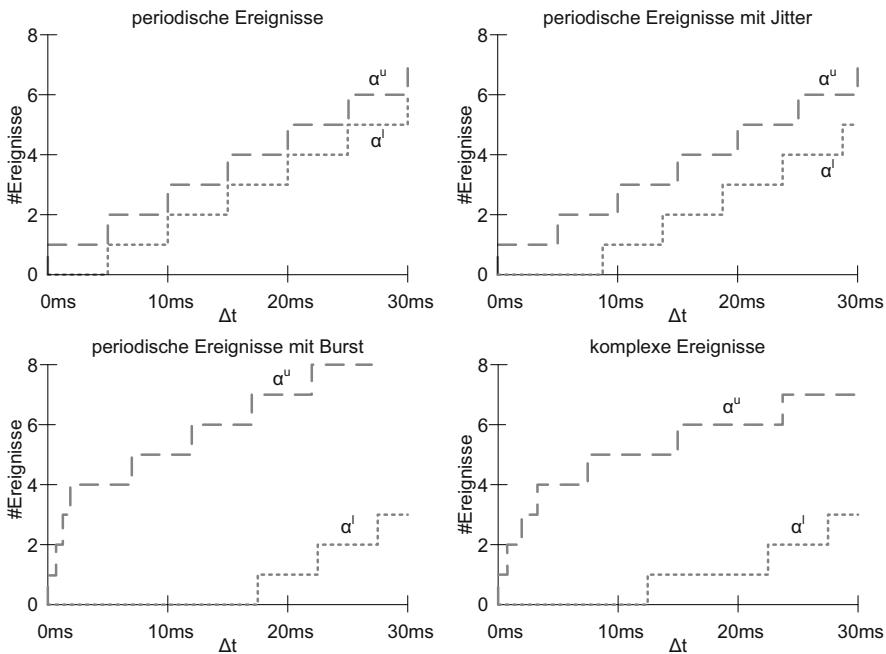

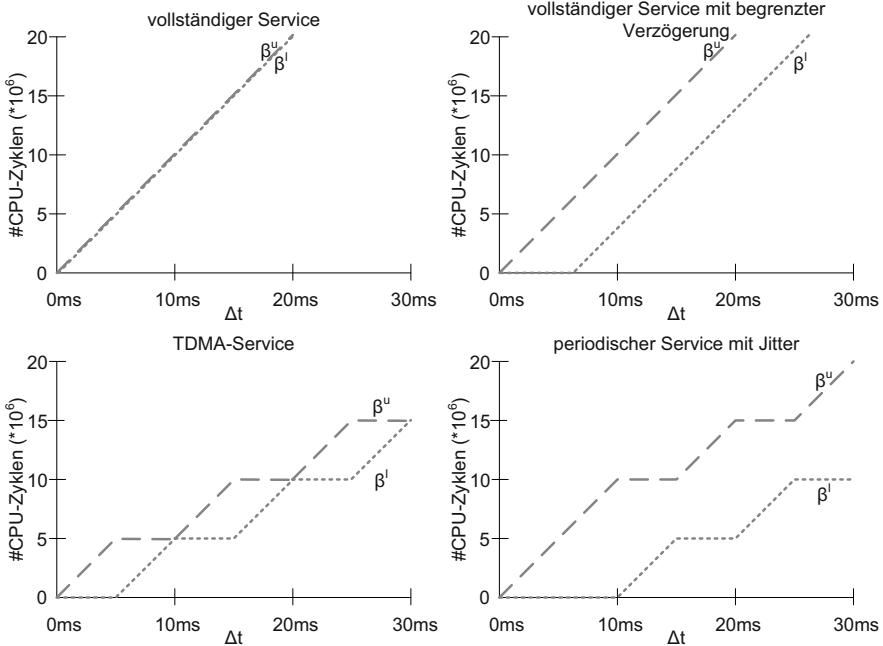

| 6.3 Ereignismodelle .....                                      | 150        |

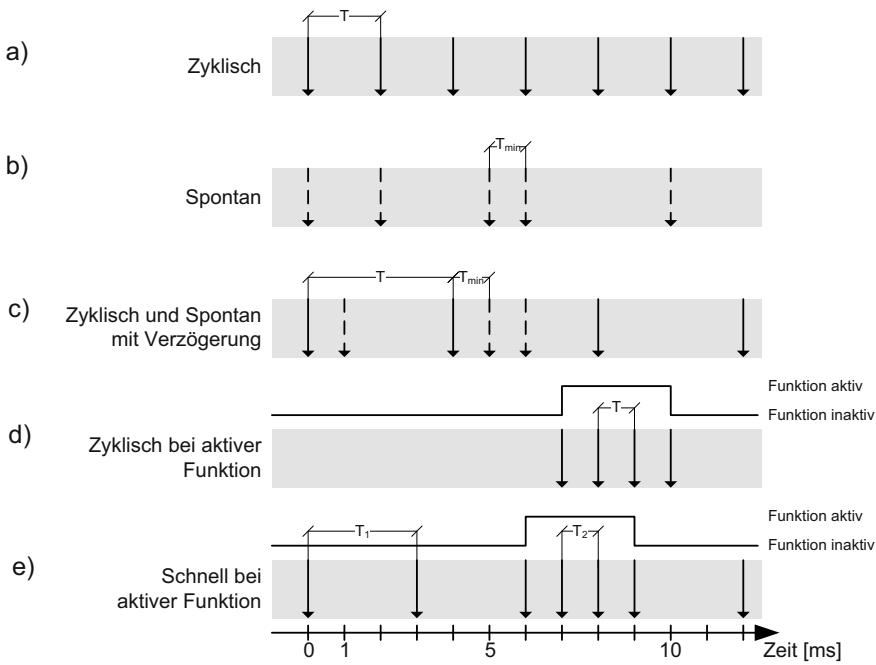

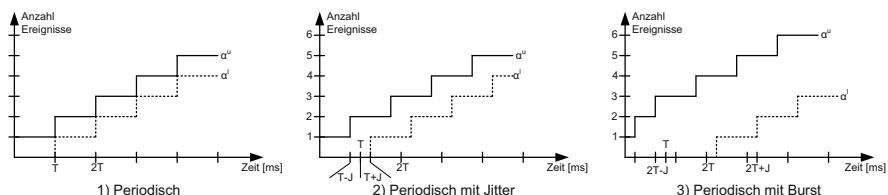

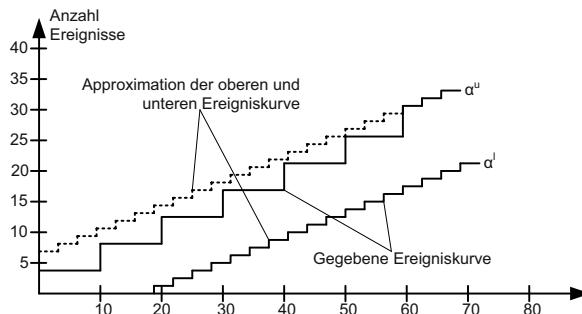

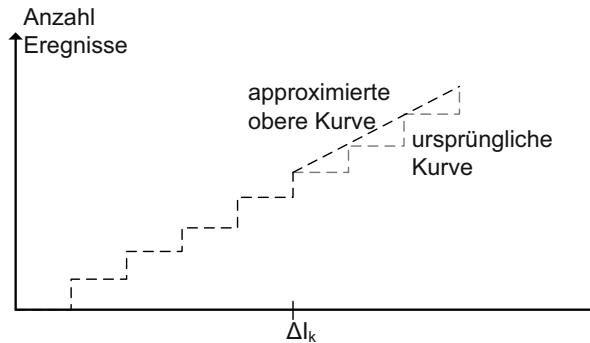

| 6.3.1 Standard Ereignismodelle .....                           | 150        |

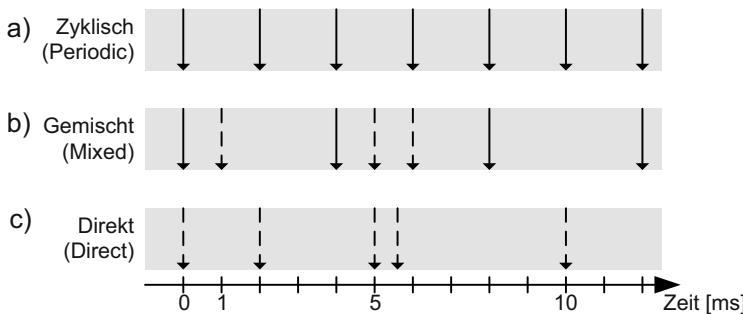

| 6.3.2 Ereignismodelle in AUTOSAR .....                         | 151        |

| 6.3.3 Ereignismodelle beim CAN-Bus .....                       | 151        |

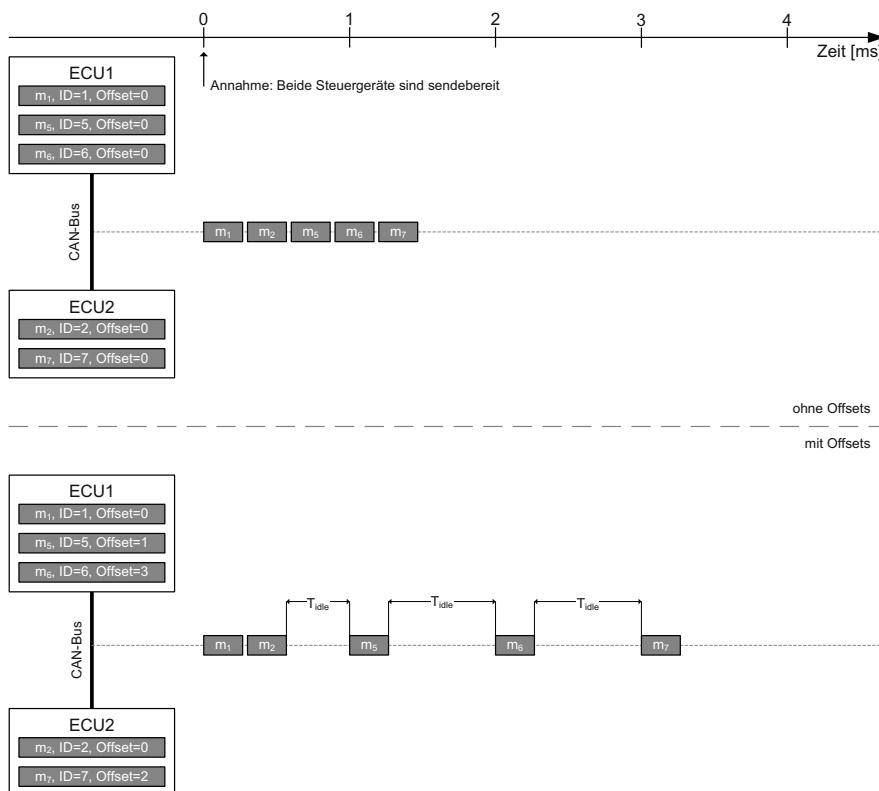

| 6.4 Offsets .....                                              | 153        |

|          |                                                                           |            |

|----------|---------------------------------------------------------------------------|------------|

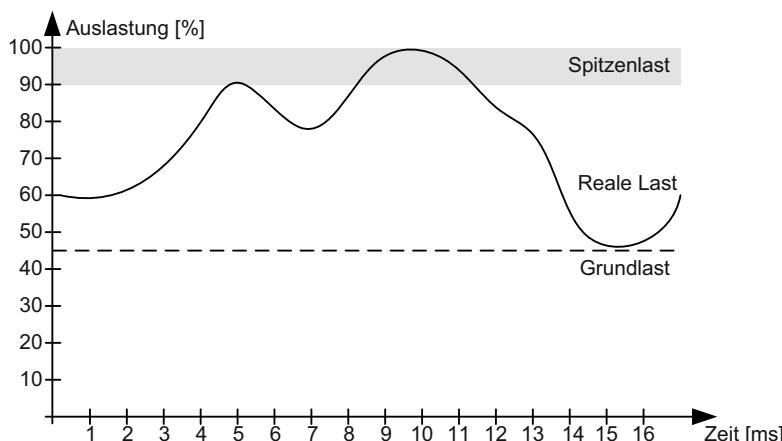

| 6.5      | Kenngrößen für die Timing-Bewertung .....                                 | 154        |

| 6.5.1    | Kenngrößen für die Bewertung von Software .....                           | 155        |

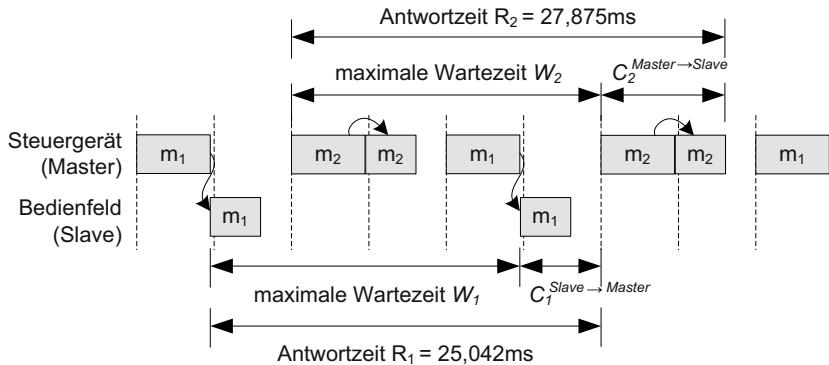

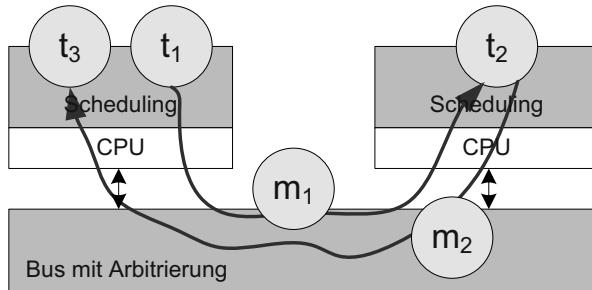

| 6.5.2    | Kenngrößen für die Bewertung von Kommunikationssystemen .....             | 156        |

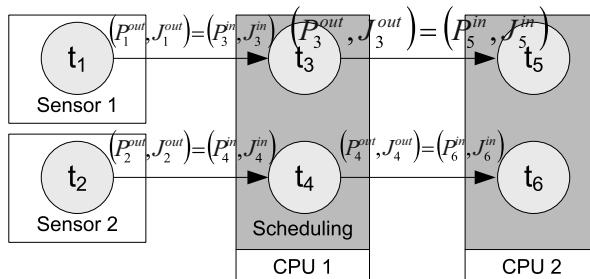

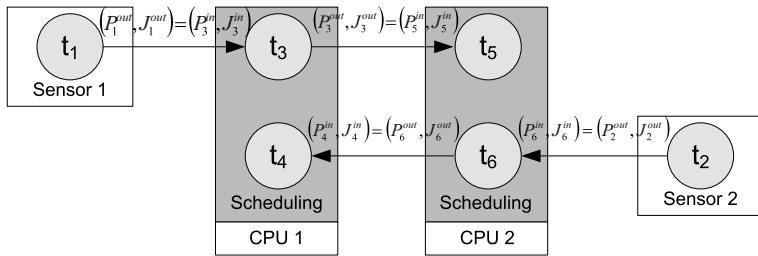

| 6.5.3    | Kenngrößen für die Bewertung von verteilten Systemen ..                   | 158        |

| <b>7</b> | <b>Timing-Bewertung von Software .....</b>                                | <b>163</b> |

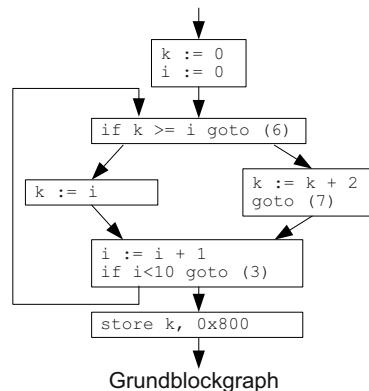

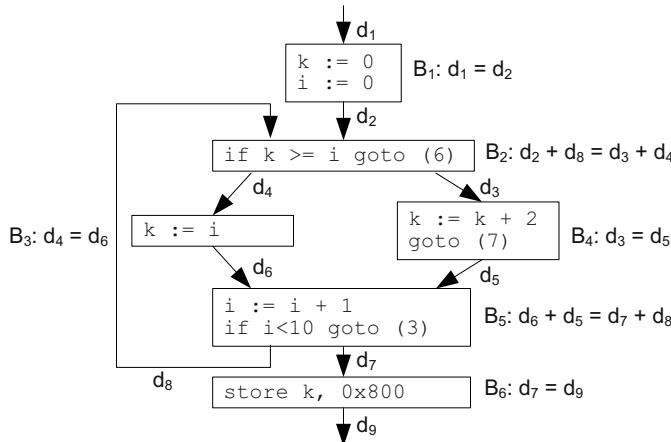

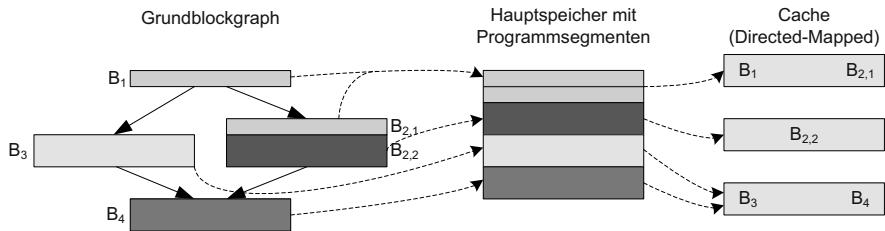

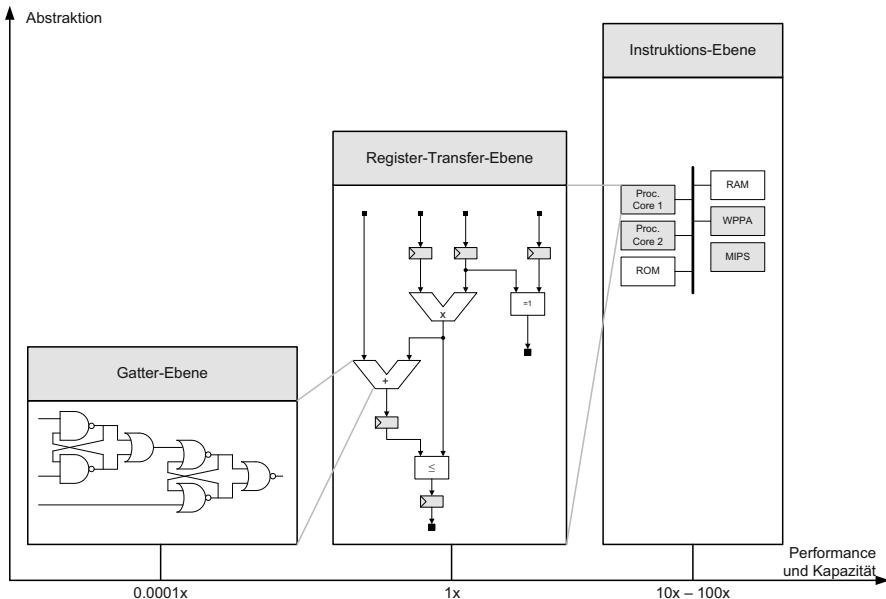

| 7.1      | Analytische Bestimmung der Ausführungszeiten .....                        | 163        |

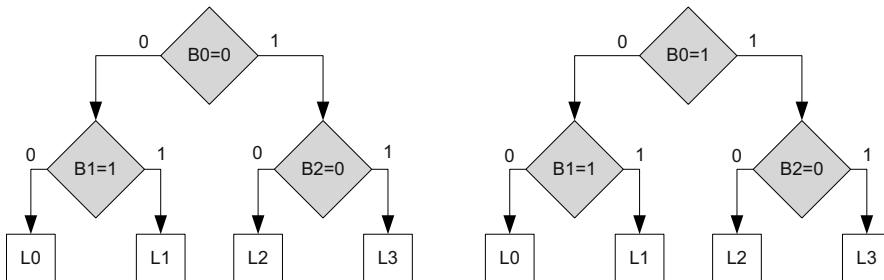

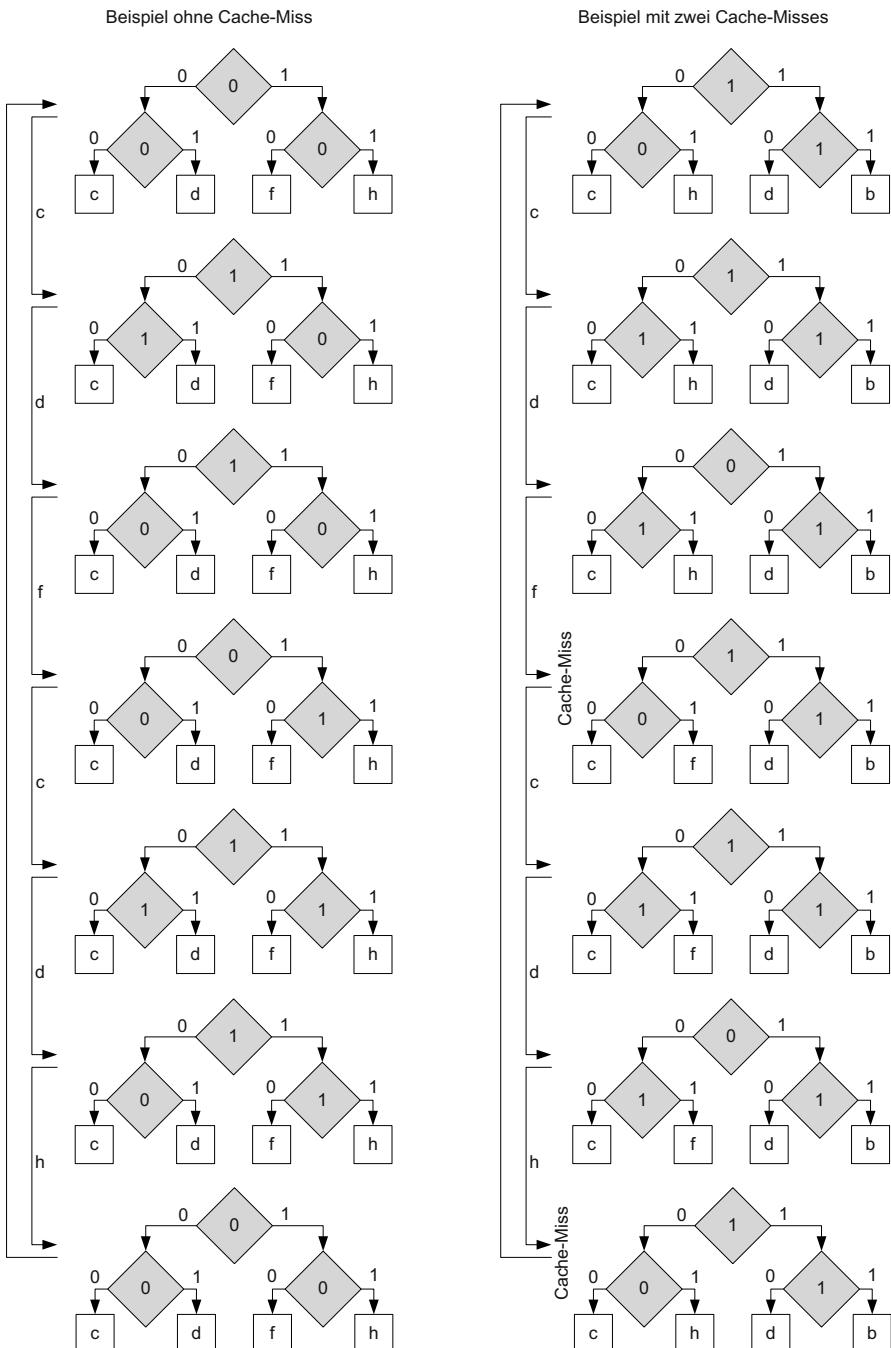

| 7.1.1    | Worst-Case-Execution-Time-Analyse .....                                   | 164        |

| 7.1.2    | Prinzipien für analysierbare Systeme und Programme ..                     | 170        |

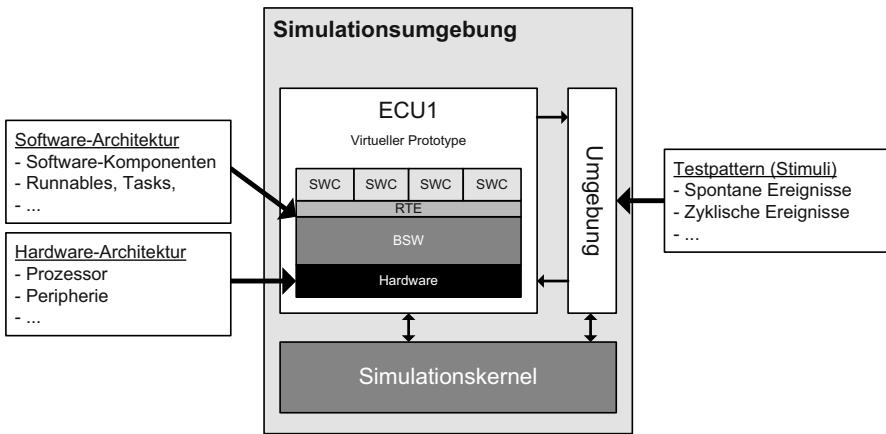

| 7.2      | Simulative Bestimmung der Ausführungszeiten .....                         | 171        |

| 7.3      | Messung der Ausführungszeiten .....                                       | 172        |

| 7.4      | Fallstudie: Bewertung der Ausführungszeiten von Software .....            | 173        |

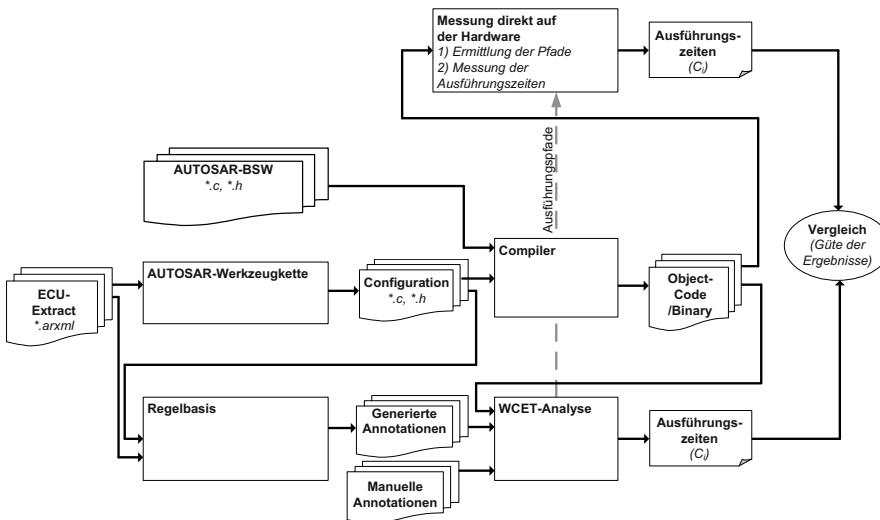

| 7.4.1    | Verwendete Werkzeugkette .....                                            | 175        |

| 7.4.2    | Analyse der Ausführungszeiten .....                                       | 176        |

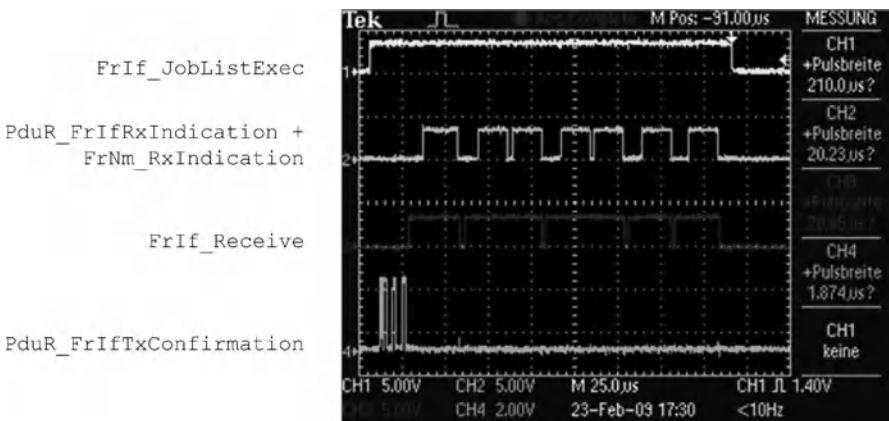

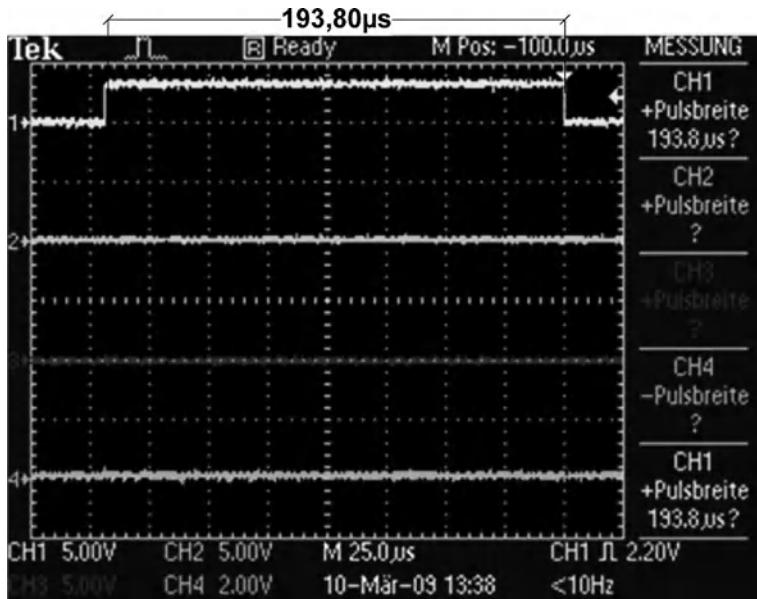

| 7.4.3    | Messung der Ausführungszeiten .....                                       | 177        |

| 7.4.4    | Vergleich der ermittelten Ausführungszeiten .....                         | 178        |

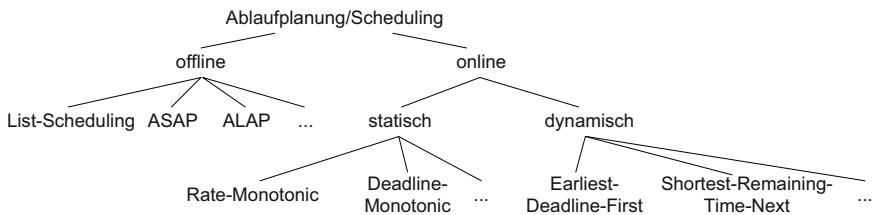

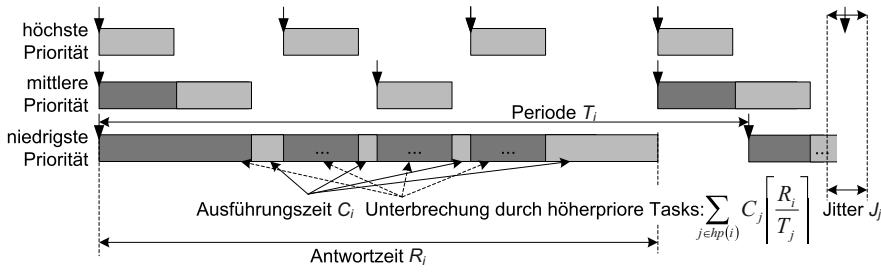

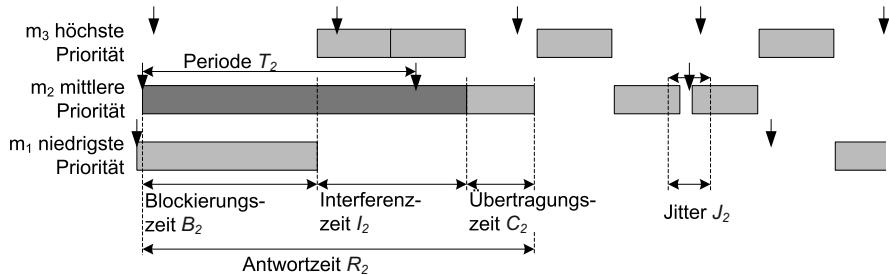

| <b>8</b> | <b>Timing-Bewertung von Komponenten .....</b>                             | <b>181</b> |

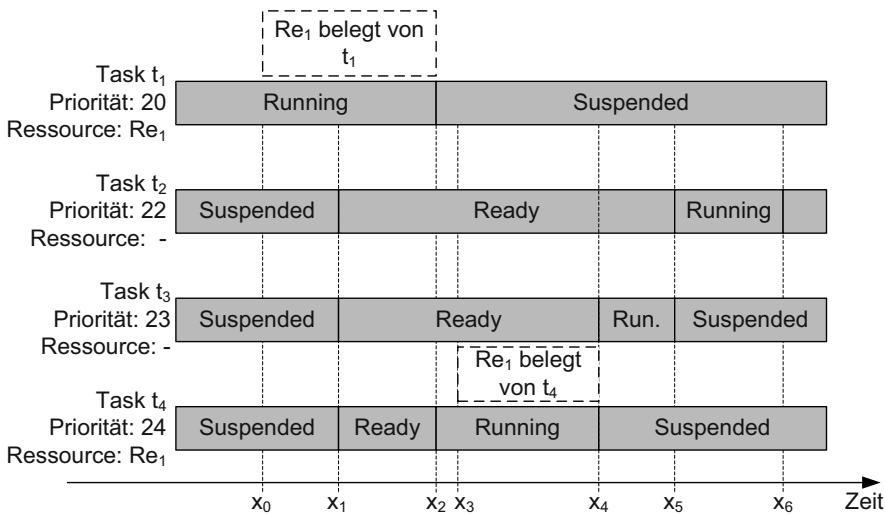

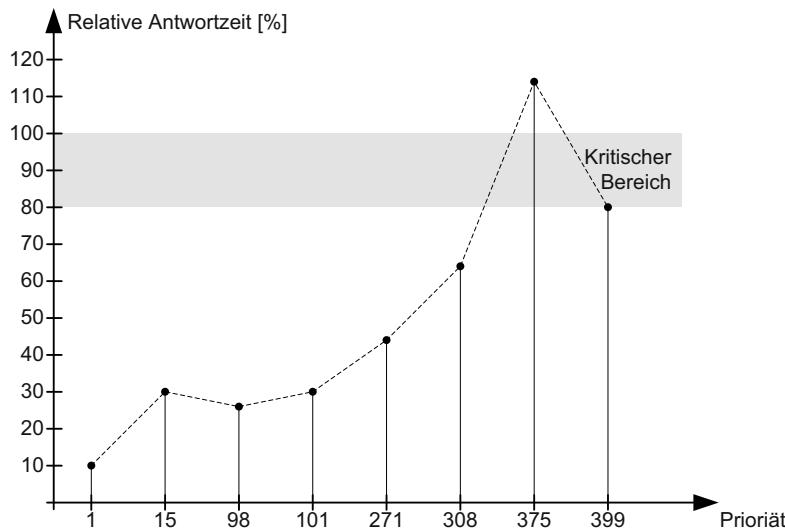

| 8.1      | Prozessor-Scheduling und Antwortzeitanalyse von Tasks .....               | 181        |

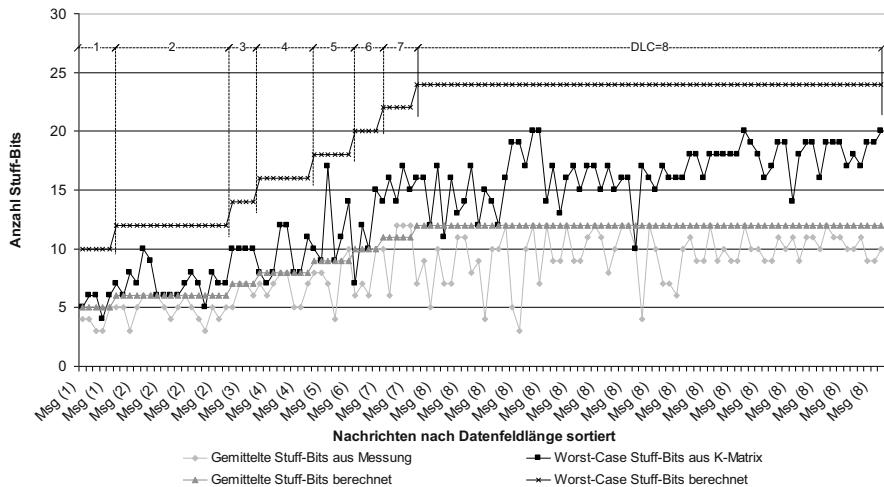

| 8.2      | Busarbitrierung und Antwortzeitanalyse von Nachrichten .....              | 186        |

| 8.2.1    | CAN-Bus .....                                                             | 186        |

| 8.2.2    | FlexRay-Bus .....                                                         | 190        |

| 8.2.3    | LIN-Bus .....                                                             | 195        |

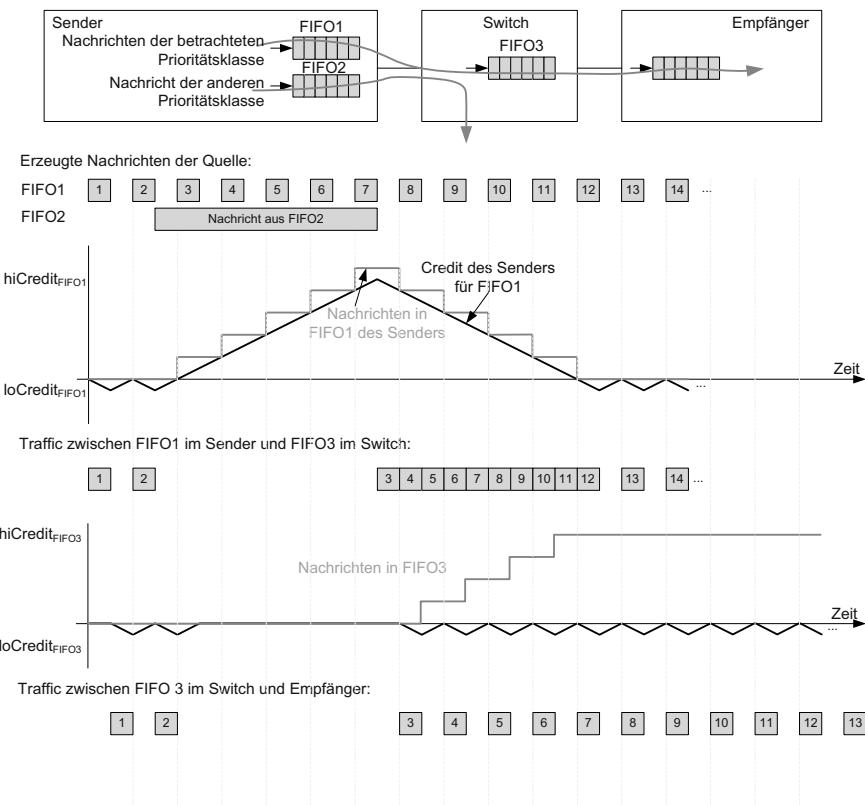

| 8.2.4    | Ethernet-AVB (IEEE 802.1Qav) .....                                        | 197        |

| 8.3      | Simulation auf Komponentenebene .....                                     | 203        |

| 8.4      | Fallstudien .....                                                         | 204        |

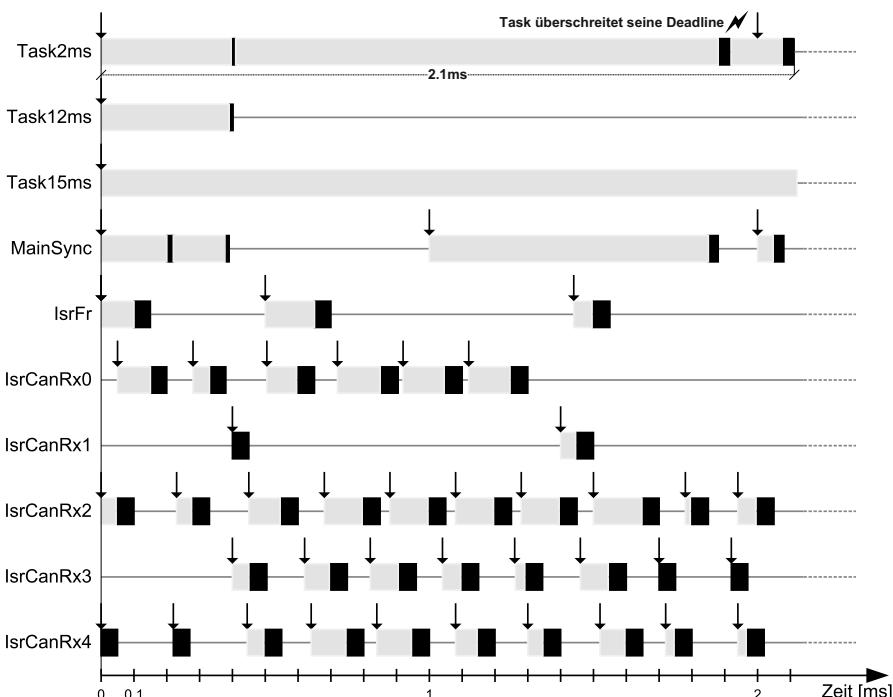

| 8.4.1    | Analyse auf ECU-Ebene .....                                               | 204        |

| 8.4.2    | Analyse eines CAN-Busses (nachvollziehbar) .....                          | 207        |

| 8.4.3    | Analyse eines CAN-Busses (komplex) .....                                  | 209        |

| 8.4.4    | Analyse des FlexRay-Busses .....                                          | 211        |

| 8.4.5    | Analyse des LIN-Busses .....                                              | 216        |

| <b>9</b> | <b>Bewertung eingebetteter Netzwerke .....</b>                            | <b>219</b> |

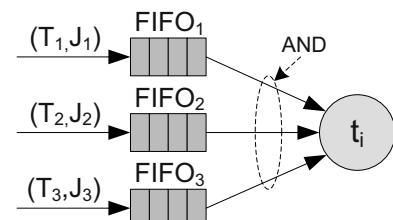

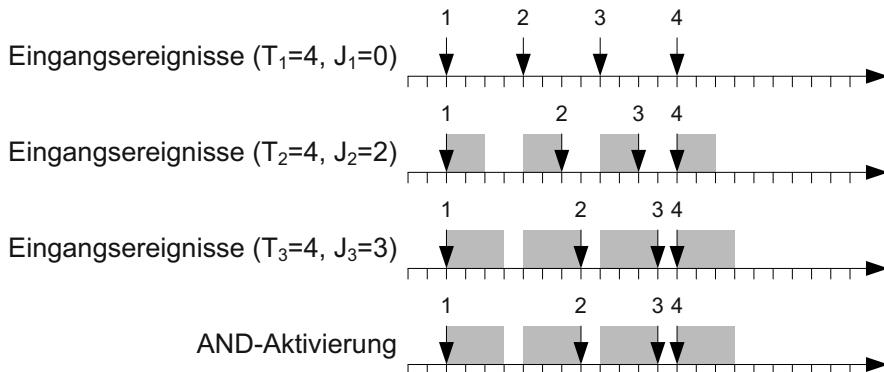

| 9.1      | Analytische Verfahren zur Bewertung des zeitlichen Systemverhaltens ..... | 219        |

| 9.1.1    | Symbolische Timing-Analyse auf Systemebene .....                          | 220        |

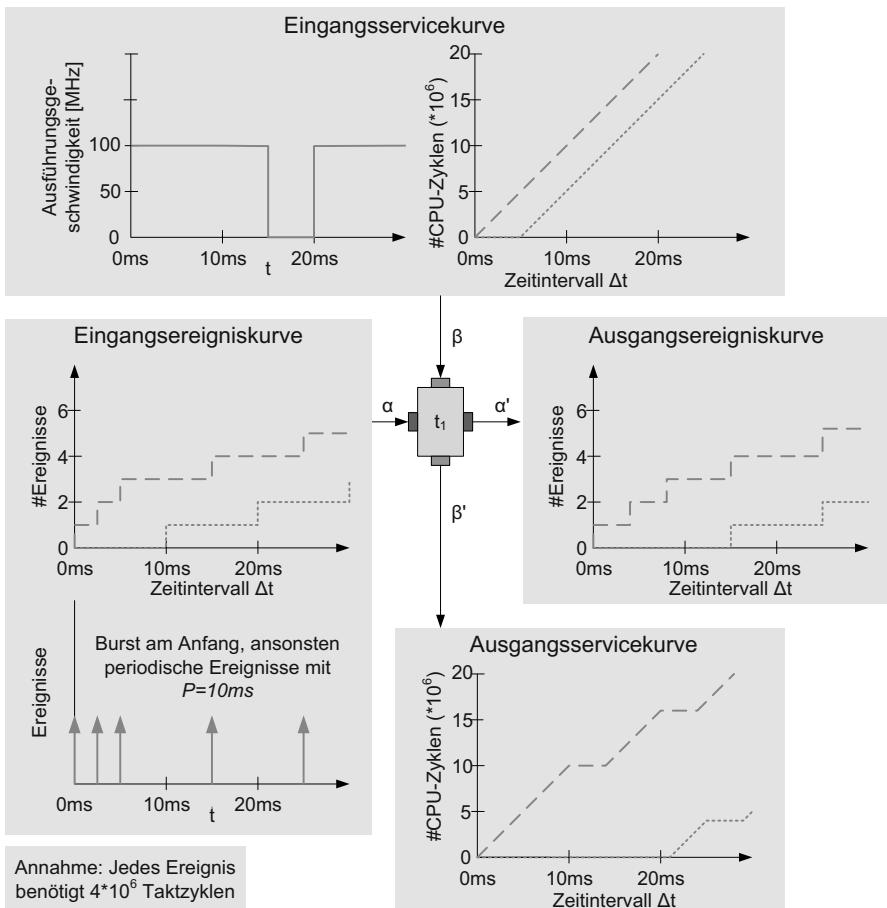

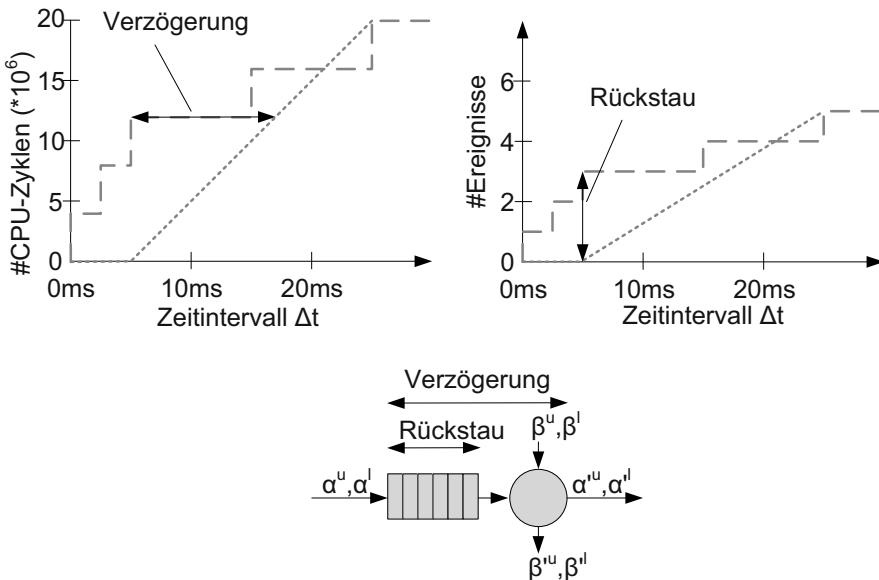

| 9.1.2    | Real-Time Calculus .....                                                  | 229        |

| 9.1.3    | Weiterführende Arbeiten zu SymTA/S und RTC .....                          | 240        |

| 9.1.4    | Timed-Automata mit Model-Checking .....                                   | 243        |

| 9.2      | Simulative Verfahren zur Bewertung des zeitlichen Systemverhaltens .....  | 247        |

| 9.3      | Fallstudien: Timing-Analyse auf Systemebene .....                         | 249        |

| 9.3.1    | Fallstudie 1 .....                                                        | 250        |

| 9.3.2    | Fallstudie 2 .....                                                        | 254        |

|                                                  |     |

|--------------------------------------------------|-----|

| <b>A Integer Linear Programming</b> .....        | 261 |

| <b>B Klemmenbezeichnung und -Steuerung</b> ..... | 265 |

| <b>Glossar</b> .....                             | 269 |

| <b>Literaturverzeichnis</b> .....                | 275 |

| <b>Sachverzeichnis</b> .....                     | 281 |

# Abkürzungen

|         |                                                |

|---------|------------------------------------------------|

| ALAP    | As Late As Possible                            |

| ALU     | Arithmetic Logic Unit                          |

| API     | Application Programming Interface              |

| ASAP    | As Soon As Possible                            |

| ASIC    | Application Specific Integrated Circuit        |

| ASIP    | Application Specific Instruction Set Processor |

| ARTOP   | AUTOSAR Tool Platform                          |

| AUTOSAR | AUTomotive Open System ARchitecture            |

| AVB     | Audio Video Broadcast                          |

| BCF     | Body Controller Front                          |

| BCET    | Best-Case Execution Time                       |

| BCR     | Body Controller Rear                           |

| BCRT    | Best-Case Response Time                        |

| BD      | Bus Driver                                     |

| BR      | Baureihe                                       |

| BSW     | Basic Software                                 |

| CAN     | Controller Area Network                        |

| CC      | Communication Controller                       |

| CE      | Consumer Electronics                           |

| CHI     | Controller Host Interface                      |

| CISC    | Complex Instruction Set Computer               |

| COM     | Communication                                  |

| CPU     | Central Processing Unit                        |

| CRC     | Cyclic Redundancy Check                        |

| CSMA    | Carrier Sense Multiple Access                  |

| DC      | Direct Current                                 |

| DIN     | Deutsches Institut für Normung                 |

| DLC     | Data Length Code                               |

| DSP     | Digital Signal Processor                       |

| ECU     | Electronic Control Unit                        |

| EDD     | Earliest Due Date                              |

|       |                                                   |

|-------|---------------------------------------------------|

| EDF   | Earliest-Deadline First                           |

| E/E   | Elektrik/Elektronik                               |

| EHPV  | Engineered Hours Per Vehicle                      |

| EMV   | Elektromagnetische Verträglichkeit                |

| EOF   | End Of Frame                                      |

| ESD   | Electro-static Discharge                          |

| FCFS  | First-come-first-served                           |

| FIBEX | Field Bus Exchange Format                         |

| FIFO  | First Input First Output                          |

| FM    | Fertigungs- und Materialkosten                    |

| FPGA  | Field Programmable Gate Array                     |

| FR    | FlexRay                                           |

| GPIO  | General Purpose I/O                               |

| GPU   | Graphics Processing Unit                          |

| GuK   | Gewährleistungs- und Kulanzkosten                 |

| GW    | Gateway                                           |

| HAL   | Hardware Abstraction Layer                        |

| HIL   | Hardware-in-the-Loop                              |

| HIS   | Herstellerinitiative Software                     |

| HPV   | Hours Per Vehicle                                 |

| HW    | Hardware                                          |

| ID    | Identifier                                        |

| IEEE  | Institute of Electrical and Electronics Engineers |

| IFS   | Inter Frame Space                                 |

| ILP   | Integer Linear Program                            |

| I/O   | Input/Output                                      |

| IP    | Intellectual Property                             |

| IP    | Internet Protocol                                 |

| ISO   | International Organization of Standardization     |

| ISR   | Interrupt Service Routine                         |

| IU    | Instruction Unit                                  |

| KFZ   | Kraftfahrzeug                                     |

| LAN   | Local Area Network                                |

| LDF   | Latest Deadline First                             |

| LDF   | Lin Description File                              |

| LFU   | Least-Frequently Used                             |

| LIN   | Local Interconnect Network                        |

| LLC   | Logical Link Control                              |

| LRU   | Least-Recently Used                               |

| LSU   | Load and Store Unit                               |

| LUT   | Look Up Table                                     |

| LVDS  | Low Voltage Differential Signaling                |

| MAC   | Media Access Control                              |

| MCAL  | Mikrocontroller Abstraction Layer                 |

| MCIU  | Multi-Cycle Instruction Unit                      |

|        |                                                 |

|--------|-------------------------------------------------|

| MCU    | Mikrocontroller Unit                            |

| MII    | Media Independent Interface                     |

| MOST   | Media Oriented Systems Transport                |

| MUX    | Multiplexer                                     |

| NIT    | Network Idle Time                               |

| NM     | Network Management                              |

| NRZ    | Non Return to Zero                              |

| OBD    | On-Board Diagnosis                              |

| OEM    | Original Equipment Manufacturer                 |

| OIL    | OSEK Implementation Language                    |

| OS     | Operating System                                |

| OSI    | Open System for Interconnection                 |

| PC     | Program Counter                                 |

| PC     | Personal Computer                               |

| PDU    | Protocol Data Unit                              |

| PHY    | Physical Bus Connect                            |

| PLL    | Phase Locked Loop                               |

| PLRU   | Pseudo Least-Recently Used                      |

| PPM    | Parts Per Million                               |

| PWM    | Pulse Width Modulation                          |

| RAM    | Radom Access Memory                             |

| RISC   | Reduced Instruction Set Computing               |

| ROM    | Read-Only Memory                                |

| RR     | Round-Robin                                     |

| RTC    | Real-Time Calculus                              |

| RTE    | Runtime Environment                             |

| RTR    | Remote Transmission Request                     |

| SG     | Steuergerät                                     |

| SJF    | Shortest-job-first                              |

| SJW    | Synchronisation Jump Width                      |

| SOF    | Start Of Frame                                  |

| SOP    | Start of Production                             |

| SPI    | Serial Peripheral Interface                     |

| SRAM   | Static Random Access Memory                     |

| SRTN   | Shortest-remaining-time-next                    |

| SW     | Software                                        |

| TCP/IP | Transmission Control Protocol/Internet Protocol |

| TDMA   | Time Division Multiple Access                   |

| TT     | Time Triggered                                  |

| TTCAN  | Time-Triggered Controller Area Network          |

| TP     | Transport Protocol                              |

| UART   | Universal Asynchronous Receiver Transmitter     |

| UDP    | User Datagram Protocol                          |

| UTC    | Universal Time Coordinated                      |

| VFB    | Virtual Function Bus                            |

|      |                            |

|------|----------------------------|

| VLAN | Virtual Local Area Network |

| XML  | Extended Markup Language   |

| WCET | Worst-Case Execution Time  |

| WCRT | Worst-Case Response Time   |

# Symbole

|                    |                                                                          |

|--------------------|--------------------------------------------------------------------------|

| $a$                | Aktivierungszeitpunkt einer Task/Nachricht                               |

| $B$                | Blockierungszeit                                                         |

| $b$                | Startzeitpunkt der Ausführung/Übertragung                                |

| $C$                | Ausführungszeit oder Übertragungszeit (Computation or transmission time) |

| $c$                | Endzeitpunkt einer Ausführung/Übertragung                                |

| $d$                | Deadline einer Task/Nachricht                                            |

| $E$                | Ereignisstrom                                                            |

| $e$                | Ereignis (Event)                                                         |

| $H$                | Hyperperiode oder Makroperiode                                           |

| $I$                | Interferenzzeit                                                          |

| $i$                | Intervall                                                                |

| $J$                | Jitter                                                                   |

| $J_{\text{abs}}$   | Absoluter Jitter                                                         |

| $J_{\text{in}}$    | Eingangsjitter                                                           |

| $J_{\text{out}}$   | Ausgangsjitter                                                           |

| $J_{\text{rel}}$   | Relativer Jitter                                                         |

| $L$                | Latenzzeit                                                               |

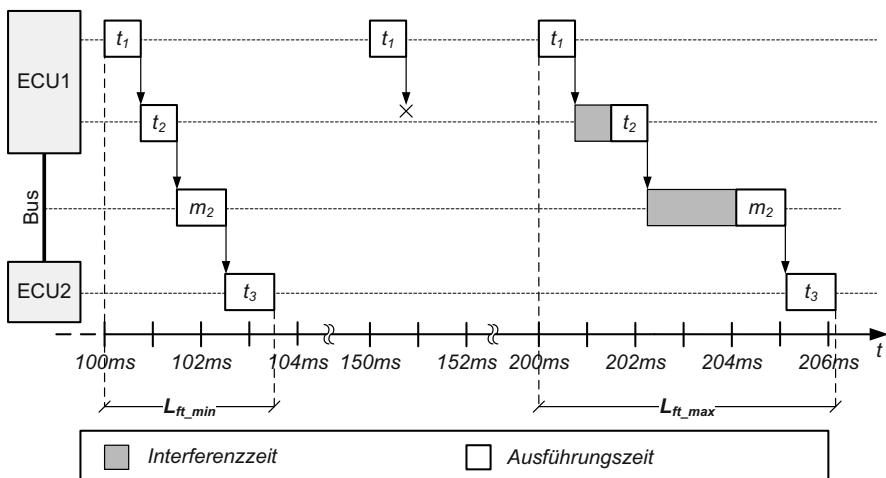

| $L_{\text{ft}}$    | Ende-zu-Ende Latenzzeit mit <i>First Through</i> Semantik                |

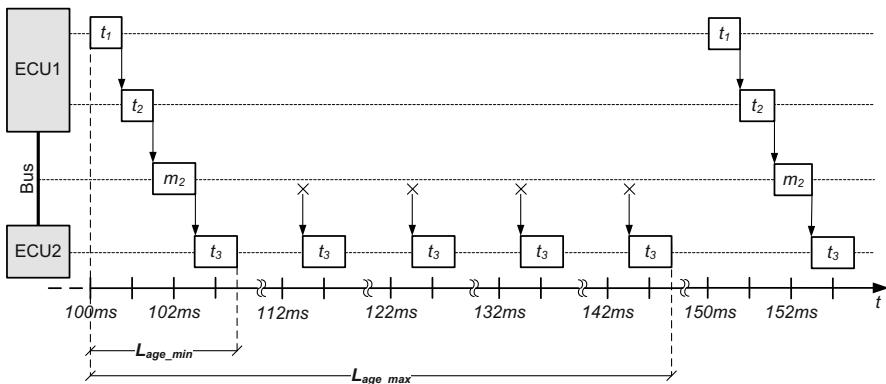

| $L_{\text{age}}$   | Ende-zu-Ende Latenzzeit mit <i>Max. Age</i> Semantik                     |

| $L_{\text{route}}$ | Routingzeit                                                              |

| $MT$               | Macrotick                                                                |

| $\mu T$            | Microtick                                                                |

| $m$                | Nachricht (Message)                                                      |

| $n$                | Wiederholungsfaktor                                                      |

| $P$                | Periodisches Ereignismodell                                              |

| $R$                | Antwortzeit (Response Time)                                              |

| $R_{\text{rel}}$   | Relative Antwortzeit                                                     |

| $r$                | Aktivierungsbegrenzung                                                   |

| $T$                | Periode                                                                  |

| $T_{\text{com}}$   | Periode des COM-Tasks                                                    |

| $T_{\text{cycle}}$ | Dauer eines kompletten Zykluses                                          |

|                    |                                                      |

|--------------------|------------------------------------------------------|

| $T_{\text{exe}}$   | Überschreitungszeit (Exeeding Time)                  |

| $T_{\text{idle}}$  | Idle-Zeit                                            |

| $T_{\text{ifs}}$   | Dauer des Interframe-Space bei CAN                   |

| $T_{\text{late}}$  | Verspätung (Lateness)                                |

| $T_{\text{min}}$   | Minimaler Auftritts-/Sendeabstand (Minimum distance) |

| $T_{\text{off}}$   | Offset                                               |

| $T_{\text{PduR}}$  | Latenzzeit für ein PDU-Routing                       |

| $T_{\text{slack}}$ | Schlupf                                              |

| $T_{\text{SR}}$    | Latenzzeit für ein Signal-Routing                    |

| $T_{\text{start}}$ | Startzeit                                            |

| $t$                | Task                                                 |

| $U$                | Auslastung                                           |

| $W$                | Wartezeit                                            |

# Kapitel 1

## Einleitung

Die Entwicklung der Automobilelektronik ist geprägt von Kooperationen zwischen Firmen, langfristigen technologischen Möglichkeiten und gesetzlichen Vorgaben. Im Unterschied zur *Consumer Electronic (CE)* umfasst die Automobilelektronik nur einen Teil eines Produkts, das aus mechanischen, elektrischen und in hohem Maße gestalterischen Anteilen besteht. Während Entwicklungs- und Produktlebenszyklen in der Consumer Electronic auf wenige Jahre beschränkt sind, ist der zeitliche Rahmen bei der Produktentstehung und des Betriebs eines Kraftfahrzeugs deutlich länger. In den folgenden Abschnitten soll ein Eindruck vermittelt werden wie das Zusammenspiel zwischen verschiedenen Firmen innerhalb der Wertschöpfungskette funktioniert und wie der grobe Zeitplan bei der Entwicklung eines Fahrzeugs aussieht. Abschließend ist anhand von einigen Diagrammen die historische Entwicklung der Automobilelektronik dargestellt.

### 1.1 Wertschöpfungskette und Unternehmensstruktur

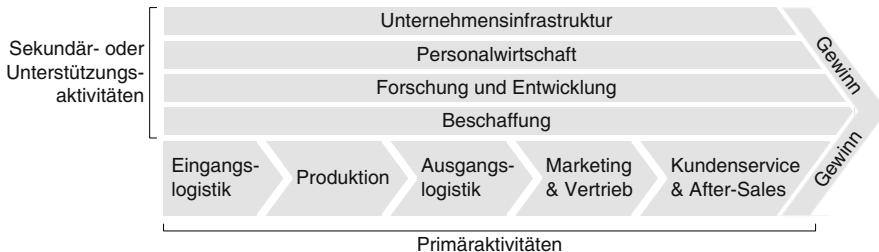

Im Allgemeinen ergibt sich die Struktur der Wertschöpfungskette aus klassisch unternehmerischen Tätigkeiten des Erwerbs von Produktionsfaktoren auf Beschaffungsmärkten, die wertsteigernd verarbeitet werden. Hierdurch entstehen Produkte oder Dienstleistungen, die auf Absatzmärkten angeboten werden können. Dieser Ablauf aus Beschaffung, Wertsteigerung und Verkauf bezieht sich nicht nur auf firmenübergreifende, sondern auch auf firmeninterne Arbeitsabläufe. Nach Michael E. Porter kann ein Unternehmen in Tätigkeitsbereiche unterteilt werden, die Hand in Hand ineinander greifen und so ein Produkt entwerfen, herstellen, vermarkten, vertreiben und letztendlich auch im sogenannten *After-Sales*-Bereich aktiv sind. Dabei ist zwischen *Primär-* und *Sekundär-* bzw. *Unterstützungsaktivitäten* zu unterscheiden [Por09]. Die Primäraktivitäten sind unmittelbar an der Wertschöpfung im Unternehmen beteiligt. Wie in Abb. 1.1 dargestellt, zählen zu den Primäraktivitäten die *Eingangslogistik, Produktion, Ausgangslogistik, Marketing und Vertrieb* sowie die *Kundenbetreuung im After-Sales*.

Abb. 1.1 Wertschöpfungskette nach Michael Porter [Por09]

Die *Eingangslogistik* nimmt die Produktionsfaktoren entgegen, kontrolliert sie und kümmert sich um Lagerung und internen Weitertransport. Die *Produktion* führt die wertsteigernde Transformation durch. Anschließend folgt die *Ausgangslogistik* der produzierten Waren, welche die Lagerung und Verteilung an den Kunden umfasst. Bei Handelsunternehmen ohne eigene Produktion kann dieses Modell leicht abgewandelt sein. Zwischen Ein- und Ausgangslogistik kann dann der eigentliche Handel liegen - also z. B. das Anbieten von Waren in der Handelsorganisation bzw. in einer Filiale. Der Bereich *Marketing und Vertrieb* kümmert sich um alle Aufgaben, die rund um den Verkauf der Produkte angesiedelt sind. Hierzu zählen beispielsweise Ermittlung von Kundenwünschen und Werbemaßnahmen. Die *Kundenbetreuung* und der *After-Sales* versorgt Kunden mit notwendigen Leistungen, um die Verwendung der angebotenen Ware über eine gewisse Zeitspanne zu gewährleisten und ggf. auf den neuesten Stand bringen zu können. Hierzu zählt beispielsweise im Automobilgeschäft die Lieferung von Ersatzteilen.

Zu den Sekundär- bzw. Unterstützungsaktivitäten gehören die *Unternehmensinfrastruktur*, *Personalwirtschaft*, *Forschung und Entwicklung* sowie *Beschaffung*. Die *Unternehmensinfrastruktur* übernimmt unter anderem Aufgaben der Unternehmensführung wie die Formulierung von Zielen und die Entwicklung von Strategien zur Erreichung der Ziele. Weiterhin gehören die Klärung von Rechtsfragen, die Finanzplanung, Qualitätskontrollen und die Schnittstellenfunktion für externe Einrichtungen und Behörden dazu. Zentrale Aufgaben in der *Personalwirtschaft* sind die Einstellung, Freisetzung und Entlohnung von Personal. Hierzu gehört auch die Ermittlung des Personalbedarfs in einzelnen Unternehmensbereichen, die Weiterbildung des Personals und die Sicherstellung seiner Zufriedenheit im Unternehmen. Unter *Forschung und Entwicklung* wird nicht nur die Neu- oder Weiterentwicklung von Produkten verstanden. Die Forschung und Entwicklung hat auch die Aufgabe Prozesse und Arbeitsabläufe zu verbessern und somit kostensenkend beispielsweise auf Produktionsabläufe oder auch auf die Produktentwicklung einzuwirken. Weiterhin fällt in diesen Bereich die Informationsverwaltung, die sich mit der Speicherung und Bereitstellung von Wissen in einer Firma befasst. Die *Beschaffung* ist anders als die Einkaufslogistik und mit der Verwaltung und internen Bereitstellung von Produktionsressourcen beauftragt. Stattdessen soll sie als übergreifende Einheit allen Unternehmensbereichen die notwendigen Arbeitsmittel beschaffen. Weiterhin stellt sie ein Bindeglied zwischen Lieferanten und dem eigenen Unternehmen dar.

Hierbei geht es auch darum Einkaufsvolumen aus unterschiedlichen Bereichen zu bündeln und Beziehungen zu zuverlässigen, vertrauenswürdigen Lieferanten aufzubauen und zu pflegen. Auch die Unterstützung von finanziell angeschlagenen Lieferanten kann eine Aufgabe sein, um die Lieferverfügbarkeit zu erhalten und somit den eigenen Produktionsfluss zu gewährleisten.

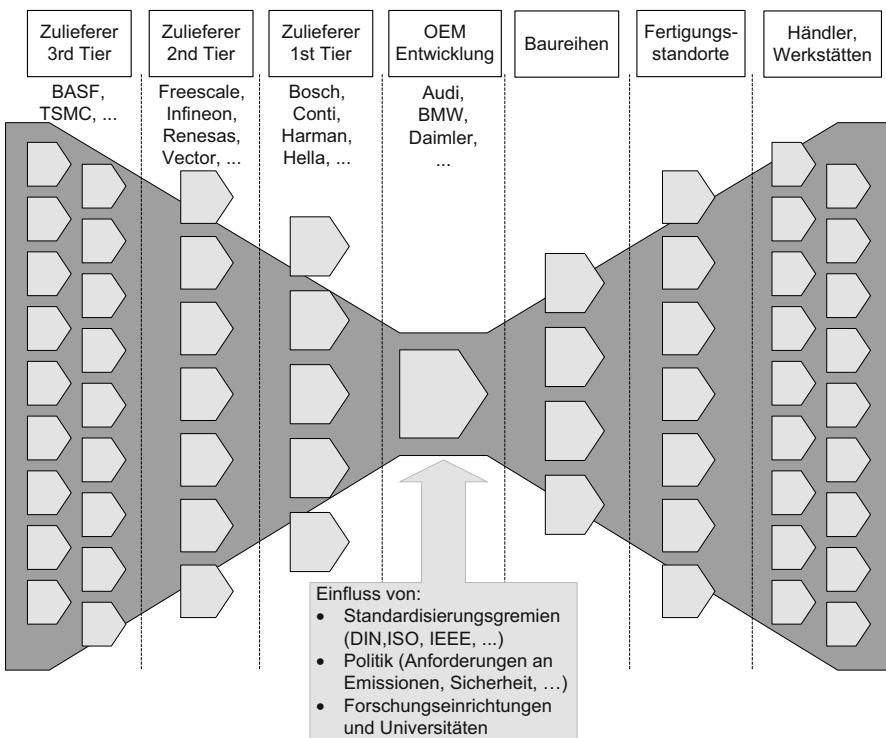

In der Automobilindustrie ist die Wertschöpfungskette bis zur Produktentstehung in verschiedene Ebenen (engl. *tier*) unterteilt. In Abb. 1.2 sind drei Zuliefererebenen dargestellt, was nicht heißen soll, dass es nur drei Ebenen sein können. Auf der dritten Ebene können sich beispielsweise Hersteller befinden, die Chemikalien für die Herstellung von Halbleiterprodukten liefern. Auf der zweiten Ebene befinden sich Firmen, von denen die Zulieferer der Automobilhersteller beliefert werden. Hierzu zählen Halbleiterfirmen, die Bauteile für Steuergeräte herstellen oder auch Software-Hersteller, die zum Beispiel Betriebssysteme programmieren. Der Lieferant auf erster Ebene steht unmittelbar mit dem Automobilhersteller bzw. *OEM* (*Original Equipment Manufacturer*) in Verbindung und liefert Komponenten oder Baugruppen, die in die Fahrzeuge integriert werden. Zusammen mit diesem Zulieferer spezifiziert der OEM die Beschaffenheit der Komponente. Der OEM entscheidet in welche Fahrzeugbaureihen die Komponente einfließen soll und verteilt die verschiedenen Fahrzeugbaureihen auf unterschiedliche Produktionsstandorte. Bei der Produktion wird nicht nur auf unternehmensinterne Produktionskapazitäten zurückgegriffen. Für Baureihen mit geringem Volumen und Automatisierungsgrad kommt es durchaus vor, dass die Produktion an Fremdfirmen vergeben wird. Beispiele hierfür sind die Mercedes G-Klasse oder der BMW X3, die bei Magna-Steyr gefertigt werden [uS09, uS04]. Der Vertrieb und der Kundenservice ist regional verteilt und kann durch Niederlassungen eines OEMs erfolgen oder durch selbständige Autohändler sowie Reparaturwerkstätten.

An der Darstellung in Abb. 1.2 ist gut zu erkennen, dass die Anzahl an involvierten Firmen und Firmenstandorten steigt, je weiter die Ebene von der Produktentwicklung beim OEM entfernt ist. Grundsätzlich ist anzumerken, dass die Kommunikation nicht nur zwischen benachbarten Ebenen erfolgt. Vielmehr muss auch ein OEM beispielsweise mit Halbleiterherstellern Handelsbeziehungen aufbauen, um sicherzustellen, dass der Ressourcenfluss auf keiner Ebene ins Stocken gerät. Sollte das dennoch der Fall sein, kann es sich auf die eigene Produktion auswirken. Die Folgen können sich direkt in der Verfügbarkeit sowie in der Qualität des Produktes zeigen und zu negativen Erfahrungen beim Kunden führen.

Neben den Kommunikationsbeziehungen innerhalb einer Wertschöpfungskette bestehen auch Beziehungen zu Standardisierungsgremien wie *DIN* (*Deutsches Institut für Normung*), *ISO* (engl. *International Organization for Standardization*), *IEEE* (engl. *Institute of Electrical and Electronics Engineers*), etc. Die Standards dieser Gremien sind teilweise verbindlich von OEMs anzuwenden wie es beispielsweise bei fahrzeugübergreifenden Schnittstellen zur Diagnose der Fall ist. Häufig entstehen aber auch Standards, um eine hohe Diversität an technischen Lösungsansätzen zu reduzieren. In einem solchen Fall ist die Berücksichtigung eines Standards nicht zwingend erforderlich, kann aber die Produktgestaltung vereinfachen. Weitere Randbedingungen für die Produktgestaltung und -entstehung werden durch

**Abb. 1.2** Dargestellt ist die Zuliefererkette bis zum OEM sowie die aus der Entwicklung entstehenden Baureihen, die auf Fertigungsstandorte und Niederlassungen verteilt werden [Bor06]

politische Zielvorgaben gesetzt. Diese Zielvorgaben können in Form von gesetzlichen Regelungen auf das Produkt einwirken oder in Form von Selbstverpflichtungen eines OEMs gegenüber einer politischen Regierung. Maßnahmen zur Reduzierung von Emissionen oder Vermeidung bzw. Entschärfung von Unfällen oder deren Folgen unterliegen typischerweise einem großen Einfluss der Gesetzgebung.

Auch Kommunikationsbeziehungen zu Universitäten und Forschungseinrichtungen sind essentiell. Zum einen kann ein Wissens- und Technologietransfer aus diesen Einrichtungen bei der Weiterentwicklung der Produkte helfen. Andererseits gibt es Fälle beim Entwurf sicherheitskritischer Systeme, bei dem ein OEM verpflichtet ist, den aktuellen Stand der Technik zur Entwicklung und Absicherung des Systems herangezogen zu haben.

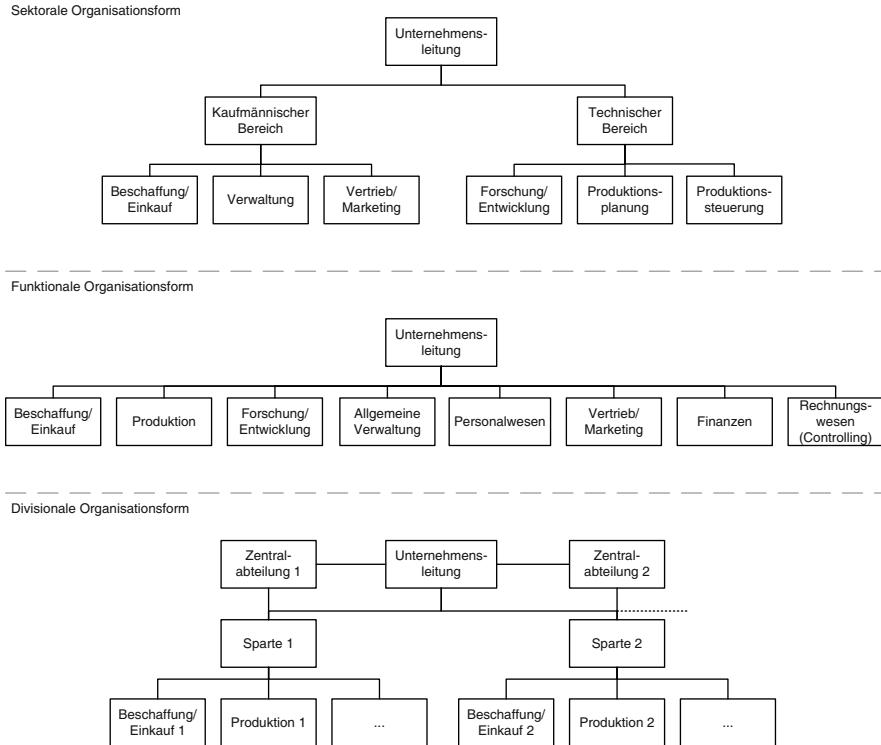

Im Folgenden soll auf die typische Organisationsform von OEMs eingegangen werden und eine detaillierte Darstellung der Struktur des Forschungs- und Entwicklungsbereiches erfolgen. Die typischen Organisationsformen für Unternehmen lassen sich in drei Ausprägungen einteilen. Die sektorale Organisation ist zumeist in kleineren und mittleren Unternehmen zu finden. Bei dieser Organisationsform sind der Unternehmensleitung ein technischer und ein kaufmännischer Bereich untergeordnet. Die zweite Ausprägung ist die funktionale Organisationsform. Hier sind

**Abb. 1.3** Typische Organisationsformen von Unternehmen. *Oben:* Sektorale Organisation mit zwei der Unternehmensleitung untergeordneten Bereichen. *Mitte:* Funktionale Organisation mit bis zu acht Bereichen, die der Unternehmensleitung unterstellt sind. *Unten:* Divisionale Organisation, welche insbesondere in großen Unternehmen zu finden ist. Der Unternehmensleitung sind sogenannte Sparten zugeordnet, die jede ihre eigene funktionale Organisation hat

der Unternehmensleitung mehrere Bereiche untergeordnet. Die Bereiche umfassen die Produktion, die Forschung/Entwicklung, das Personalwesen, die Finanzen, den Vertrieb/Marketing und den Einkauf. Diese Art der Organisationsform ist bei den meisten OEMs vorzufinden. Als dritte Ausprägung gibt es die divisionale Organisationsform, welche eine weitere Aufteilung in Form von Sparten vornimmt. Die Sparten befinden sich direkt unterhalb der Unternehmensleitung und haben dann jeweils ihre eigene funktionale Organisation. Diese Art der Organisationsform ist insbesondere bei großen Unternehmen zu finden, welche auf verschiedenen Produktfeldern tätig sind. In Abb. 1.3 sind die drei Organisationsformen dargestellt.

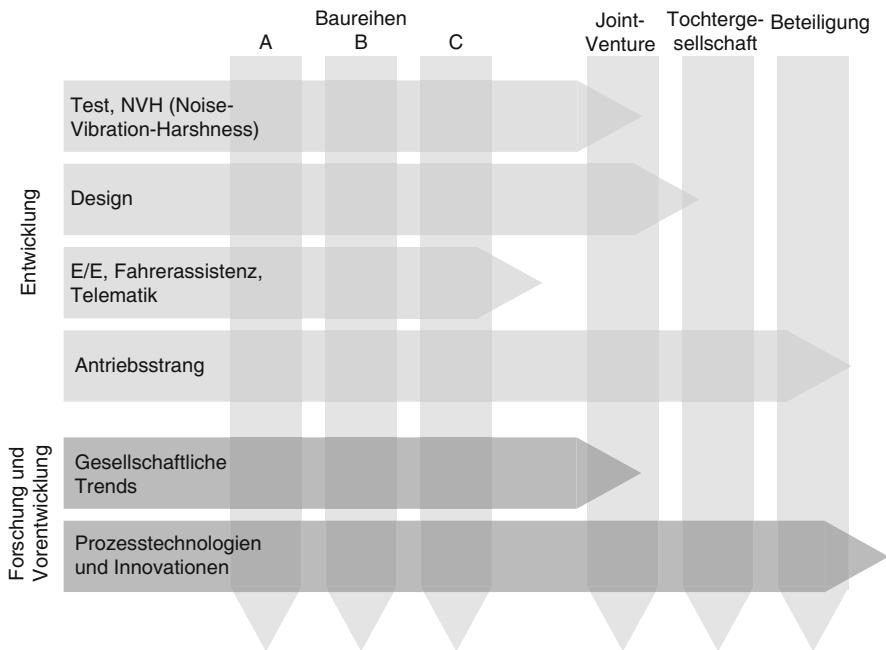

In Abb. 1.2 entspricht der Forschungs- und Entwicklungsbereich der mittleren Spalte, aus der verschiedene Baureihen hervorgehen. Bei der Forschung und Entwicklung handelt es sich um eine querschnittliche Aktivität, deren Ergebnisse sowohl in verschiedene Baureihen als auch in verschiedene Geschäftsbereiche einfließen. Durch diese matrixartige Strukturierung, die auch in Abb. 1.4 dargestellt ist, können gleiche Entwicklungsaktivitäten für verschiedene Produkte gebündelt und

**Abb. 1.4** Matrixartige Organisation, bei der Forschung, Vorentwicklung und Entwicklung übergreifend über die Produktentwicklung sowie Geschäftsbereiche agieren

Doppelentwicklungen reduziert bzw. vermieden werden. Diese Vorgehensweise hat den positiven Effekt, dass eine Art Baukasten aus Komponenten oder Baugruppen entsteht, aus der sich die einzelnen Baureihen bedienen können. Die Komponenten eines solchen Baukastens können in höherer Stückzahl und somit günstiger eingekauft werden. Weiterhin reduziert sich das Fehlerrisiko, da weniger Komponenten getestet und folglich mehr Zeit für den Gesamtsystemtest zur Verfügung steht. Die Qualität steigt tendenziell durch den Aufbau eines solchen Baukastens. Nachteilig wirkt sich die Übernahme von Komponenten jedoch durch die mangelnde Differenzierung und Individualisierung der verschiedenen Baureihen aus. Sind die Komponenten kundenerlebbar, so stellt sich einem Kunden eines Premiumfahrzeugs die Frage, ob der Preis seines Fahrzeugs gerechtfertigt sei, wenn er die gleichen Komponenten im Volumensegment wiederfindet. In der Produktgestaltung muss also auf die kundenerlebbaren Bestandteile und in der Entwicklung auf die individuelle Gestaltbarkeit von solchen Komponenten geachtet werden.

Innerhalb des Entwicklungsprozesses wird typischerweise zwischen verschiedenen Stadien einer Entwicklung unterschieden. Die Forschung ist unter zeitlichen Gesichtspunkten am weitesten von einer Produktentwicklung entfernt. Die Vorentwicklung ist dem Produktentstehungsprozess vorgelagert und die Entwicklung ist direkt an der Produktentstehung beteiligt. In der Unternehmensstruktur sind Forschung, Vorentwicklung und Entwicklung aber nicht strikt getrennt. Vielmehr wer-

den einzelne Bereiche zusammengefasst wie zum Beispiel die Vorentwicklung mit der Entwicklung oder die Forschung mit der Vorentwicklung. Das Risiko eines vollständigen Zusammenschlusses aller Bereiche kann jedoch dazu führen, dass bei Problemen in der Produktentwicklung Kapazitäten der Vorentwicklung zur Produktentwicklung verschoben werden. Für die Lösung eines Engpasses in der Entwicklung kann eine solche Maßnahme helfen. Es sollte jedoch sichergestellt werden, dass das mittel- oder langfristige Innovationspotenzial hierdurch nicht sinkt.

## 1.2 Produkt- und Entwicklungszyklen

Im vorherigen Abschnitt erfolgte die Darstellung der Zusammenhänge innerhalb eines Unternehmens und zwischen Unternehmen in einer Lieferkette. In Ansätzen wurde hierbei die Produktentstehung erläutert, diese wird im Folgenden im Detail beschrieben. Der Bereich der Elektrik/Elektronik-Entwicklung steht dabei im Fokus.

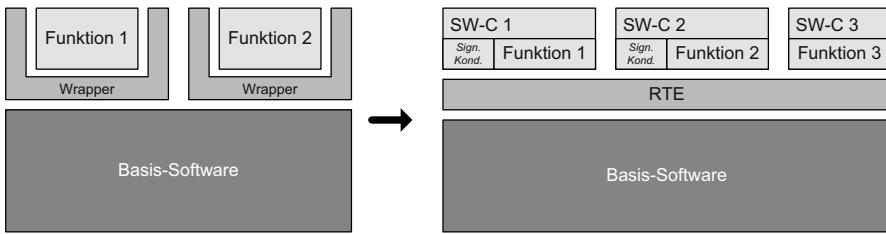

### 1.2.1 Entwicklungsprozess

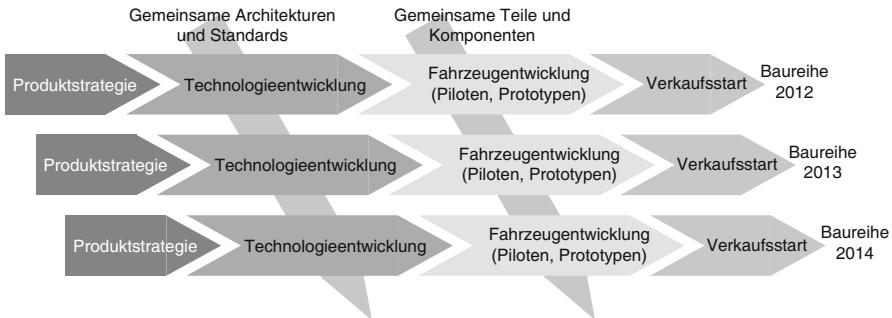

Wie ein Produktentstehungsprozess im Einzelnen verläuft und wie lange er dauert, variiert von OEM zu OEM. Es gibt allerdings gewisse Vorgehensweisen und strategische Überlegungen, die verbreitet sind. Wie in Abb. 1.5 dargestellt, gibt es vier Phasen, in die sich eine Produktentwicklung untergliedert: 1.) die Entwicklung einer Produktstrategie, 2.) die Technologieentwicklung, 3.) die Fahrzeugentwicklung und 4.) der Produktions- und Verkaufsstart. Während der Entwicklung einer Produktstrategie werden potenzielle Zielgruppen (Käufer) identifiziert, die mit einem Produkt angesprochen werden sollen. Gemäß den Wünschen dieser Zielgruppen und prognostizierten gesellschaftlichen Trends werden kundenerlebbare Funktionen und funktionale Innovationen bestimmt, die im Zusammenhang mit einem Produkt angeboten werden müssen. Weiterhin gilt es, gesetzliche Anforderungen und Einflüsse aus Standardisierungsgremien zu berücksichtigen.

Anschließend folgt die Technologieentwicklung, die auf Basis gemeinsamer Elektrik/Elektronik-Architekturen bzw. Plattformkonzepten eine spezifische Architektur ableitet, die einerseits die funktionalen Innovationen aufnehmen kann und andererseits Optimierungskriterien wie beispielsweise Kostenziele erfüllen muss. Um neue Technologien oder neue Plattformen über mehrere Baureihen hinweg auszurollen, startet man typischerweise von einer Baureihe, die als Technologieträger fungiert. Welche Baureihe sich als Technologieträger eignet hängt von verschiedenen Aspekten ab. Zum einen besteht bei neuen Technologien ein gewisses Risiko für Entwicklungsfehler, die im schlimmsten Fall durch teure aufwändige Rückrufaktionen behoben werden müssen. Eine Baureihe mit kleinen Stückzahlen reduziert zwar nicht das Risiko einer Rückrufaktion, aber dafür die Gesamtkosten, da

**Abb. 1.5** Entwicklungsphasen verschiedener Baureihen starten versetzt zueinander und gliedern sich in eine Produktstrategie, Technologieentwicklung, Fahrzeugentwicklung und einen Produktions- sowie Verkaufsstart

es evtl. weniger Fahrzeuge zu überarbeiten gilt. Andererseits sollte diese Baureihe auch als Technologieträger alle innovativen Funktionen und Technologien enthalten. Bei einer kostenoptimierten Baureihe aus dem niedelpreisigen Segment wird dies kaum der Fall sein. Vielmehr lassen sich solche Innovationen im hochpreisigen Fahrzeugsegment am besten einführen.

In der dritten Phase folgt die Fahrzeugentwicklung. In dieser Phase der Entwicklung werden Prototypen aufgebaut, um zunächst einzelne Komponenten und am Ende das gesamte Fahrzeug zu testen. Parallel zu dieser Phase starten die Aktivitäten zur Werkzeugentwicklung für die spätere Serienproduktion. Auch die Arbeitsabläufe für eine spätere Fließbandproduktion müssen vorbereitet sein, damit die Fertigungskapazitäten an die einzelnen Arbeitsschritte angepasst und die Arbeitsplätze eingerichtet werden können. Die Zeit, die von Beginn der Produktstrategie bis zum Verkaufsstart vergeht, kann von Produkt zu Produkt schwanken. Eine typische Größenordnung ist 50 Monate für eine neue Fahrzeugbaureihe. Allerdings kann auch diese Zeitspanne noch verkürzt werden, wenn es sich um eine Baureihe handelt, die in ähnlicher Form bereits auf dem Markt ist bzw. auf einer bereits existierenden Plattform aufbaut. Ein allgemeiner Trend ist die Verkürzung des Entwicklungszeitraums, um besser auf Marktbedürfnisse eingehen zu können. Gerade die Marktresonanz nach Verkaufsstart einer Baureihe enthält wichtige Informationen für eine Folgebaureihe der gleichen oder verwandter Produktklassen. In Abb. 1.5 ist der Anlauf verschiedener Baureihen zeitlich versetzt dargestellt. Durch einen solchen Versatz können einerseits die Entwicklungskapazitäten homogen ausgelastet werden und andererseits die Verkaufszahlen stabil gehalten werden. Typischerweise steigen bei Verkaufsstart die Verkaufszahlen einer Baureihe an und sinken bis zum Start des neuen Typs der gleichen Baureihe. Durch eine geschickte zeitliche Verteilung der Entwicklung und des Verkaufs von Baureihen mit großen und kleinen Stückzahlen, reduzieren sich die Schwankungen der wirtschaftlichen Kenngrößen einer Firma.

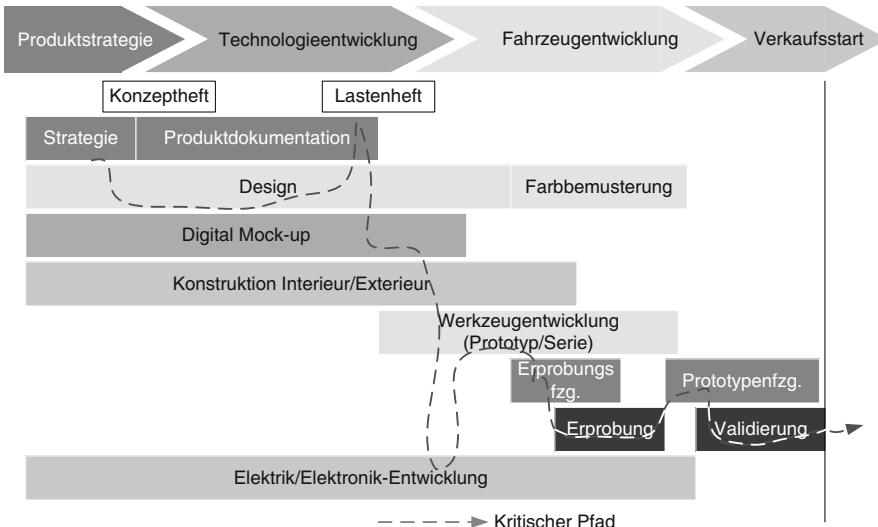

Der Entwicklungsprozess, der in Abb. 1.5 Baureihen-übergreifend dargestellt ist, ist in Abb. 1.6 für eine Baureihe detailliert aufgezeigt. Die Aktivitäten innerhalb

**Abb. 1.6** Die Entwicklung einer Baureihe besteht aus verschiedenen parallelen Entwicklungssträngen, zwischen denen Abhängigkeiten bestehen. Der kritische Pfad deutet an, welche Abhängigkeiten zu Verzögerungen der Gesamtentwicklung führen

eines solchen Prozesses starten bereits in frühen Phasen mit der Gestaltung erst des Exterieurs und dann des Interieurs eines Fahrzeugs. Weiterhin werden digitale Prototypen (Mock-up Modelle) eines Fahrzeugs entwickelt, sodass ohne den Aufbau realer Komponenten und Prototypen ein Fahrzeug erlebbar wird, technische Absicherungen durchgeführt werden können und die Konstruktion des Gesamtfahrzeugs starten kann. Eine weitere Tätigkeit, die in einer frühen Phase einer Fahrzeugentwicklung startet, ist die E/E-Entwicklung, auf die im Folgenden näher eingegangen wird. Als Ergebnis der ersten Phase muss ein Konzeptheft vorliegen, auf dessen Basis ein Lastenheft geschrieben wird. Dieses Lastenheft ist ein wesentlicher Vertragsbestandteil bei der Beauftragung von Lieferanten. Es beschreibt sämtliche Anforderungen an ein System sowie die Leistungen, die ein Lieferant zur Erfüllung seines Auftrags zu erbringen hat. Auf Basis eines Lastenhefts kann ein Zulieferer Vorschläge erarbeiten und dem OEM ein Angebot unterbreiten. Die Lösungsvorschläge, zur Erfüllung der Anforderungen aus dem Lastenheft arbeitet der Zulieferer in Form eines Pflichtenheftes aus. Da es sich bei dem Lastenheft bereits um ein wesentliches Dokument zum Vertragsabschluss handelt, werden Anforderungen in einer formalisierten Art beschrieben, mit der sich die Erfüllung leichter überprüfen lässt [IBM].

Nachdem die Beauftragung eines Lieferanten mit der Komponentenentwicklung und -herstellung erfolgt ist, können erste Muster implementiert und produziert werden, die mittels Laboraufbauten oder in Erprobungsfahrzeugen erprobt und später in Prototypen validiert werden. Parallel dazu findet im Bereich der Fahrzeuggestaltung bzw. des Designs die genaue Farbmusterung des Exterieurs und Interieurs statt.

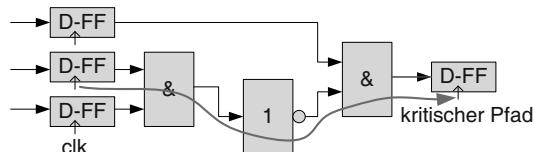

Weiterhin werden Werkzeuge für die Fertigung entwickelt und Produktionsschritte geplant. Durch die einzelnen Schritte des Entwicklungszyklus zieht sich ein kritischer Pfad, der die zeitkritischen Abhängigkeiten zwischen den einzelnen parallelen Entwicklungssträngen aufzeigt. Der kritische Pfad muss nicht wie in Abb. 1.6 verlaufen, er soll jedoch verdeutlichen, dass die Entwicklungsstränge nicht unabhängig voneinander agieren und dass sich Verzögerungen auf einem Entwicklungsstrang auch auf andere Stränge auswirken können.

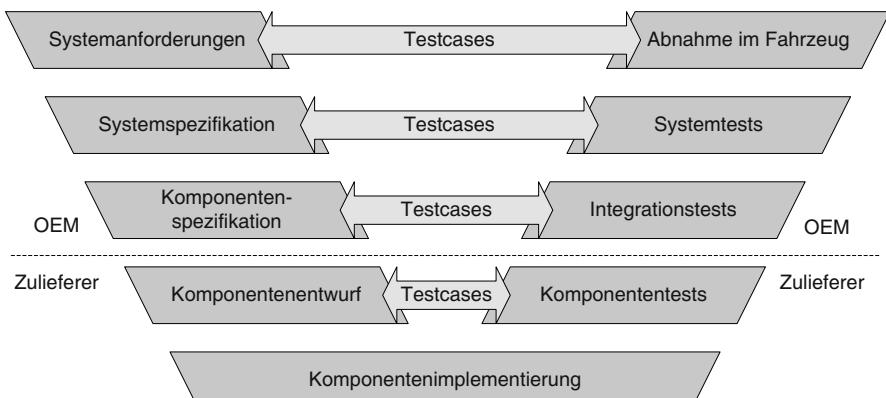

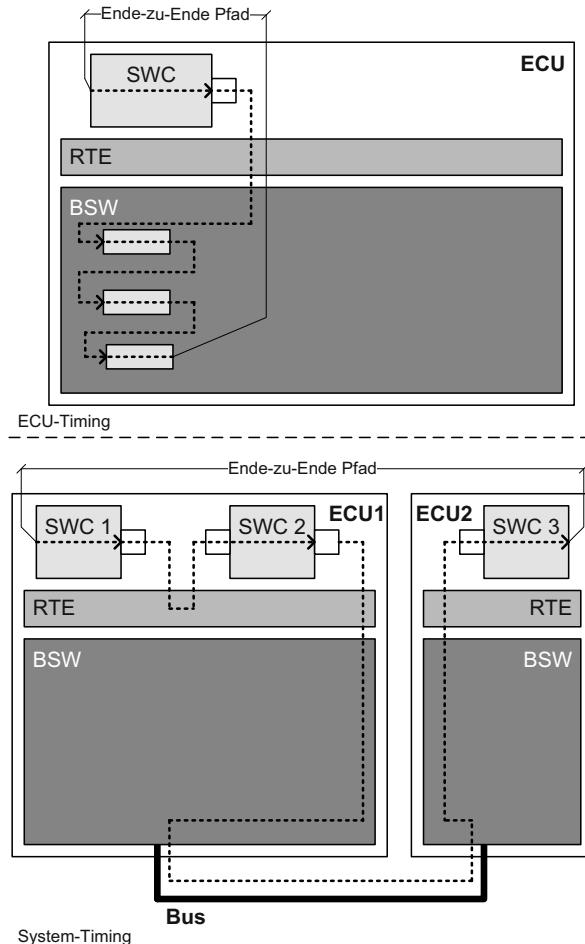

### 1.2.2 Kooperationsmodelle zwischen OEM und Zulieferer

Die Kooperationsmodelle zwischen OEM und Zulieferer lassen sich auf mehrere Arten beschreiben. Ein weitverbreitetes Modell für die Zusammenarbeit im Rahmen einer Entwicklungstätigkeit ist das sogenannte *V-Diagramm*, das in Abb. 1.7 dargestellt ist. Das V-Diagramm umreißt den Entwicklungsablauf von der Beschreibung der Systemanforderungen bis zur Abnahme im Fahrzeug [SZ05]. Von oben nach unten wird in diesem Diagramm die betrachtete Granularität immer feiner. Auf den oberen Ebenen gilt es Systemanforderungen und eine Systemspezifikation zu schreiben, während anschließend die Zerlegung eines Systems in Komponenten erfolgt. Auf unterster Ebene findet der Übergang von der Entwurfs- in die Implementierungs- bzw. Umsetzungsphase statt. Anschließend finden angefangen bei einzelnen Komponenten bis zur Abnahme im Fahrzeug Tests statt. Hierbei kommen Testfälle zum Einsatz, mit denen die beschriebenen Eigenschaften in einer Systemspezifikation mit den tatsächlichen Eigenschaften des implementierten Systems überprüft werden. Eine übliche Trennung der Arbeitsschritte zwischen OEM und Zulieferer findet auf Komponentenebene statt. Der OEM über-

**Abb. 1.7** Das V-Diagramm ist eine typische Darstellung, um die einzelnen Entwicklungsschritte in die Bereiche Spezifikation (linke Hälfte) und Test (rechte Hälfte) auf unterschiedlichen Systemebenen zu unterteilen

gibt dem Zulieferer eine Komponentenspezifikation, die auch bereits ausführbare Simulationsmodelle enthalten kann und erhält getestete Komponenten zurück, die erst mit anderen Komponenten sowie in virtuellen Fahrzeugumgebungen getestet werden. Anschließend erfolgt die Integration in Fahrzeuge und Prototypen. Dieses Zusammenspiel aus spezifizieren, implementieren und testen, ist für die Entwicklung elektrisch/elektronischer Komponenten typisch. In einigen Bereichen, wie beispielsweise bei Teilen des Rohbaus oder mechanischen Komponenten liegt die Entwicklungs- und Fertigungsverantwortung zum großen Teil beim OEM. In anderen Bereichen ist der Zulieferer stärker involviert.

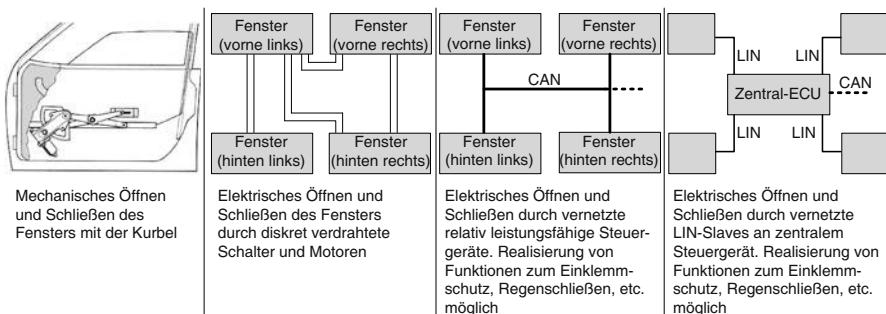

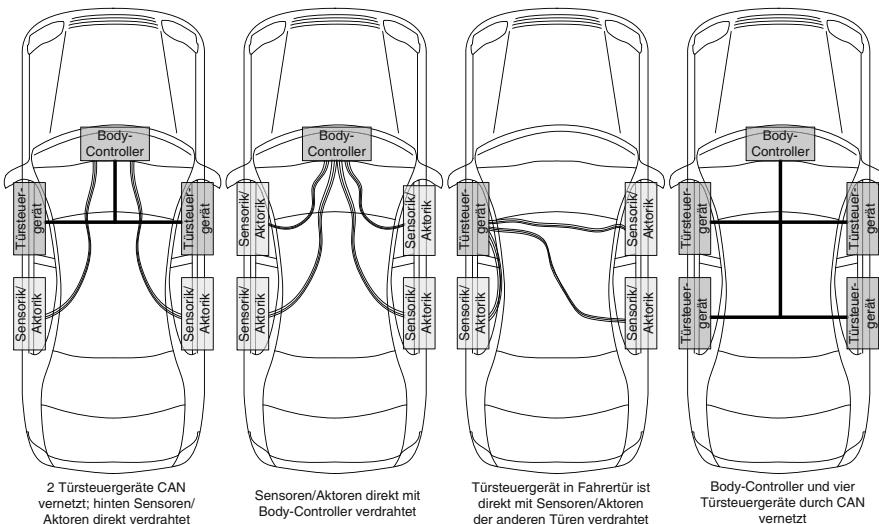

## 1.3 Historische Entwicklung der Elektronik im Kraftfahrzeug

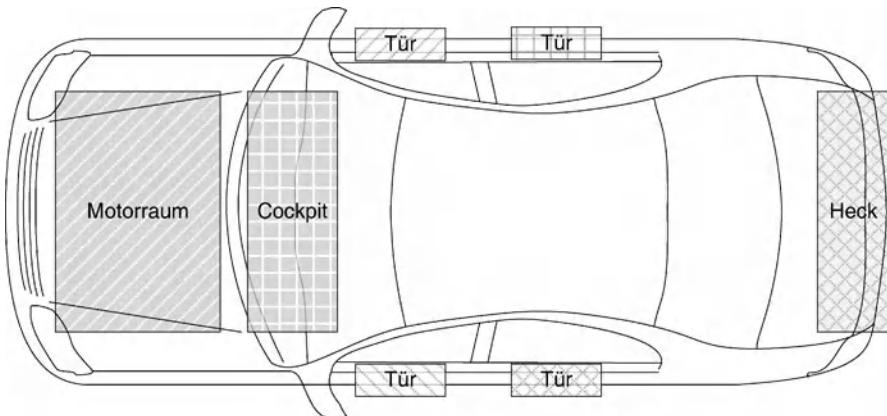

Die elektronische Entwicklung im Fahrzeug durchlebt seit Jahren einen kontinuierlichen Aufwärtstrend. Nicht nur neue Funktionalität wird auf Basis von eingebetteter Elektronik implementiert, auch Systeme die ursprünglich rein mechanisch funktionierten, sind in vielen Bereichen durch vernetzte mechatronische Systeme realisiert. Ein einfaches Beispiel ist in Abb. 1.8 dargestellt. Es zeigt die Entwicklung von einer rein mechanischen Lösung eines Fensterhebers zu einer vernetzten Lösung, bei der die Funktion zur Steuerung eines Fensterhebermotors auf einem unabhängigen Steuergerät läuft, das auch andere Funktionen ausführen kann. Bevor jedoch vernetzte Systeme zur Ansteuerung des Fensterhebers eingesetzt wurden, kamen elektrische Lösungen zum Einsatz, bei denen die einzelnen Motoren an den Fenstern diskret mit Schaltern verkabelt waren. Heutiger Stand ist bei einigen Premiumfahrzeugen ein Ansatz, bei dem die Fensterhebersteuerung über Türsteuergeräte in jeder Tür realisiert ist. Die Türsteuergeräte sind untereinander vernetzt und können auch auf andere Informationen des Fahrzeugzustands zugreifen. Hierdurch sind neben dem Öffnen und Schließen eines Fensters auch Funktionen wie Einklemmschutz, Regenschließen oder Schließen des Fensters über eine Fernsteuerung möglich. Der bereits erwähnte Fall, bei dem die Türsteuergeräte durch einfache LIN-Slaves ersetzt

**Abb. 1.8** Beispiel eines Fensterhebers, der in Form einer mechanischen, elektrischen und zwei elektronischen Lösungen realisiert ist

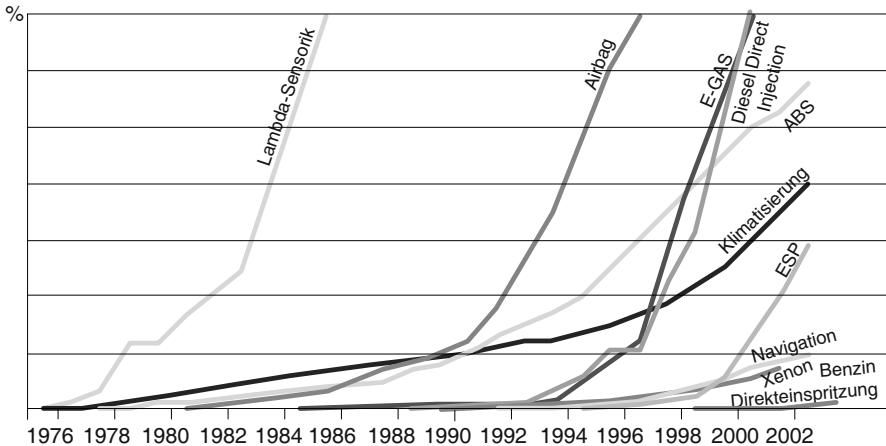

Abb. 1.9 Marktdurchdringung verschiedener elektrisch/elektronischer Komponenten im Fahrzeug [Kal06]

sind und die Funktionen auf einem generischen Steuergerät laufen, deutet einen neuen Trend an. Funktionen, die in Software auf einem Mikrocontroller partitioniert sind, müssen nicht zwangsläufig auf einem Steuergerät für eine Gruppe von Sensoren und Aktoren laufen. Stattdessen kann solche Software-Funktionalität irgendwo im Netzwerk partitioniert sein, wo entsprechende Rechenkapazität verfügbar ist. An diesem Spektrum von Implementierungsmöglichkeiten ist gut zu erkennen wie groß und interdisziplinär der Lösungsraum für eine einfache Funktion sein kann.

Neben der Ergänzung von mechanischen Komponenten um elektrische Steuerungen oder Regelungen, sind etliche neue Funktionen in Fahrzeuge integriert worden. Die Integration einiger Funktionen hat nach einer gewissen Einführungszeit eine exponentielle Marktdurchdringung erreicht. Ein paar Beispiele, bei denen es dieses rasante Wachstum gab, sind qualitativ in Abb. 1.9 dargestellt.

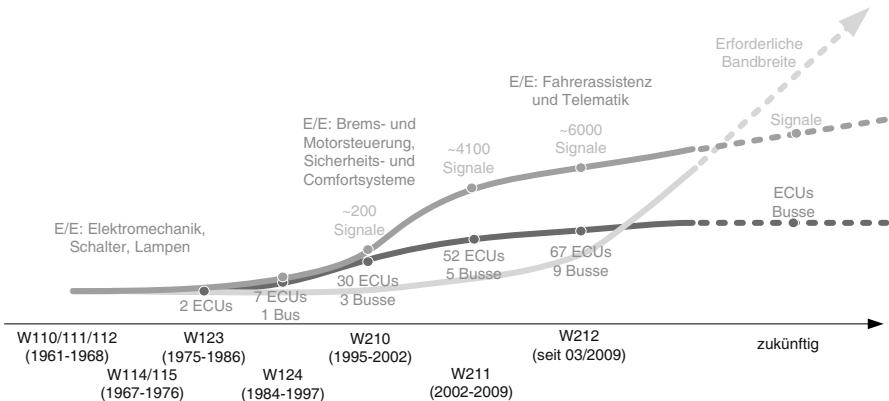

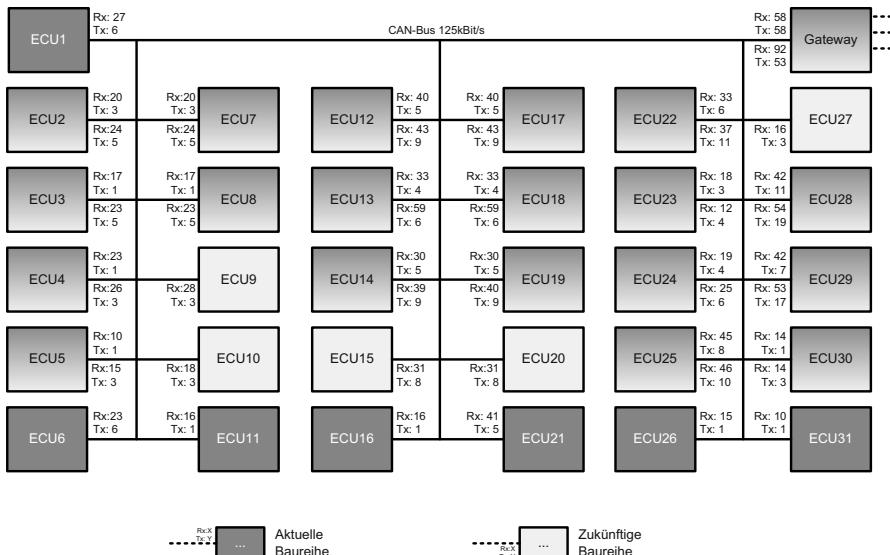

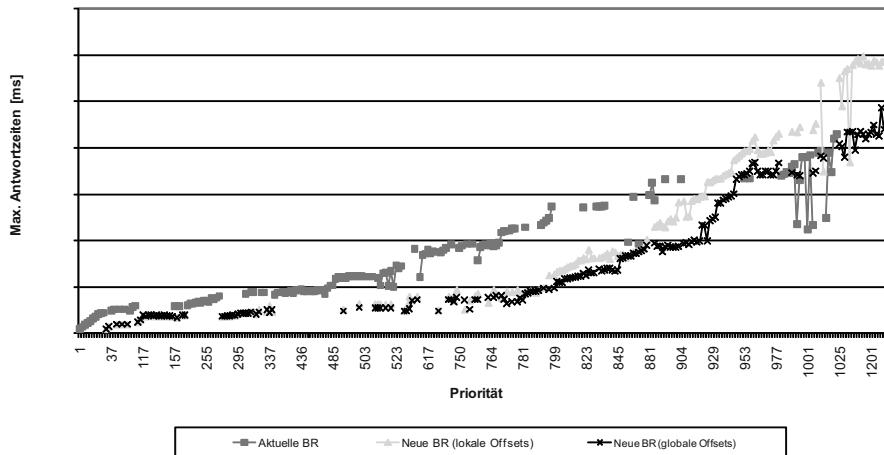

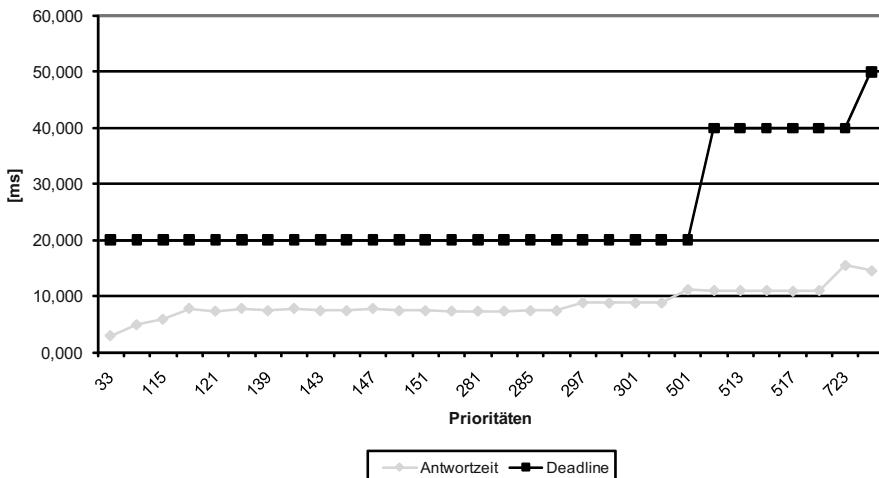

Die Konsequenz aus der steigenden Anzahl an Funktionen im Fahrzeug, ist ein wachsender Bedarf an vernetzten elektronischen Komponenten. Abbildung 1.10 zeigt wie sich im Premiumsegment die Anzahl an Steuergeräten entwickelt hat. Angefangen bei zwei nicht vernetzten Steuergeräten (engl. Electronic Control Units, kurz ECUs) sind in der folgenden Baureihe bereits sieben über einen Bus vernetzte ECUs verbaut worden. Im Laufe der Jahre hat die Anzahl an Steuergeräten zugenommen und beträgt heute knapp 70 Steuergeräte, die über neun Busse verbunden sind. Gleichzeitig hat die Anzahl an Signalen zugenommen, die über diese Busse übertragen werden. Die Treiber hinter dieser Entwicklung kamen zunächst aus dem Bereich der Motorsteuerung, der Sicherheits- sowie der Komfortsysteme. Aktuell sind die Technologietreiber im Bereich der Fahrerassistenz und im Bereich der Telematik sowie der Infotainment-Systeme zu finden. In diesem Bereich ändert sich der Typ an Daten, die es zu übertragen gilt. Statt einfachen Signalen, die zum Teil 1-Bit-Werte – wie Schalter *an* oder *aus* – sind, müssen Streaming-Daten übertragen werden. Hierunter fallen Audio- oder Videodaten aus Medienquellen oder Kame-

**Abb. 1.10** Dargestellt ist die Anzahl der Steuergeräte und Signale sowie die benötigte Bandbreite über der Zeit [Rei10]. Interessant an dieser Darstellung ist der starke Anstieg an benötigter Bandbreite. Statt einfacher Signale bestehend aus wenigen Bits, werden zunehmend Streaming-Daten von komplexen Sensoren und Kameras verschickt

rasystemen sowie Menülisten und Objektdaten. Mit anderen Worten, es steigt nicht nur das Signalaufkommen, es steigt auch die Komplexität der Daten und somit auch die benötigte Bandbreite.

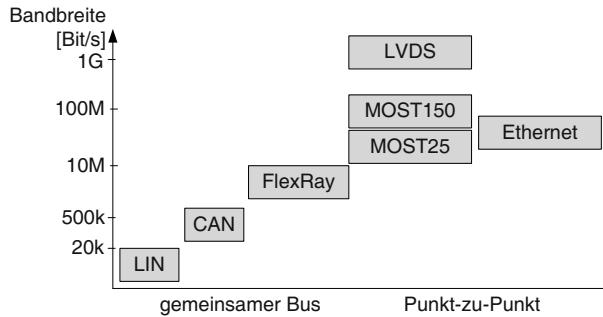

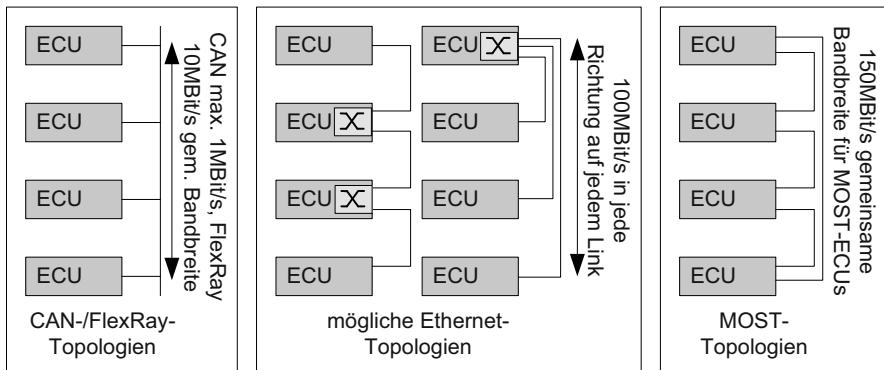

Aus der steigenden Anzahl an Signalen und dem steigenden Bandbreitenbedarf ergeben sich neue Anforderungen an die Kommunikationstechnologien im Fahrzeug. Während mit den heutigen Automotive-Technologien wie *Local Interconnect Network (LIN)*, *Controller Area Network (CAN)* und *FlexRay Bus*-Topologien mit bis zu 10MBit/s Bandbreite aufgebaut werden können, muss bei höheren Bandbreiten ein Wechsel zu Punkt-zu-Punkt-Topologien stattfinden. Der *MOST25-Standard (Media Oriented System Transport)*, der eine Bandbreite von 25 MBit/s bietet, ist auf physikalischer Ebene eine Punkt-zu-Punkt-Topologie, die ringförmig aufgebaut ist. Gleiches gilt für *Ethernet*, bei dem End-Knoten über Switches miteinander verbunden sind. Durch diese Switches werden Punkt-zu-Punkt-Topologien erzeugt und Arbitrierungsmechanismen in einer Kollisionsdomäne überflüssig. Wie in Abb. 1.11 dargestellt, findet mit den heute verfügbaren Technologien zwischen 10MBit/s und 25 MBit/s ein Umbruch in der Topologieauslegung statt: anstelle von Bustopologien kommen bei höheren Bandbreiten Punkt-zu-Punkt-Topologien zum Einsatz.

Ein weiterer Trend, der sich auf die Kommunikation bezieht und noch nicht in Abb. 1.10 enthalten ist, betrifft die Fahrzeug-übergreifende Kommunikation. Bislang ist die Fahrzeugelektronik als abgeschlossenes System vorgestellt worden, das statisch während einer Entwicklungsphase konzipiert und abgesichert wird. Der Trend geht jedoch zu einer Öffnung dieses Systems. Zum einen werden vermehrt Schnittstellen ins Auto integriert, die eine Kommunikation zwischen dem Fahrzeug und der Umwelt ermöglichen. Hierzu gehört die Kommunikation zwischen Elektrofahrzeugen und Ladesäulen, der Datenaustausch zwischen den einzelnen Fahrzeugen selber, um sich gegenseitig beispielsweise vor Gefahren auf einer Strecke zu warnen oder die Möglichkeit Notrufe und Ferndiagnosen über Funkschnittstellen

**Abb. 1.11** Die Zunahme an Bandbreite ist verbunden mit einer Änderung der Vernetzungsarchitektur, da mit steigender Bandbreite kein gemeinsamer Bus, sondern Punkt-zu-Punkt-Topologien notwendig sind

durchzuführen. Neben diesen Schnittstellen eines Fahrzeugs nach außen, soll der Kunde auch die Möglichkeit bekommen eigene elektronische Geräte (CE-Geräte) im Fahrzeug zu integrieren, was zu einem gewissen Dilemma führt. Während die Automobilelektronik eine Lebensdauer von bis zu 30 Jahren haben kann, ändert sich die *Consumer Electronic* in deutlich kürzeren Zyklen. Somit müssen Integrationskonzepte entwickelt werden, die flexibel genug sind während der Laufzeit eines Fahrzeuges Update-Möglichkeiten für unklare oder gar unbekannte Trends der CE-Geräte vorzusehen.

# **Kapitel 2**

## **Grundlagen der**

## **Elektrik/Elektronik-Architekturen**

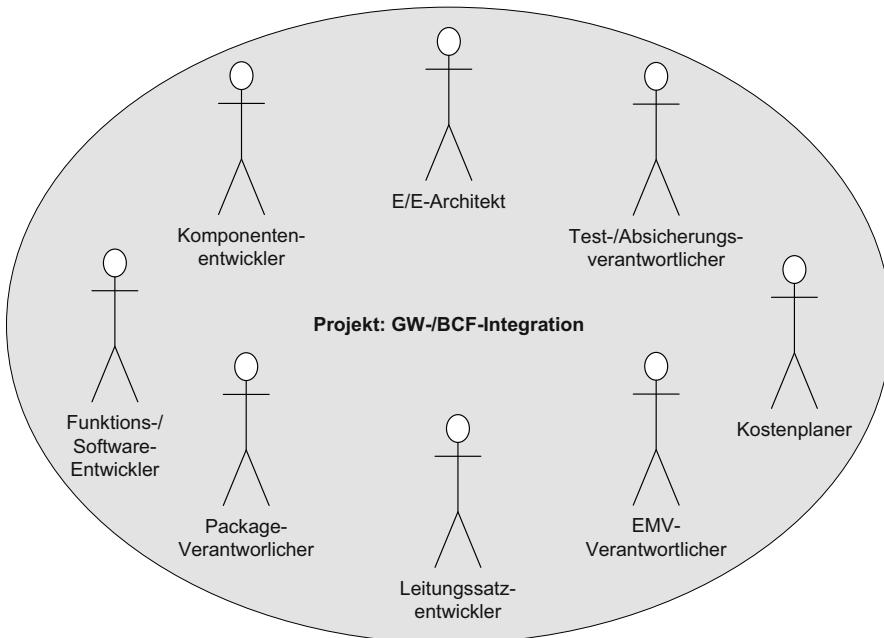

Der Entwurf und die Entwicklung von E/E-Architekturen ist ein vielschichtiger Prozess, an dem viele Fachbereiche aus verschiedenen Organisationseinheiten eines Unternehmens beteiligt sind. Die Entwicklung der E/E-Architektur findet hierbei in einem E/E-Fachbereich statt, dessen Entwickler von anderen nicht E/E-Fachabteilungen unterstützt werden. Der Vertrieb liefert beispielsweise Kennzahlen für Verbauquoten von Funktionen. Die Produktstrategie stellt Anforderungen, welche von einem zukünftigen Fahrzeug zu erfüllen sind. Die Kostenplaner unterstützen bei der Kostenabschätzung und -planung von Baugruppen sowie elektronischen Systemen. Weitere Fachbereiche kümmern sich um konstruktive Aspekte wie Bauräume, die für die E/E-Komponenten notwendig sind oder beschäftigen sich mit der Bestimmung von Umweltanforderungen wie Temperatur, Feuchtigkeit und Vibration. Unter Berücksichtigung dieser verschiedenen Einflüsse muss ein E/E-Entwickler einen Funktionsumfang ins Auto integrieren.

Bei dieser Integration muss entschieden werden, ob die Funktionen auf einem oder sogar mehreren Steuergeräten ausgeführt werden, welche Sensorik, Aktorik notwendig ist und wo diese E/E-Komponenten verbaut werden. Die Komponenten müssen wiederum im Auto Daten austauschen, mit elektrischer Leistung versorgt werden und mitsamt ihrer Versorgungs- sowie Kommunikationsleitungen in vorgegebene Bauräume passen. Bei der Bearbeitung dieser einzelnen Themen ist nicht nur auf eine korrekte Implementierung und Integration zu achten, vielmehr muss gezeigt werden, dass eine fehlerfreie Integration der Komponenten als Teilsystem möglich ist. Hierfür können in der frühen Entwicklungsphase Bewertungsmetriken verwendet werden, um eine Aussage über die Qualität und die Abdeckung der Anforderungen liefern zu können.

### **2.1 Ebenen der E/E-Architektur**

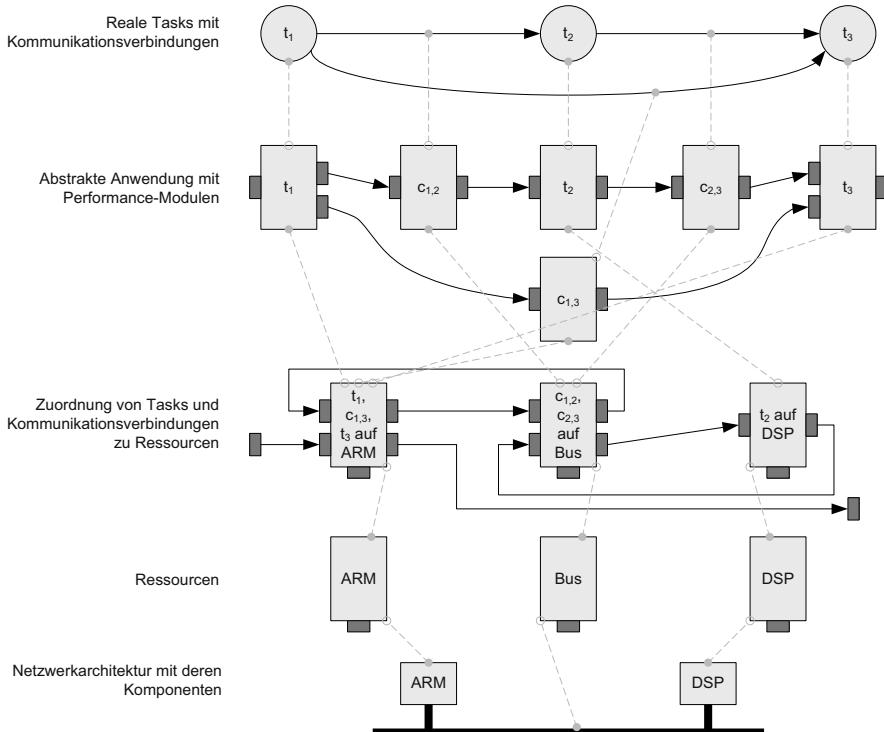

Für eine strukturierte Beschreibung der verschiedenen miteinander verzahnten Aspekte in einem Entwurfsprozess hat sich ein Modell etabliert, welches die Möglich-

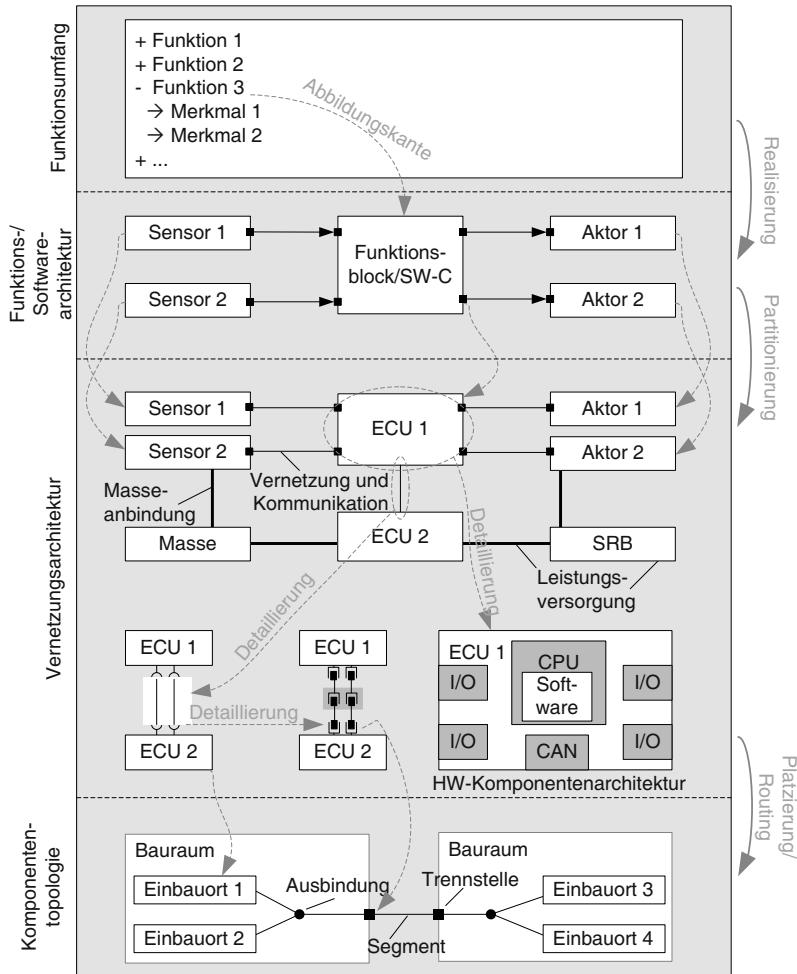

**Abb. 2.1** Eine E/E-Architektur besteht aus vier Systemebenen: 1.) der kundenerlebbare Funktionsumfang, 2.) der Funktions-/Softwarearchitektur, 3.) der Vernetzungsarchitektur und 4.) der Komponententopologie

keit bietet, eine E/E-Architektur auf Basis von verschiedenen Ebenen strukturiert beschreiben zu können. Jede dieser Ebenen entspricht einer spezifischen Sicht, die Produktstrategen, Kunden oder Entwickler auf eine E/E-Architektur haben. Da zwischen diesen Ebenen Abhängigkeiten bestehen, werden diese Abhängigkeiten in einem Modell mit vier Systemebenen beschrieben, das in Abb. 2.1 gezeigt ist.

Auf oberster Ebene befindet sich der *Funktionsumfang*, also eine Liste mit *Funktionen*, die hierarchisch aufgebaut ist. Eine Funktion kann dabei anhand von mehreren *Merkmalen* weiter untergliedert werden. Auf der darunterliegenden Ebene – der sogenannten *Funktions-/Softwarearchitektur* – werden diese Funktion durch

|                     | Komponenten                                                                    | Verbindungslogik | Schaltplan<br>Technologiebezogen | Layout | Produkt |

|---------------------|--------------------------------------------------------------------------------|------------------|----------------------------------|--------|---------|

| Halbleiterindustrie | Building Blocks<br>                                                            |                  |                                  |        |         |

| Elektronik          | Transistoren<br>ICs<br>Widerstände<br>Kondensatoren<br>Dioden<br>...           |                  |                                  |        |         |

| Fahrzeug E/E        | Steuergeräte<br>Aktuatoren<br>Sensoren<br>Schalter<br>Motoren<br>Relais<br>... |                  |                                  |        |         |

Abb. 2.2 Analogie zwischen den Systemebenen im E/E-Architekturentwurf und anderen Bereichen der Elektronikentwicklung [Hen09]

einzelne Funktionsblöcke (Sensor, Funktion, Aktor) nach dem sogenannten *EFA-Prinzip (Eingabe-Funktion-Ausgabe)* mit ihren Datenabhängigkeiten dargestellt. Die einzelnen Funktionsblöcke sind dabei noch technologieunabhängig. Zwischen diesen beiden Ebenen gibt es Abbildungskanten, mit denen ausgedrückt wird, welche Funktionsblöcke zur Realisierung einer Funktion notwendig sind. Im Laufe des Entwicklungsprozesses entspricht ein solcher Funktionsblock genau dem Umfang einer Software-Komponente inklusive ihrer Schnittstellen.

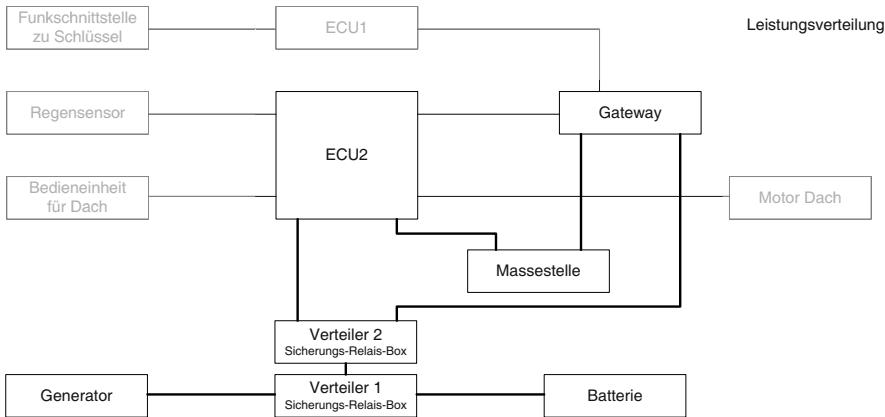

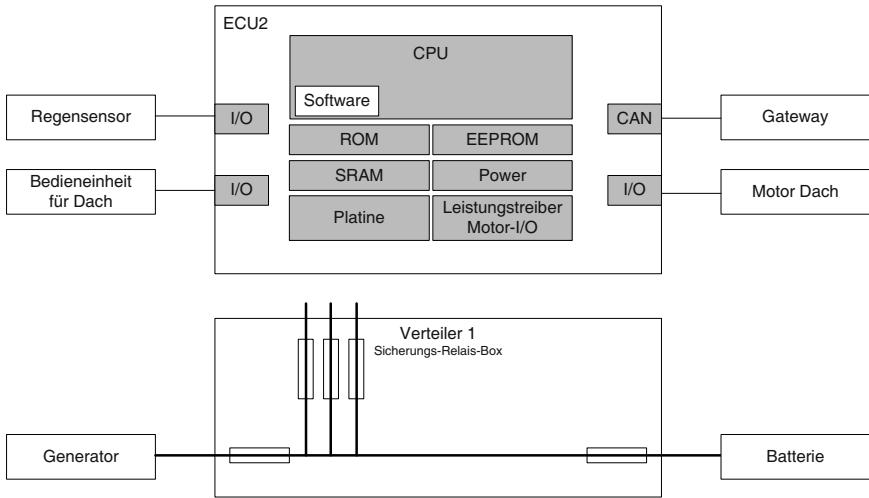

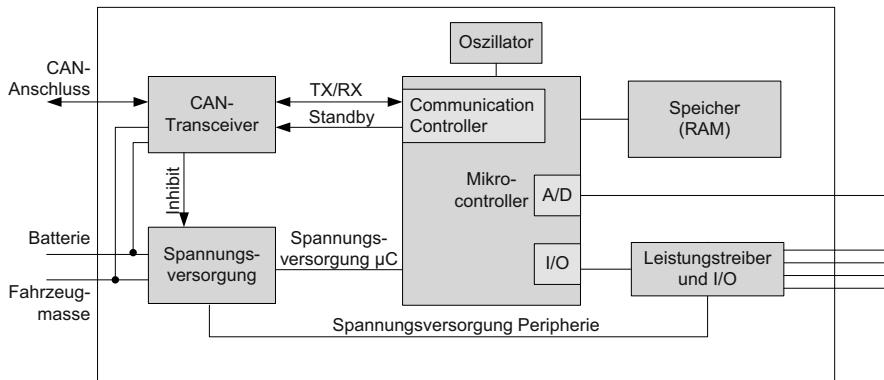

Auf der nächsten Ebene werden die einzelnen Software-Komponenten auf die Hardware-Komponenten (Sensor, ECU, Aktor) partitioniert. Für diese Zuordnung gibt es wiederum Abbildungskanten zwischen der Funktions-/Software-Architekturebene und der *Vernetzungsarchitekturebene*. Bei dieser Zuordnung von Software-Komponenten auf die Hardware-Komponenten muss sichergestellt werden, dass sämtliche Datenabhängigkeiten auf die Kommunikationsressourcen der Vernetzungsarchitektur abgebildet werden können. Damit die Hardware-Komponenten funktionieren, müssen sie mit elektrischer Leistung versorgt werden, was in einem Modell zur *Leistungsversorgung* beschrieben wird. Außerdem kann die Vernetzungsarchitektur noch in eine sogenannte *Hardware-Komponentenarchitektur* und in den *Leitungssatz* verfeinert werden. Diese Hardware-Komponentenarchitektur beschreibt das Innenleben eines Steuergeräts, eines komplexen Sensors oder Aktors.

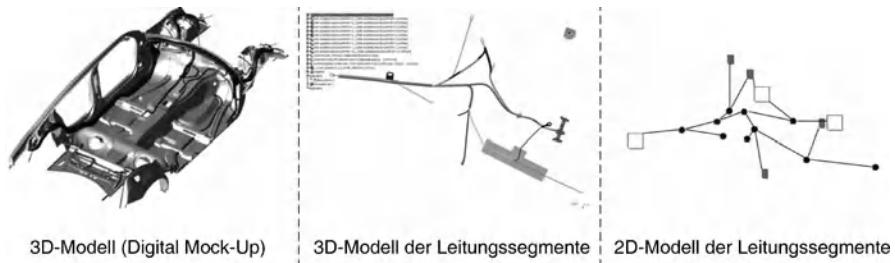

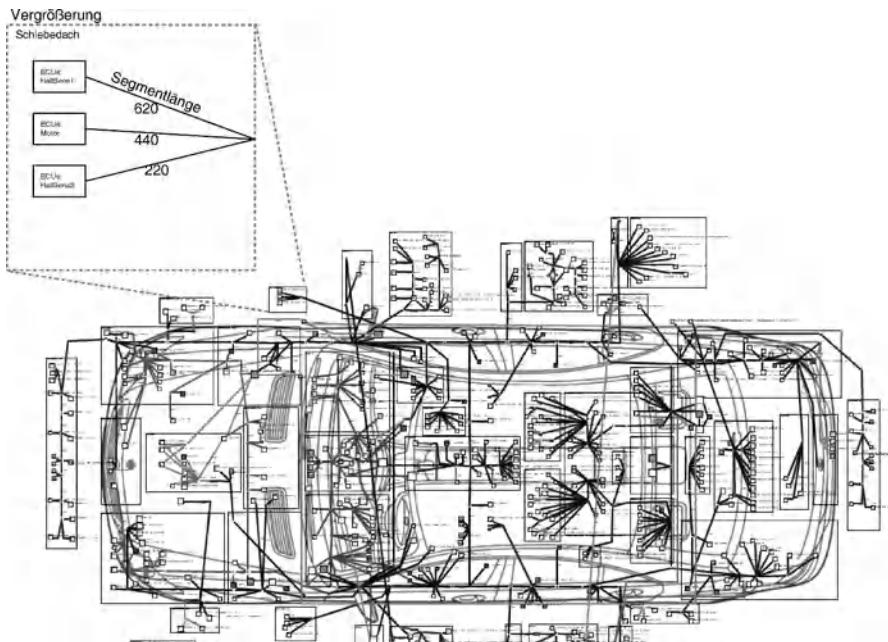

Auf der untersten Ebene in Abb. 2.1 befindet sich die *Komponententopologie*. Auf dieser Ebene werden die Hardware-Komponenten der Vernetzungsarchitektur auf Bauräume abgebildet und die Leitungen für die Vernetzung, Kommunikation und Leistungsversorgung entlang vorgegebener Verlegewege geroutet.

Als Analogie zu den Systemebenen im E/E-Architekturentwicklungsprozess gibt es auch in anderen Bereichen der Elektronikentwicklung vergleichbare Schichtenmodelle. In Abb. 2.2 ist ein Ausschnitt aus den Systemebenen der Halbleiterindus-

trie dargestellt. Hier werden zunächst funktionale Komponenten – also Logik oder existierende IP-Blöcke – ausgewählt und miteinander verbunden. Je nach Technologie findet dann die *Synthese* und das *Floorplanning* statt, bevor die Maskensätze für die Produktion hergestellt werden können. Beim Platinenentwurf verhält es sich ähnlich: Die funktionalen Komponenten sind hierbei Kondensatoren, Widerstände, ICs, etc., die in einem Schaltplan sowohl logisch wie auch elektrisch miteinander verbunden werden. Anschließend erfolgt das Layout und Routing auf den einzelnen Platinenlagen sowie die Produktion, in der die Platinen geätzt und bestückt werden.

Die genaue Beschreibung der Objekte und deren Eigenschaften, die auf den einzelnen Ebenen spezifiziert bzw. modelliert werden können, erfolgt nun in den folgenden Abschnitten.

### 2.1.1 Funktionsumfang

Der Funktionsumfang eines Fahrzeugs umfasst sämtliche kundenerlebbaren Funktionen (Ausstattungen). Bei vielen Fahrzeugtypen besteht dieser Funktionsumfang aus einem Basisumfang an kundenerlebbaren Funktionen (Basisausstattung), der mit Sonderausstattungen erweitert werden kann. Hierbei kann es vorkommen, dass gewisse Abhängigkeiten zwischen den einzelnen Ausstattungen existieren, ein Kunde wählt also eine Ausstattung aus und muss eine andere hinzunehmen. Diese Abhängigkeit kann sowohl technische als auch wirtschaftliche Gründe haben. Ein Schiebedach kann zum Beispiel den Regensor des automatischen Scheibenwischers benötigen, um bei Regen automatisch zu schließen. Hierdurch entsteht eine technische Abhängigkeit. Wirtschaftliche Abhängigkeiten entstehen dann, wenn eine Ausstattung nur zu sehr hohen Kosten integrierbar ist, die einem Kunden schwer vermittelbar wären. In einer Mischkalkulation aus zwei oder mehreren Ausstattungen können diese hohen Kosten auf alle Ausstattungen (Funktionen) umgelegt werden. Aus logischer Sicht sind solche Abhängigkeiten zwischen den Funktionen als Implikation zu betrachten: Funktion X → Funktion Y. Neben dieser Implikation gibt es auch den umgekehrten Fall, in dem sich zwei Ausstattungen gegenseitig ausschließen. Für die Ausstattung Halogen- und Xenon-Scheinwerfer ist dies ganz offensichtlich der Fall. Dieser gegenseitige Ausschluss entspricht einem logischen Exklusiv-Oder: Funktion X ⊕ Funktion Y.

Eine kundenerlebbare Funktion hat eine Menge an sogenannten kundenerlebbaren Anforderungen und nicht-kundenerlebbaren Anforderungen zu erfüllen. Ein Beispiel für eine solche kundenerlebbare Anforderung ist: *Nach Betätigung des Fensterhebers muss nach maximal 100 ms eine Reaktion des Fensters erfolgen*. Zu den nicht-kundenerlebbaren Anforderungen zählen u. a. rein technische Anforderungen oder Anforderungen, die sich aus Gesetzen ergeben.

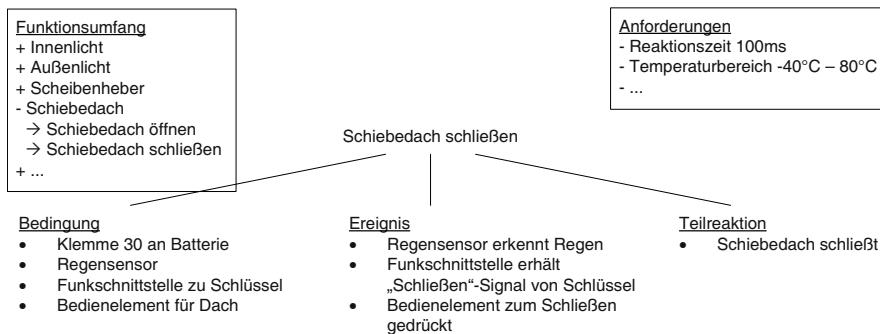

Wie in Abb. 2.3 dargestellt, besteht die Beschreibung des Funktionsumfanges aus mehreren Bestandteilen: 1.) der Auflistung von Funktionen bzw. Ausstattungen mit deren Merkmalen sowie 2.) der Menge von Anforderungen an eine Funktion. Die Funktion Schiebedach hat das Merkmal *Schiebedach öffnen* und *Schiebe-*

**Abb. 2.3** Gezeigt ist das Funktionsmerkmal *Schiebedach schließen*. Die Bedingungen müssen erfüllt sein, damit das Funktionsmerkmal ausführbar ist. Die Ereignisse führen zu einem Auslösen des Funktionsmerkmals und die Teilreaktion beschreibt die Reaktion auf ein Ereignis

*dach schließen*. Für das Merkmal *Schiebedach schließen* können 1.) Bedingungen, 2.) auslösende Ereignisse und 3.) Teilreaktionen definiert werden.

### 2.1.2 Funktions-/Softwarearchitektur

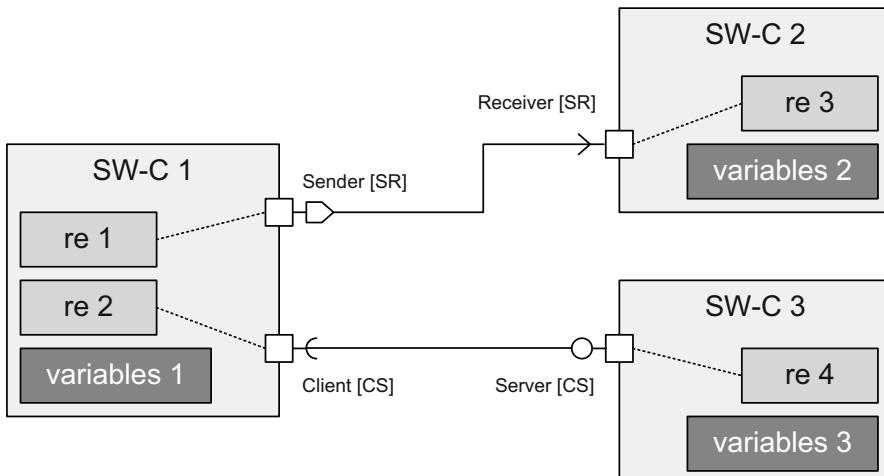

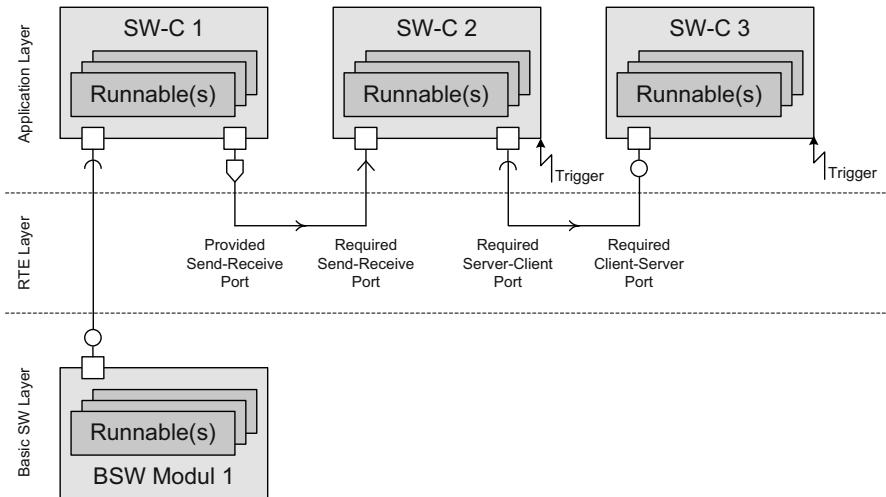

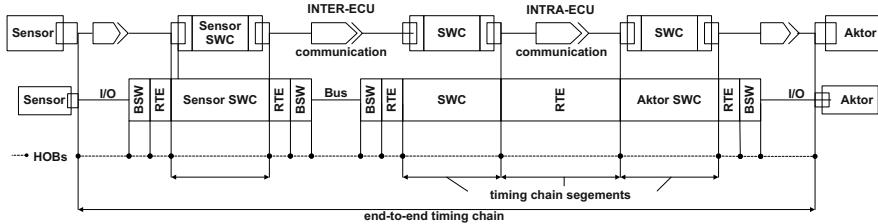

Der Funktionsumfang eines Fahrzeugs mit seinen Funktionen (Ausstattungen) muss in einem nächsten Schritt als *Funktions-/Softwarearchitektur* modelliert werden. Die Funktions-/Softwarearchitektur besteht aus *Funktions-, Sensor- und Aktorblöcken* sowie *Verbindungen*, mit denen die Blöcke logisch verknüpft werden. Funktionsblöcke haben die Eigenschaft, dass sie eingehende Daten verarbeiten und anschließend wieder ausgeben. Hierbei spielt das genaue Verfahren zur Datenverarbeitung, das durch den Funktionsblock repräsentiert wird noch keine Rolle. Vielmehr ist ein Funktionsblock durch seine Schnittstelle charakterisiert – also die Art der Ports (Ein-/Ausgang), dem Datentyp der Werte und dem Datenaufkommen an einem Port. Gleiches gilt für Sensor- und Aktorblöcke, allerdings verfügen sie nur über Ausgangs- bzw. nur über Eingangssports und fungieren somit als Datenquelle oder Datensenke. Die Aus- und Eingangssports dieser drei Blocktypen werden durch logische Verbindungen verknüpft. Auf dieser Systemebene kann bereits festlegt werden, um welche Art der Kommunikation es sich handelt also eine Client-Server-Kommunikation, bei der ein Client einen Server nach einem Ergebnis fragt oder eine Sender-Receiver-Kommunikation, bei der ein Receiver immer das entgegennehmen muss, was der Sender ihm schickt. Weiterhin steht durch die logischen Verbindungen auch fest, welche Daten zwischen bestimmten Kommunikationsblöcken ausgetauscht werden. So können auf dieser Ebene bereits Funktionen mit hohem Kommunikationsaufkommen geclustert werden. Außerdem kann mit diesen Informationen später abgeschätzt werden wie hoch das Kommunikationsaufkommen innerhalb einer ECU oder auf Bussen zwischen den ECUs ist.

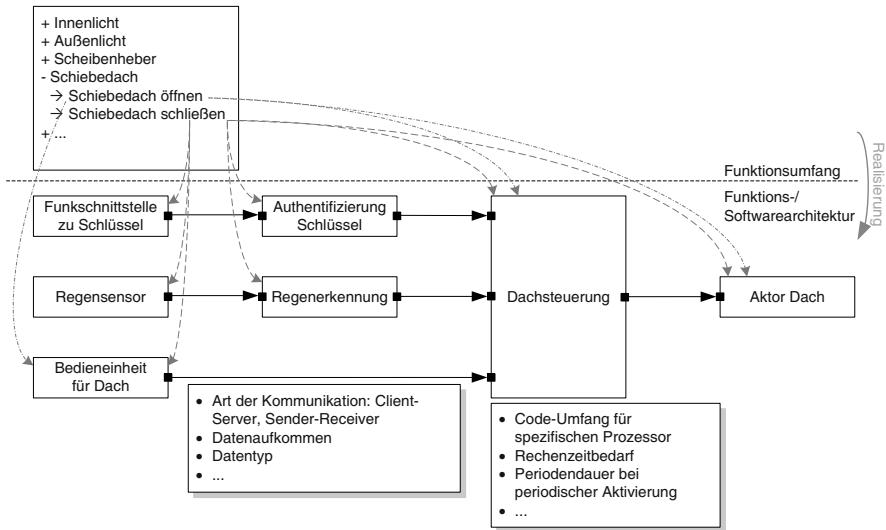

**Abb. 2.4** Eine Funktions-/Softwarearchitektur besteht aus Funktionsblöcken, die über Ports und Verbindungen Daten austauschen. Die Funktionsblöcke werden den Funktionen und Funktionsmerkmalen der oberen Systemebene zugeordnet. Im gezeigten Beispiel benötigt das Funktionsmerkmal Schiebedach schließen alle Funktionsblöcke, während das Funktionsmerkmal Schiebedach öffnen auf den Regensor und die Funkschnittstelle verzichten kann

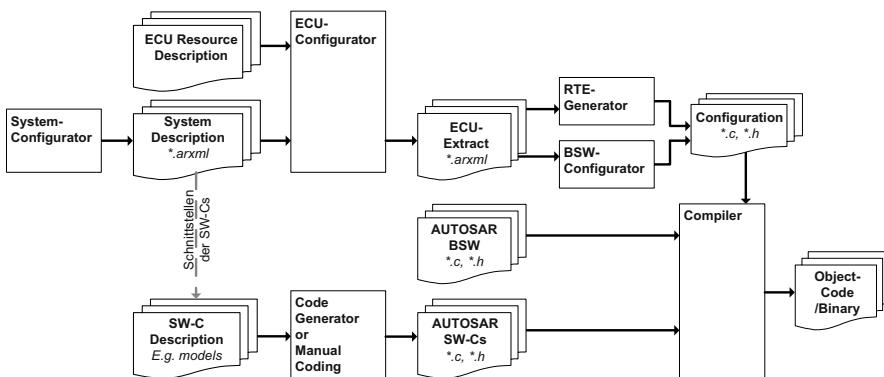

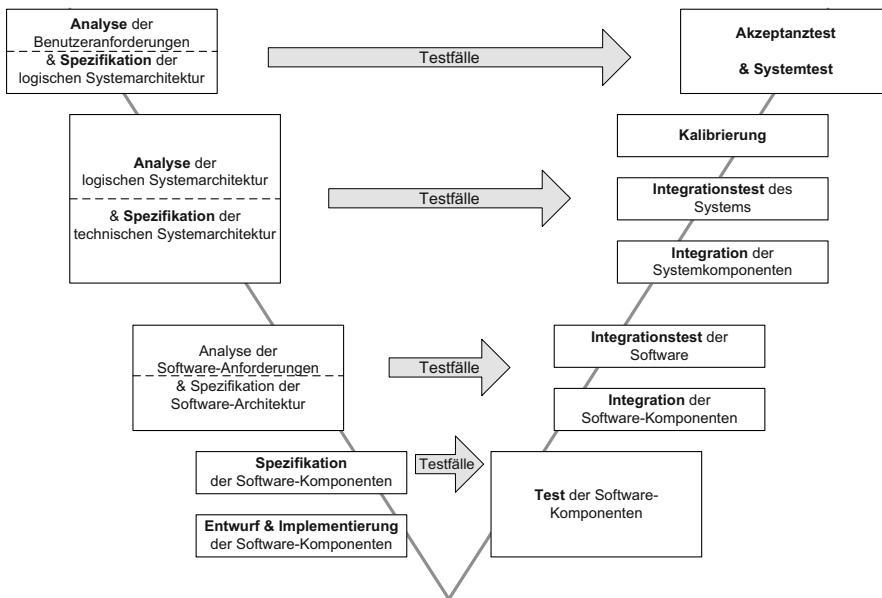

Eine solche Funktions-/Softwarearchitektur ist vergleichbar mit dem AUTOSAR-Modell, bei dem Funktionsblöcke durch sogenannte *Software-Components (SW-Cs)* repräsentiert werden. Allerdings wird hier noch nicht festgelegt, ob ein Funktionsblock in Software auf einer CPU oder in Hardware auf einem ASIC bzw. FPGA ausgeführt wird. Auch die endgültige Verteilung der einzelnen Blöcke auf Steuergeräte spielt beim Aufbau der Funktions-/Softwarearchitektur noch keine Rolle. Vielmehr steht hier die Frage im Vordergrund: Wie wird der Funktionsumfang unterteilt, sodass die einzelnen Funktionsblöcke 1.) wiederverwendbar sind, 2.) nicht zu komplex oder zu feingranular sind und 3.) sinnvoll auf die ECUs verschiedenster Vernetzungsarchitekturen verteilt werden können.

In Abb. 2.4 ist das Funktionsmerkmal *Schiebedach öffnen* des Schiebedaches auf drei Funktionsblöcke aufgeteilt, da das Dach in diesem Fall nur durch die Bedieneinheit geöffnet werden kann. Das Funktionsmerkmal *Schiebedach schließen* kann durch den Funkschlüssel und Regensor ausgelöst werden. Für *Schiebedach schließen* werden also alle Funktionsblöcke benötigt. An die einzelnen Funktionsblöcke können charakteristische Eigenschaften annotiert werden, was in Abb. 2.4 für den Funktionsblock *Dachsteuerung* exemplarisch dargestellt ist. Gleichermaßen gilt für die Verbindungen zwischen den Blöcken, was hier für die Verbindung zwischen *Bedieneinheit für Dach* und *Dachsteuerung* beispielhaft gezeigt ist. Die einzelnen Funktionsblöcke wie *Regenerkennung* oder *Authentifizierung Schlüssels* werden auch für die Realisierung von anderen Funktionen (Ausstattungen) verwendet wie z. B. Scheibenwischersteuerung oder Zutrittsberechtigung zum Fahrzeug. Eine

separate Modellierung ermöglicht also die Wiederverwendbarkeit eines Funktionsblocks in anderen Zusammenhängen.

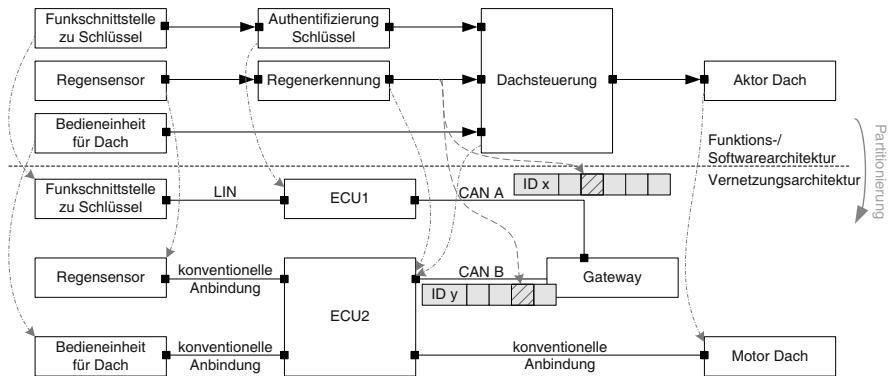

### 2.1.3 Vernetzungsarchitektur

Auf der Ebene der *Vernetzungsarchitektur* werden *Steuergeräte*, *Sensoren* und *Aktoren* betrachtet, die benötigt werden, um die Funktionsblöcke bzw. Software-Komponenten der Funktions-/Softwarearchitektur auszuführen. Weiterhin stehen diese Komponenten für den Austausch von Daten in Verbindung und müssen mit elektrischer Leistung versorgt werden. Aus diesem Grund wird diese Systemebene typischerweise in vier Unterebenen unterteilt: 1.) die Kommunikationsstruktur, 2.) die Leistungsversorgung, 3.) die Komponentenarchitektur und 4.) den Leistungssatz.

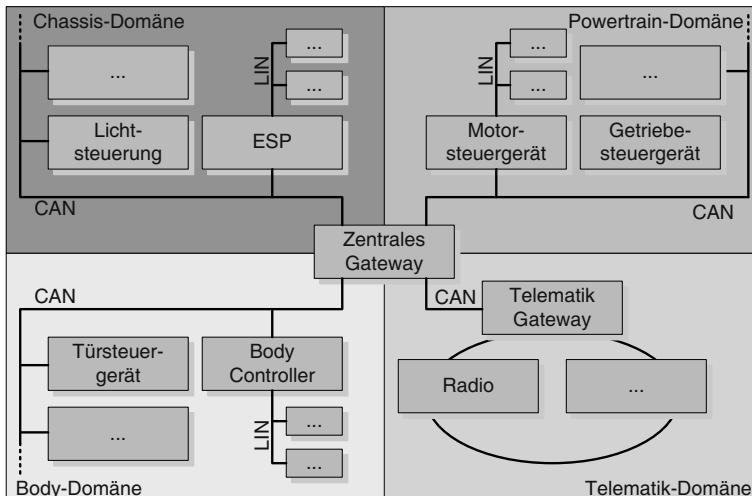

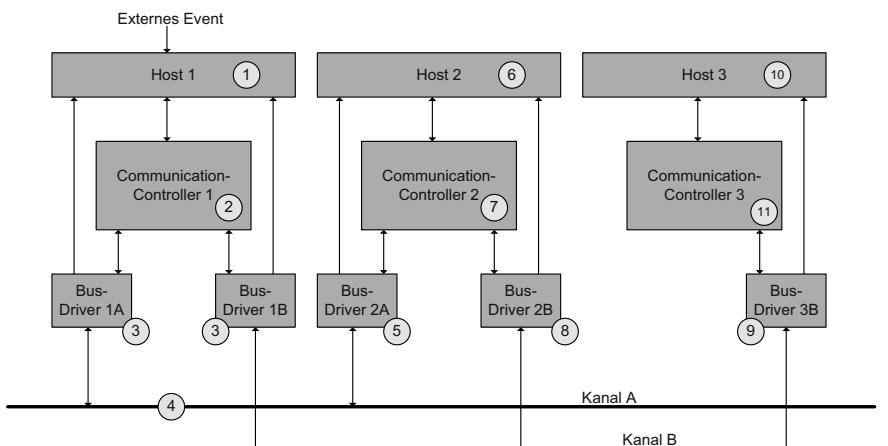

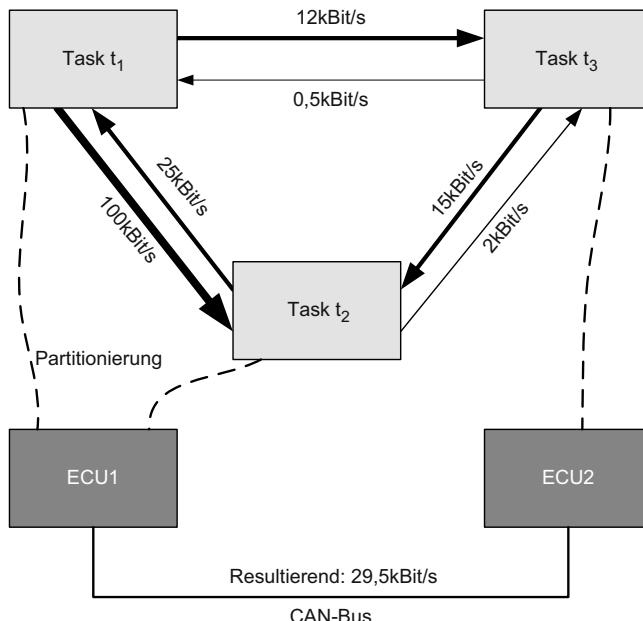

#### Kommunikationsstruktur

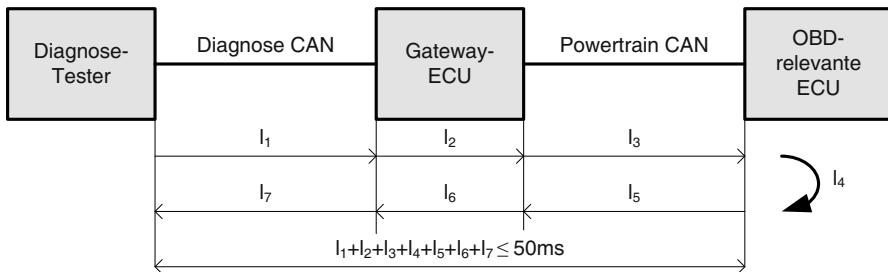

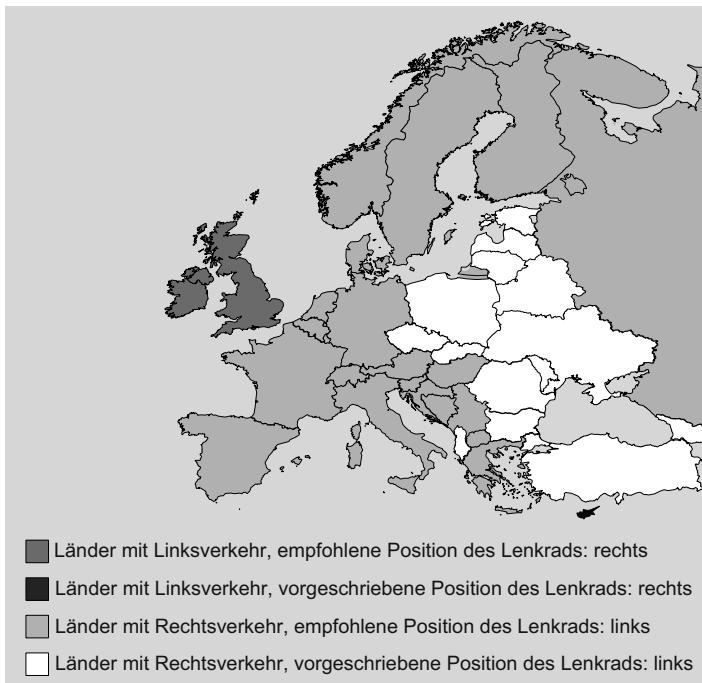

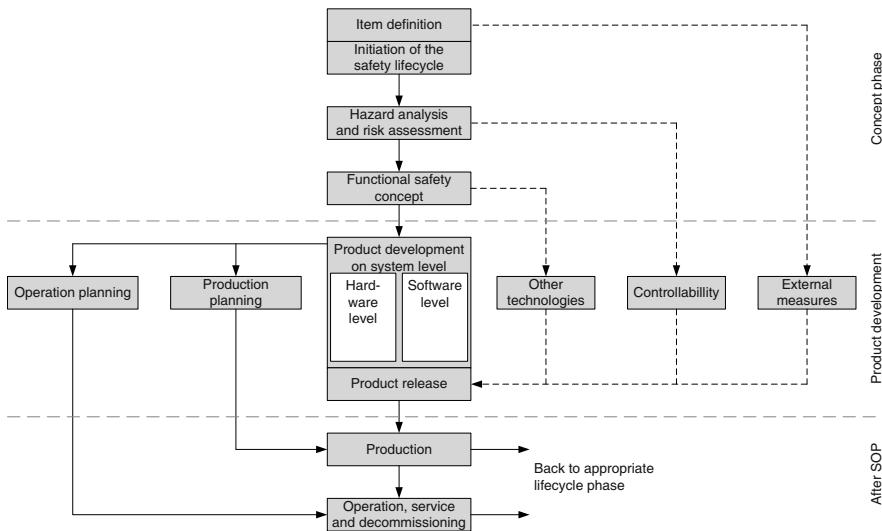

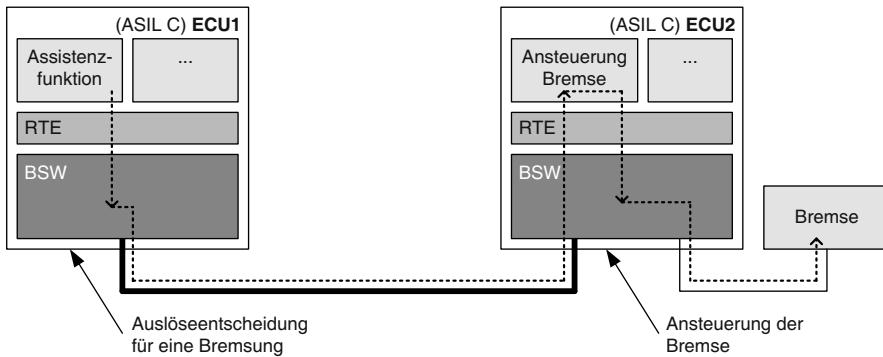

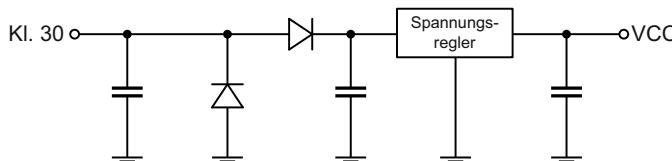

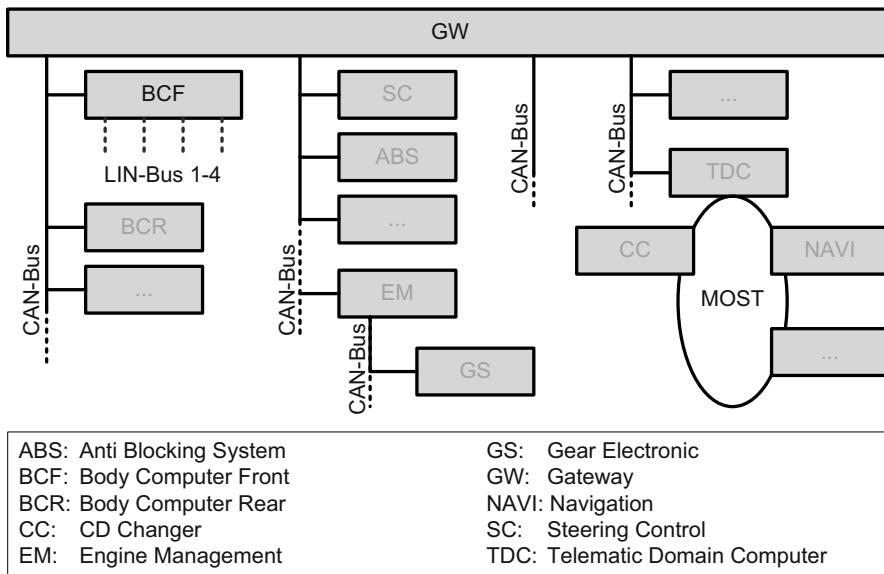

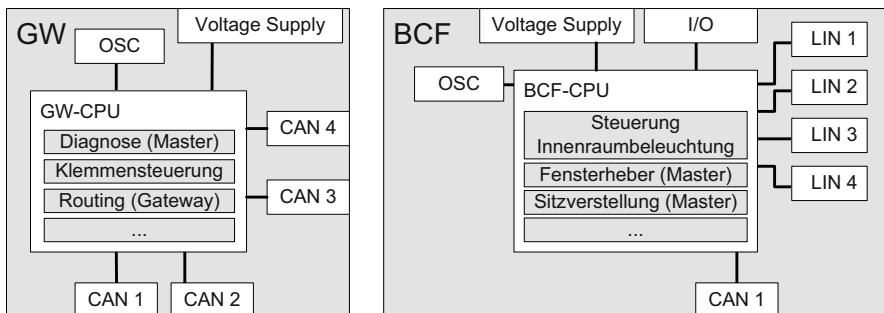

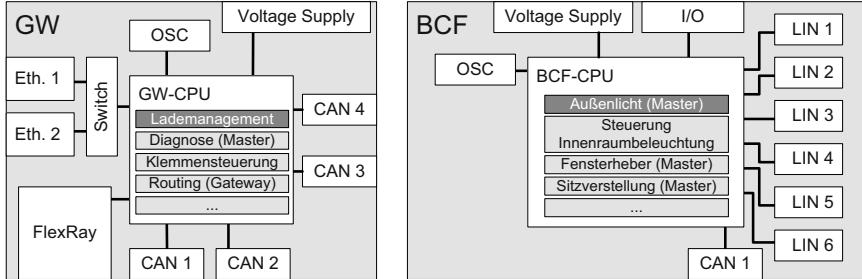

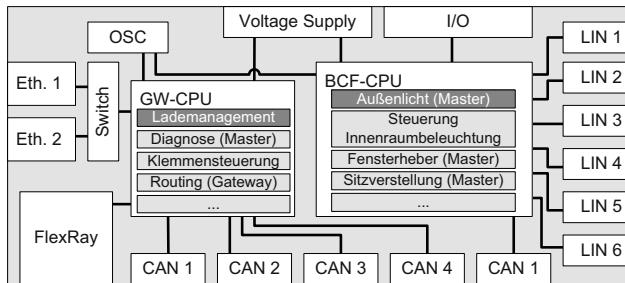

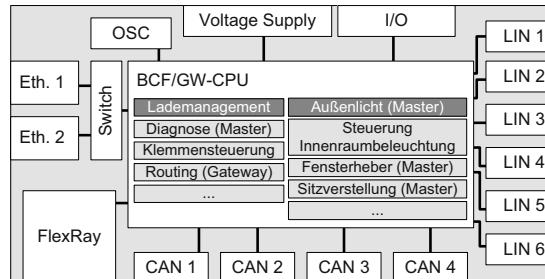

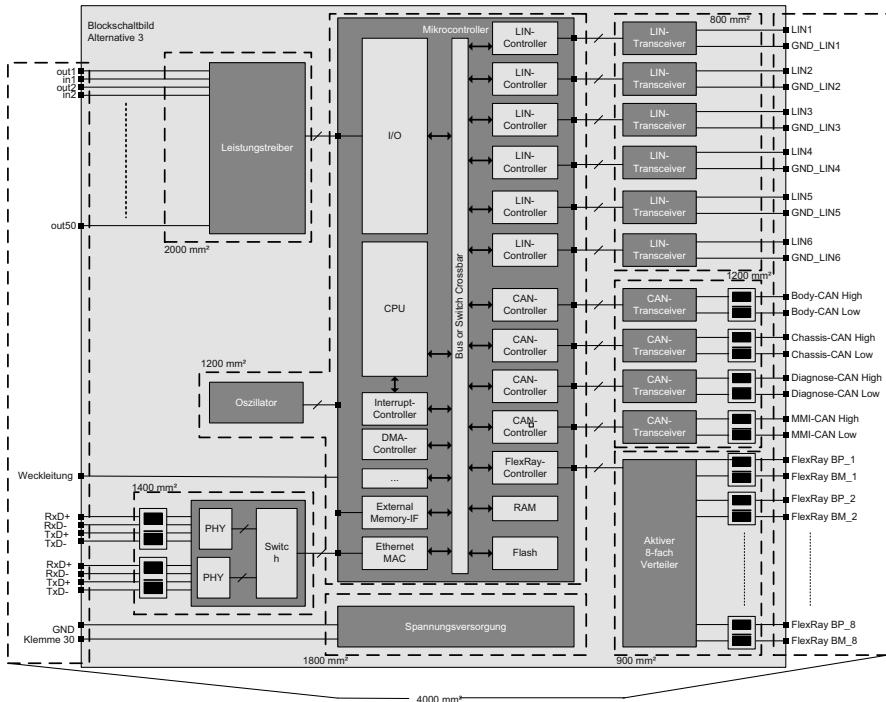

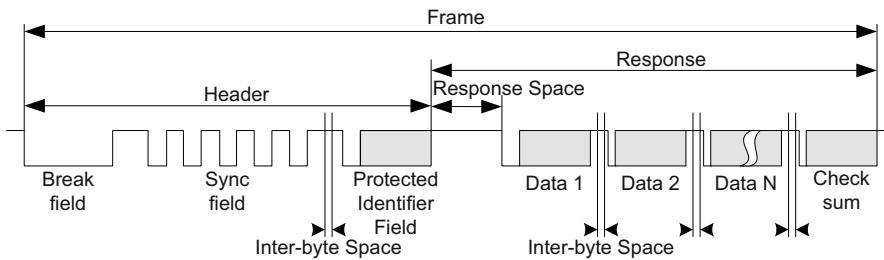

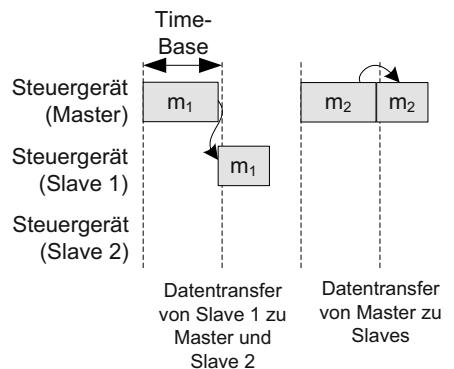

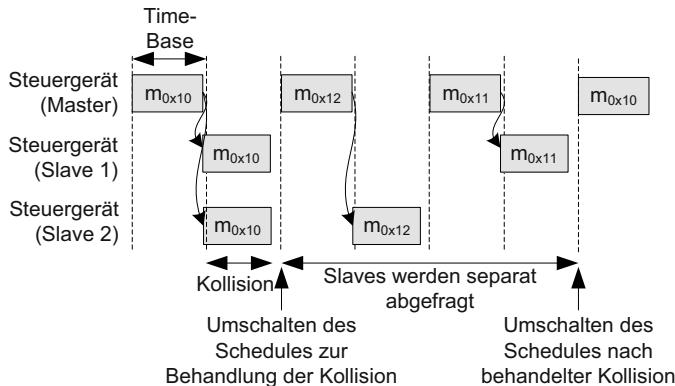

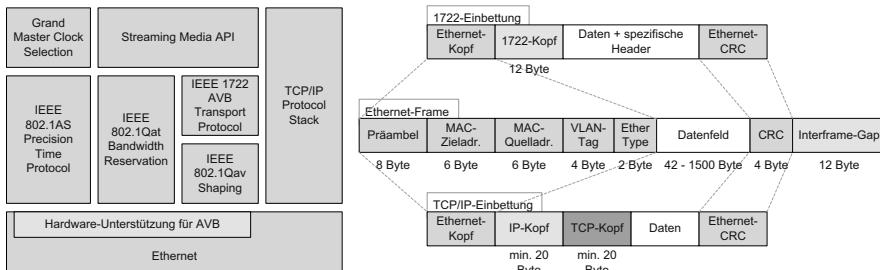

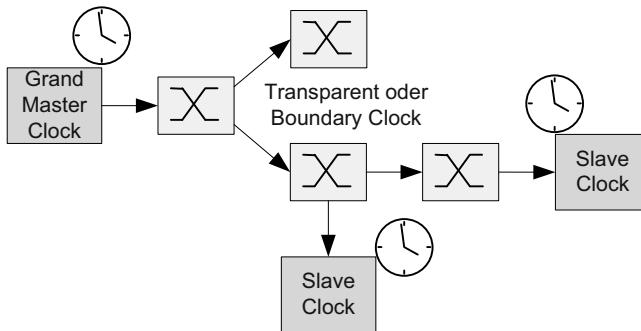

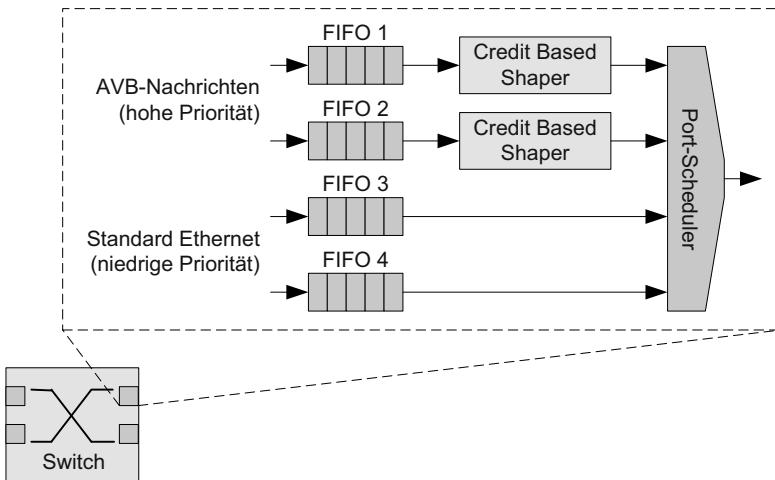

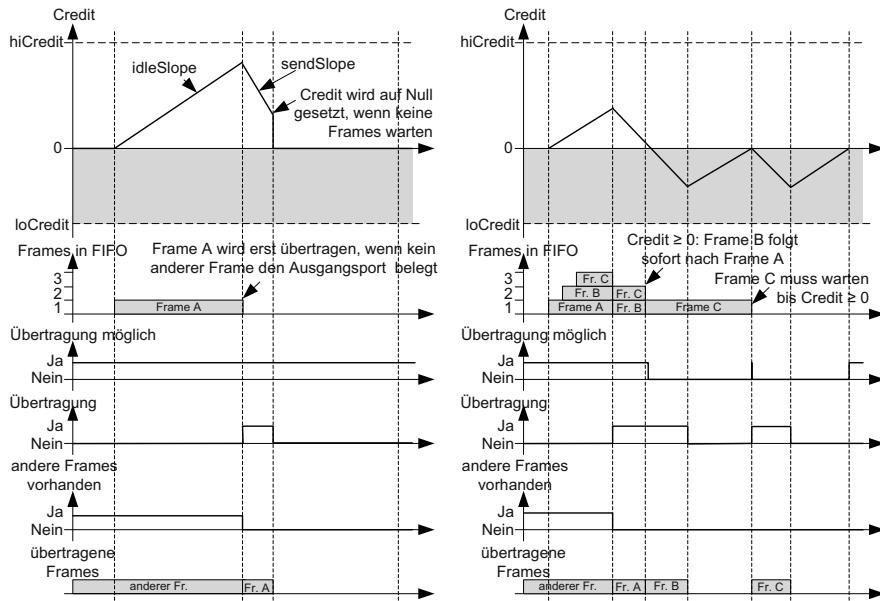

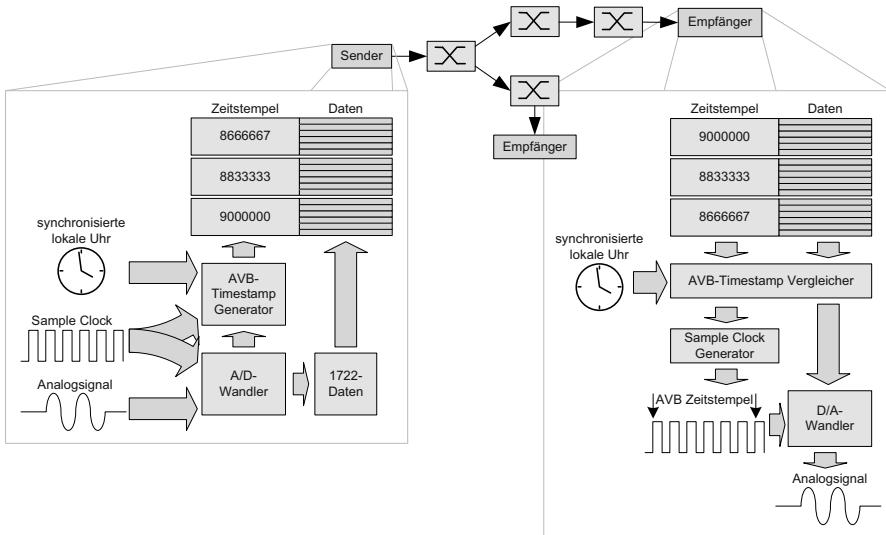

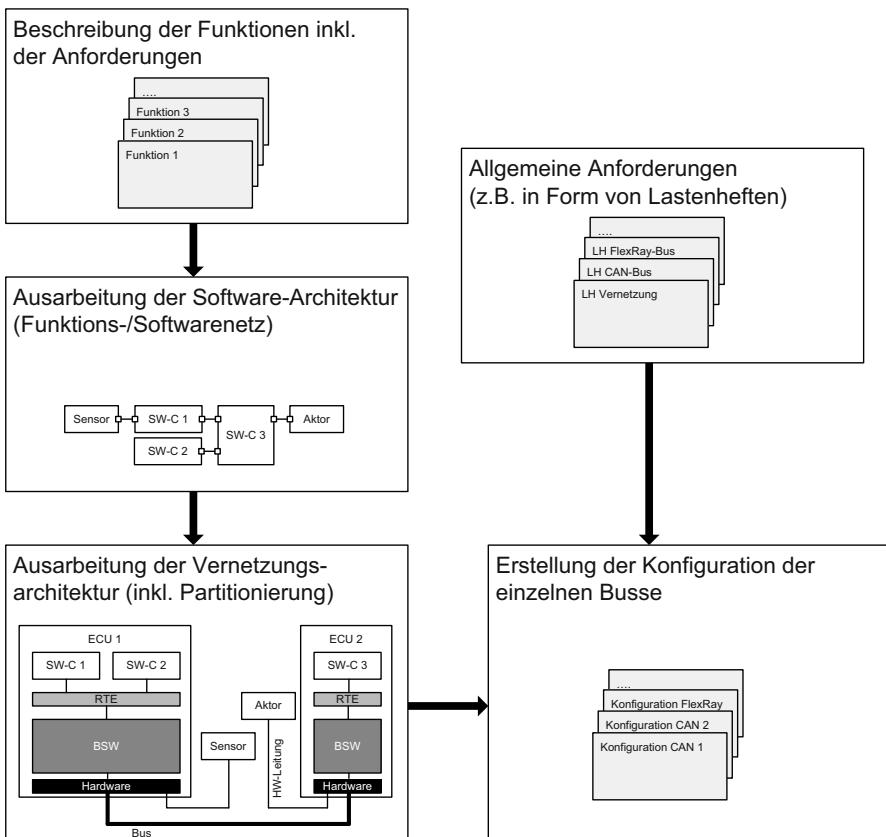

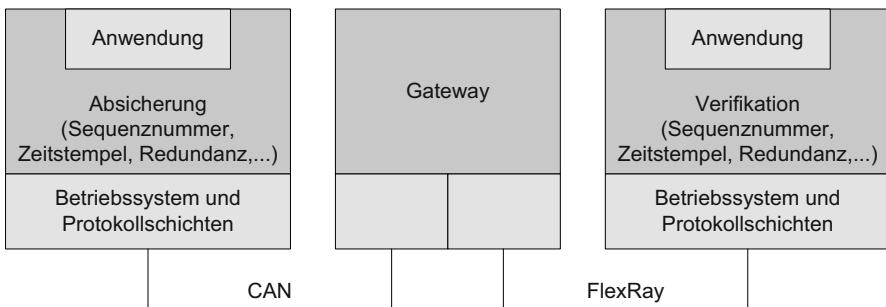

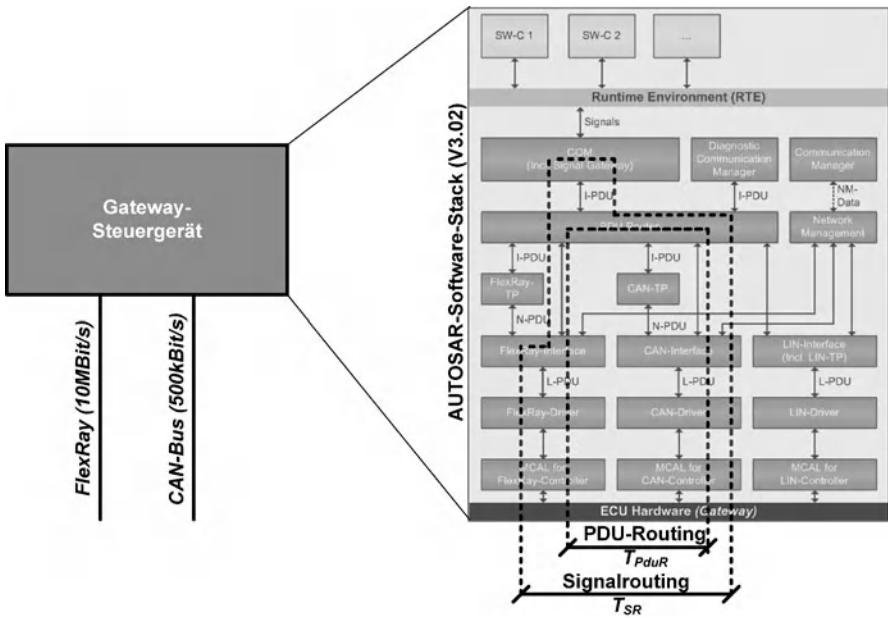

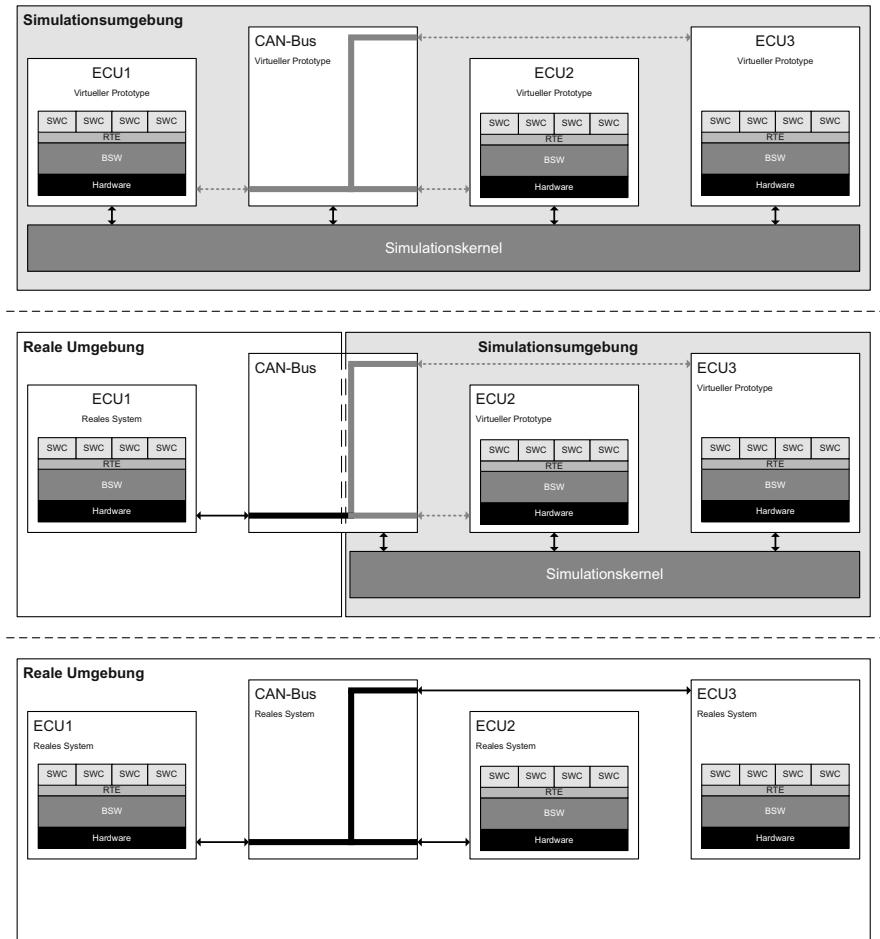

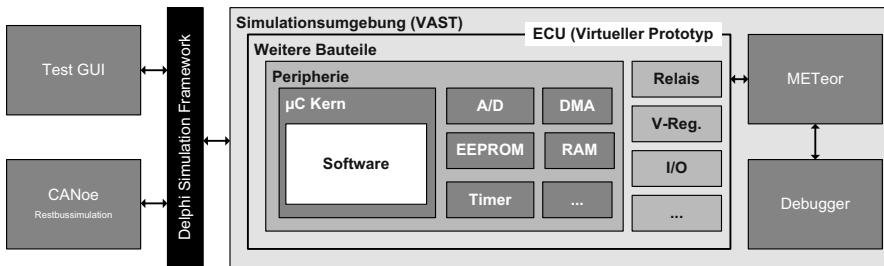

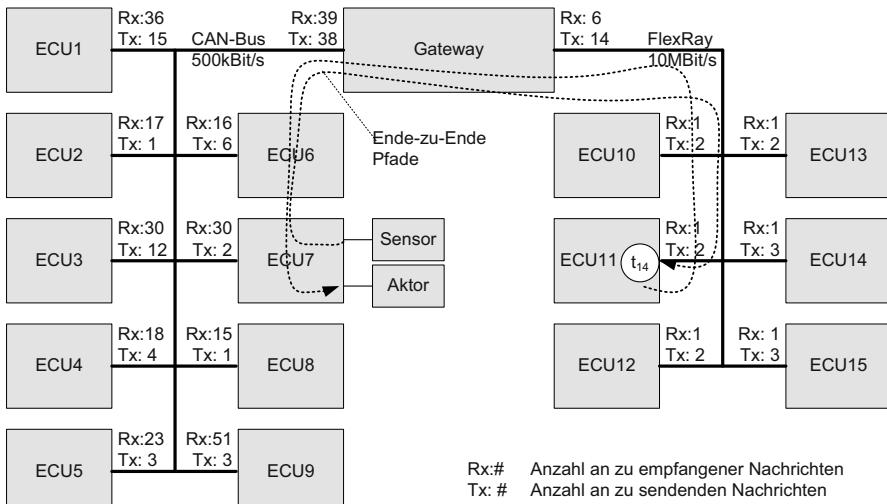

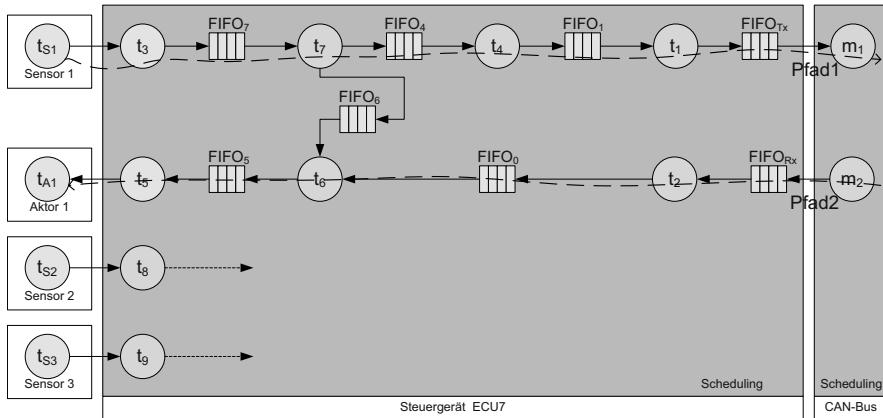

In der Kommunikationsstruktur werden Netzwerke aufgebaut, die aus Komponenten wie Steuergeräten, Sensoren und Aktoren bestehen. Die Kommunikation zwischen diesen Komponenten kann über Busse wie FlexRay, CAN, LIN, MOST, etc. erfolgen oder über dedizierte bzw. proprietäre Anbindungen, wie es zum Beispiel beim Anschluss eines Sensors oder Aktors der Fall sein kann. Sollen verschiedene Kommunikationssysteme oder Stränge eines Busses miteinander verbunden werden, so kann das auf verschiedenen Ebenen des ISO-OSI-Schichtenmodells erfolgen: